дом сумматора, а второй и третий выходы синхронизатора соединены с управляющим вхоцом ключа и вторым входом измерителя, введены аналого-цифровой преобразователь, два комбинационных сумматора, блок памяти блок адресации, регистр, дв блока коррекции, цифроаналоговый преобразователь и сглаживающий фильтр, причем выход измерителя соединен с третьим и четвертым входами сумматора как непосредственно, так и через последовательно включенные аналого-цифровой преобразователь, первый комбинационный сумматор, блок памяти, регистр, первый блок коррекции, второй комбинационный сумматор, цифроаналоговый преобразователь и сглаживающий фильтр соответственно, кроме того, выходы аналого-цифрового преобразователя через второй блок коррекции подключены к другим входам второго комбинационного сумматора, выходы регистра соединены со второй группой входов первого комбинационного : сумматора, а тактирующие входы и входы, установки начальных состояний регистра и обоих блоков коррекции подклю- чены к червертому и пятому выходам синсинхронизатора, шестой выход которого соединен также через адресный блок с адресными входами блока памяти.

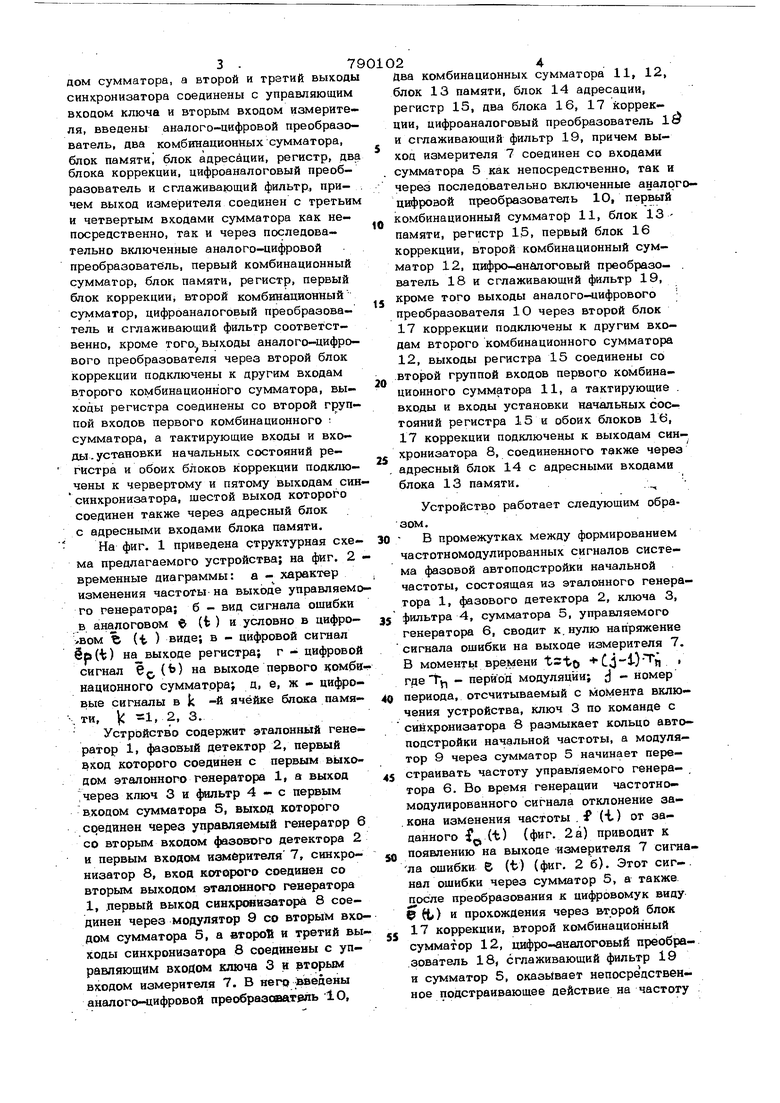

На фиг, 1 приведена структурная схема предлагаемого устройства; на фиг. 2 временные диаграммы: а - характер изменения частоты на выходе управляемого генератора; б - вид сигнала ошибки в аналоговом е (t ) и условно в цифро вом % (t ) виде; в - цифровой сигнал eu(fc) на выходе регистра; г - цифровой сигнал е (Ь) на выходе первого комбинационного сумматора; д, е, ж - цифровые сигналы в k -и ячейке блока памя. ти, Y 1, 2. 3.

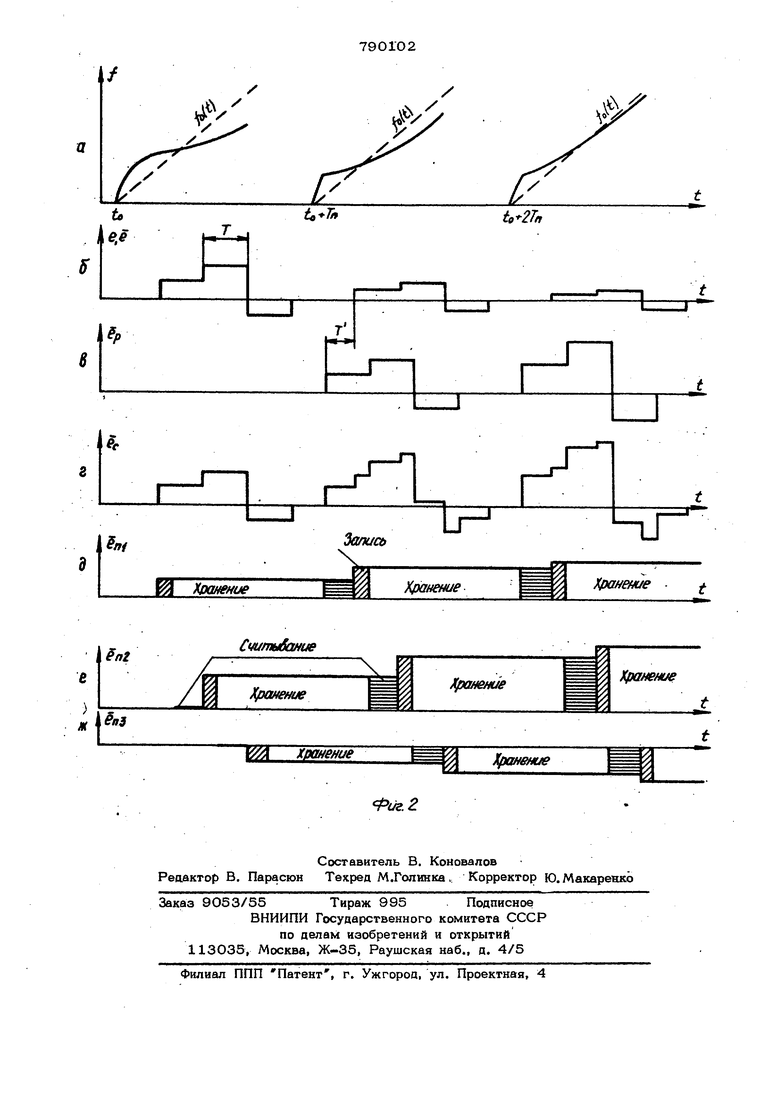

Устройство содержит эталонный генератор 1, фазовый детектор 2, первый вход которого соединен с первым выходом эталонного генератора 1, а выход ; через ключ 3 и фильтр 4 - с первым входом сумматора 5, выход которого соединен через управляемый генератор 6 со вторым входом фазового детектора 2 и первым вкодсял измерителя 7, синхронизатор S, вход которого соединен со вторым выходом эталонного генератора 1, .первый выход синхрсжизатора 8 соединен через модулятор 9 со вторым входом сумматора 5, а аторо1б и третий выходы синхронизатора 8 соединены с управляющим вколом ключа 3 и вторым входом измерителя 7. В него введены аналого-цифровой преобразоватрль 10,

Два комбинационных сумматора 11, 12, блок 13 памяти, блок 14 адресации, регистр 15, два блока 16, 17 коррекции, цифроаналоговый преобразователь id и сглаживающий фильтр 19, причем выход измерителя 7 соединен со входами сумматора 5 как непосредственно, так и через последовательно включенные аналоцифровой преобразователь 10, первый комбинационный сумматор 11, блок 13 памяти, регистр 15, первый блок 16 коррекции, второй комбинационный сумматор 12, цифро-аналоговый преобразователь 18 и сглаживающий фильтр 19, кроме того выходы аналого-цифрового преобразователя 10 через второй блок 17 коррекции подключены к другим входам второго комбинационного сумматора 12, выходы регистра 15 соединены со второй группой входов первого комбинационного сумматора 11, а тактирующие . входы и входы установки начальных состояний регистра 15 и обоих блоков 16, 17 коррекции подключены к выходам синхронизатора 8, соединенного также через адресный блок 14 с адресными входами блока 13 памяти.

Устройство работает следующим образом.

В промежутках между формированием частотномодулированных сигналов система фазовой автоподстройки начальной частоты, состоящая из эталонного генератора 1, фазового детектора 2, ключа 3, фильтра 4, сумматора 5, управляемого генератора 6, сводит к, нулю напряжение сигнала ошибки на выходе измерителя 7. В моменты времени tst Cj-i) где TY, - период модуляции; jj - номер периода, отсчитываемый с момента включения устройства, ключ 3 по команде с сийхронизатора 8 размыкает кольцо автоподстройки начальной частоты, а модулятор 9 через сумматор 5 начинает перестраивать частоту управляемого генератора 6. Во время генерации частотномодулированного сигнала отклонение за.кона изменения частоты . f (i,) от заданного (t) (фиг. 2а) приводит к появлению на выходе измерителя 7 сигнала сйшибки е (t) (фиг. 2 б). Этот сигнал ошибки через сумматор 5, а также после преобразования к цифровомук виду е И) и прохождения через второй блок 17 коррекции, второй комбинационный сумматор 12, цифро-аналоговый преобра.зователь 18, сглаживающий фильтр 19 и сумматор S, оказывает непосредственное подстраивающее действие на частоту управляемого генератора 6. Помимо непосредственного воздействия на часто ту управляемого генератора 6 сва:нап. ошибки в цифровой Ь (t) форме испол зуется для формирования компенсирующе- го напряжений, подаваемого ко входу управляемого генератора 6 в последующих периодах модуляции. Возможность применения такого компенсирующего напряжени основьшается на том, что ошибки в частотномодулированных генераторам -в среднем от одного периода к другому практически постоянны. Основным бло- .ком, участвующим в формировании компенсирующего напряжения, является блок 13 памяти, каждая ячейка которого заменяет один из интеграторов, имеющихся в известном устройстве. Ячейки блока 13 памяти в момент включения устройства могут быть либо обнулены, либо содержать априорную информацию о характере компенсирующего напряжения, полученную по результатам предварительного измерения нелинейности модуляционной характеристики управляемого генера- тора 6 или на основании предыдущих включений устройства. Рассмотрим процесс формирования компенсирующего напряжения в -м после включения устройства периоде модуляции. Во временных интервалах. ., гдет,/Т; - 1.2. 3 ... - номер ячейки блока 13 памяти, числовая информация k,,k из V -и ячейки блока 13 памяти переписываются в регистр 15 (фиг. 2 а), в котором она хранится в течение времени Т, определяемом периодом дискретизации сигнала ошибки. Запись новых чисел (фиг. 2 д ), представляющих собой сумму % (фиг. 2 г) чисел е и §р 1 с выходов аналого цифрового преобразователя 10 (фиг. 26) й-регистра 15 (фиг. 2 в) в |d -) ячейку блока 13 памяти осуществляется во временных интервалах . Ito (i- rгn,t (knVr-T4d-i)Tn, показанных на фиг. 2 д-ж косой штрихов кой. Сформированное на основании измере ний сигнала ошибки в предыдущих перио дах модуляции и содержащееся в регистре 15-напрйжение . где I - 1,2,3 ... -1, после прохождения первого блока 16 коррекции, второго комбинационного сумматора 12, цифро-аналогового преобразователя 18, сглаживающего фильтра 19 н сумматора 5 осуществляет компенсацию присущих управляемому генератору 6 и модулятору9 ошибок, повторяющихся от одного периода модуляции к другому. Входящие в устройство блоки 16 и 17 коррекции обеспечивают требуемые .динамические характеристики. Использование этих цифровых блоков позволяет реализовать желаемый коэффициент передачи для напряжений в и 6р с высокой степенью точности. Формулаизобретения. Устройство прецизионного формирования повторяющихся частотномодулированных сигналов содержащее эталонный генератор, фазовый детектор, первый вход которого соединен с первым выходом эталонного генератора, а выход че-рез ключ и фильтр с первым входом сумматора, выход которого соединен через управляемый генератор со вторым входом фазового детектора и первым входом измерителя, синхронизатор, вход которого соединен со вторым выходом эталонного генератора, первый выход синхронизатора соединен через модулятор Со вторым входом сумматора, а второй и третий выходы синхронизатора соединены с управляющим входом ключа и вторым входом измерителя, отличающееся тем, что, с целью пов1ь1Ш ния точности Инадежности, в него введены аналого-цифровой преобразователь, два комбинационных сумматора, блок памяти, блок адресации, регистр, два блока коррекции, цифро-аналоговый преобразователь и сглаживающий фильтр, причем выход измерителя соединен с третьим и четвертым входами сумматора как непосредственно, так и через последовательно включенные аналого-иифровой преобразователь, первый комбинационный сумматор, блок памяти, регистр, первый блрк коррекции, второй комбинационный сумматор, цвфро- аналоговый преобразователь и сглаживающий фильтр, соответственно, кроме то- rOj выходы аналого-цифрового преобразователя через второй блок коррекции пой- ключены к другим входам второго icOMбинационного сумматора, выходы регистра соединены с другими входами первого комбинационного сумматора, а тактирующие входы и входы установки начальник состояний регистра в .блоков коррекции. подключены к четвертому и пятому выходам синхрсжизатора, шестой выход ко7 .7901028

торого соединен через адресный блок с1. Авторское свидетельство СССР

адресными входами блока памяти.№ 526997; кл. Н 03 В 3/04, 1976.

Источники информации,2. Патент США № 3.899.448,

принятые во внимание при экспертизекл. 252-551, 1972.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство формирования частотно- модулированных сигналов | 1979 |

|

SU792528A1 |

| УСТРОЙСТВО ДЛЯ КЛАССИФИКАЦИИ ПОСЛЕДОВАТЕЛЬНОСТИ ЦИФРОВЫХ СИГНАЛОВ | 2010 |

|

RU2453915C1 |

| Ультразвуковое устройство для измерения контактных давлений | 1990 |

|

SU1746297A1 |

| Устройство формирования сигнала для коррекции искажений телевизионного изображения | 1985 |

|

SU1317687A2 |

| Формирователь повторяющихся частотно-модулированных сигналов | 1988 |

|

SU1555806A1 |

| Формирователь повторяющихся частотно-модулированных сигналов | 1982 |

|

SU1084940A1 |

| Устройство для контроля радиоэлектронных объектов | 1990 |

|

SU1714622A1 |

| Цифровой измеритель задержки | 1980 |

|

SU930219A2 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ РАДИОТЕЛЕМЕТРИЧЕСКИХ СИГНАЛОВ | 1994 |

|

RU2126139C1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1985 |

|

SU1305851A1 |

Pi/e.f

t

е.ё

Авторы

Даты

1980-12-23—Публикация

1979-02-19—Подача