Изобретение отосится к импульсной технике и может быть использовано в цифровых вычислительных машинах, цифровых измерительных приборах и в цифровых преобразователях.

Известны устройства синхронизации, содержащее триггеры, элементы совпадения и инверторы 1.

Недостаток известных устройств - низкая точность измерения..

Из известных устройств наиболее близким по технической сущности к предложенному является устройство тактовой синхронизации, содержащее запоминающий и управляющий триггеры, два злемента И-НЕ, инвертор и логический формирователь импульсов 2.

Недостатками известного устройства тактовой сиихронизации являются низкое быстродействие и низкая точность синхронизации.

Цель изобретения - повышение; быстродействия и точности синхронизации устройства.

Поставленная цель достигается тем, что в устройство синхронизации, содержащее последовательно соединенные запоминающий и управляющий трштеры и первый элемент И-НЕ,

последовательно соединенные инвертор и второй элемент И-НЕ, второй вход которого подключен к инверсному выходу запоминающего триггера, а выход второго элемента И-НЕ соединен с нулевым входом управляющего триггера, а также логический формирователь импульсов, тактовый вход которого соединен со вторым входом первого элемента И-НЕ и с щиной тактовых импульсов введены два дополнительных триггера, два дополнительных элемента И-НЕ

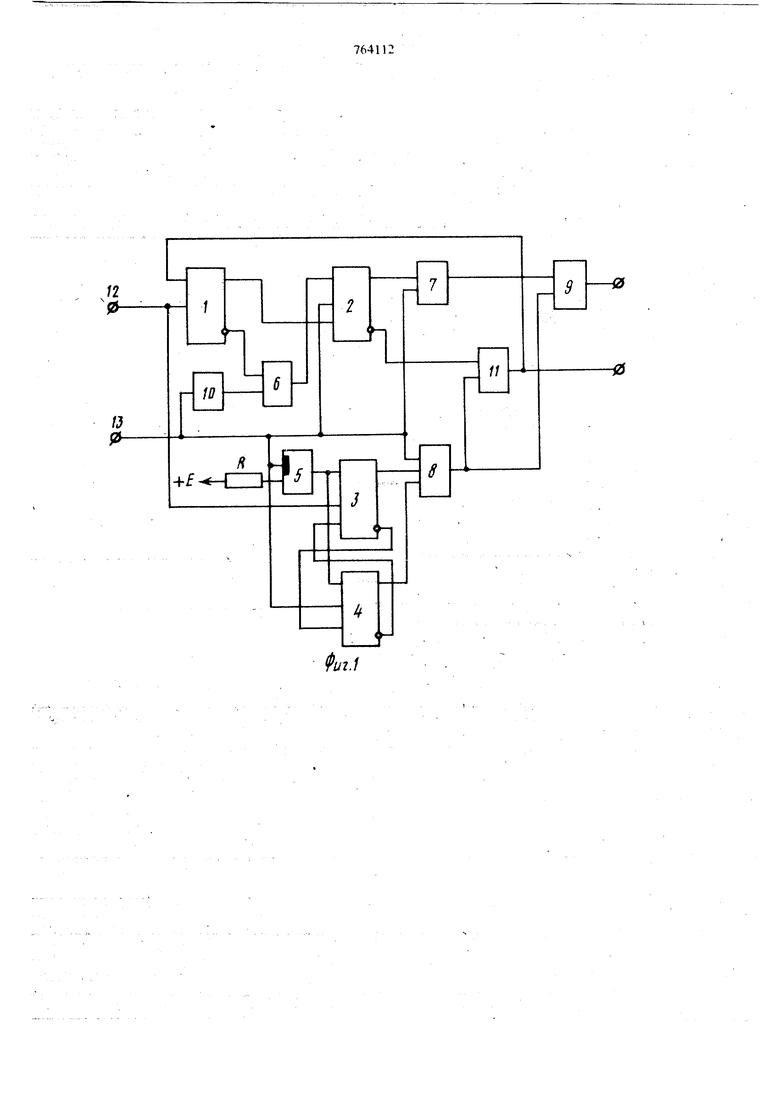

10 и элемент И, первый вход которого соединен с инверсным выходом управляющего триггера, второй вход элемента И соединен с выходом первого дополнительного элемента И-НЕ и с первым входом второго дополнительного эле15мента И-НЕ, первый вход первого дополнительного элемента И-НЕ подключен к тактовому входу логического формирователя, а второй И третий входы первого дополнительного элемента И-НЕ соединены с прямыми выхода20ми первого и второго дополнительных триггеров, при этом нулевые входы дополнительных триггеров соединены с выходом логического формирователя импульсов, инверсные вы376ХОДЫ первого и второго ;юпот1ительных триггеров соедт ены с информаодонными входами второго и первого дополнительных триггеров соответственно, синхровходы первого и второfO rt6nbJtHHte7ibHbtx тригге ров подключены к шине управляющих импульсов и к тине тактовых нмЛульсов соответственно, выход элемента И соединен с нулевым входом запоминающего триггера, второй вход второго дополнительного элемента И-НЕ соединен с выходом первого элемента И-НЕ, а вход инвертора подключен к шине тактовых импульсов. . На фиг. 1 приведена структурная схема устройства тактовой синхронизации; на фиг. 2 эпюры напряжений, иллюстрирующие формирование выходных импульсов. Устройство тактовой синхронизации содержит запоминающий триггер 1, управляющий триггер 2, дoпoJffiитeльныe триггеры 3 и 4, логический формирователь 5 импульсов, элементы И-Н 6-9, инвертор 10, элемент И 11, щину 12 упра ляющих импульсов и шину 13 тактовых импул сов, тактовый вход запоминающего триггера по соединен к щине управляющих импульсов, а синхррвход управляющего триггера подсоедииен к шине тактовых импульсов. Устройство тактовой синхронизации работает следующим образом.. В исходном положении все триггеры устройства находятся в нулевом состоянии. На шине 1 i уп||11ЙяШЩйх ймпуль:сОв присутствует низкий потенциал. Элементы И-НЕ 7 и 8 закрыты (на их выходах поддерживае:тся высокий потенциал), а элемент И-НЕ открыт (на.его выходе поддерживается низкий потенциал). На выходе логического элемента И 11 присутствует высокий потенциал. Присутствие тактовых импульсов на шине 13 (фиг. 2, а) изменяет лишь состояние триггера 4. / При появлении управляющего сигнала (положительный импульс - фиг. 2, 6) перепадом от низкого потенциала к высокому триггер 1 переходит в единичное состояние (фиг. 2, в). Триггер 3 не изменяет своего состояния, так как на синхровход триггера 4 раньше поступил тактовый импульс и триггер 4 перешел в единичное состояние (фиг. 2, г). Потенцй1ап, соответствующий логическому О, с инверсного выхода триггера 4 поступает на информационный вход триггера 3, и приход управляющего импульса на информационный вход последнего подтверждает его нулевое состояние. ПоявленйТ тактового импульса вызывает переключение инвертора 10. С установкой триггера 1 в единичное Состояние на инверсном выходе последнего устанавливается низкий потенциал, что Тп|5йвЪД1т появлению на выходе элемента И-НЕ 6 BbicoKoroi потенциала (фиг. 2, д). Триггер 2 йе удерживается принудительно в нулевом состоянии низким ютсн Ц1алом. Высо кий потенциал с прямого выхода триггера 1 подается на информаниоиньгй вход триггера 2. С прихбдом следующего ближайшего тактового импульса насинхронход триггера 2 гкхледний переходит в единичное состояние (фиг. 2, е). На прямом выходе триггера 2 появляется высокий потенциал, открывающий элемент И-НЕ,7 по первому входу. На выходе последнего появляется отрицательный импульс (фиг. 2, ж), так как на втором входе элемента И-НЕ 7 присутствует положительный тактовый импульс. Низкий потенциал с выхода элемента И-НЕ 7 поступает на вход элемента И-НЕ 9 и на выходе последнего появляется положительный импульс (фиг. 2, з), по длительности и моменту совпадающий с тактовым импульсом. С установкой триггера 2 в единичное состояние низкий потенциал с его инверсного выхода поступает на вход элемента И 11 и на выходе последнего формируется отрицательный имПульс, по длительности и моменту совпадающий с тактовым импульсом (фиг. 2, и), который поступает на инверсный выход устройства и на нулевой вход триггера 1, устанавливая его в нулевое состояние. Потенциал на его. нулевом выходе становится высоким. По окончании тактового импульса потенциал на выходе инвертора 10 также становится высоким, что, в свою очередь, приводит к появлению низкого потенциала на выходе элемента И-НЕ 6, которым триггер 2 устанавливается в нулевое состояние. Таким образом, устройство тактовой сийхронизации возвращается в исходное положение. В моменты времени, когда управляющий и тактовый импульсы не совпадают во времени по переднему фронту (на фиг. 2-мрменты времени ti, ta) устройство тактовой синхронизации работает аналогичным образом. fticcMOTpMM работу ; устройства; при совпадении по переднему фронту управляющих и тактовых импульсов (на фиг. 2 - момент времени tj). В этом случае при одновременном поступлении на синхровходы триггеров 3 и 4 управляющих и тактовь1Х импульсов последние переходят в единичные состояния, так как на их информационных входах до этого момента присутствовал потенциал, соответствующий логической 1 (фиг. 2, г, к). Триггер I управ.ляющим импульсом также переводится в единичное состояние. Теперь на всех входах элемента И-НЕ 8 имеются высокие потенциалы, что вызыва ет его переключение, т.е. на выходе элемента И-НЕ 8 устанавливается низкий потенциал (фиг. 2, л.). Отрицательнь1Й. импульс с выхода элемента И-НЕ 8 поступает на входы элемента И 11 и элемента .И-НЕ 9. На элемента И 1Г формируется также отрицатель576ный импульс, который гкктупает на нулевой вход фиггера 1, возвращая его тем самым в нулевое состояние, а с поступлением отрицатель ного импульса на вход элемента И-НЕ 9 на вы ходе последнего формируется положительный импульс, синхронный с импульсом тактовой частоты, длительностью, равной длительности импульса тактовой частоты. По заднему фронту этого же тактового импульса на выходе формирователя формируется короткий отрицательный импульс (фиг. 2, м), которым триггеры 3 и 4 устанавливаются в нулевое состояние. Таким образом, устройство тактовой синхронизации возвращается в исходное положение Соедине1 ие прямого выхода запоми11ающего триггера с информационным входом управляющего триггера, синхровход которого подключен к щине тактовых импульсов, и соединение инверсного выхода управляющего триггера с од ним из входов элемента И, в ыход которого со единен с нулевым входом запоминающего триггера, позволило повысить быстродейстиве устройства. Так, в прототипе импульс на выходе появляется через время At + Т после поступления управляющего импульса, где Т - период следования тактовых импуль сов; At - время от момента поступления управляющего импульса до момента поступления, ближайшего тактового импульса (см. фиг. 4, а). Таким образом, в известном устройстве тактовой синхронизации задержка составляет ut-hT. . В предлагаемом устройстве быстродействие повысилось в , раза. В этом случае р- uttT ,Т-УТ 1 - ргп . т - т.е.-быстродействие повысилось в 2 раза. Введение двух допО11Нительных триггеров, ло гического элемента И и двух логических элементов И-НЕ позволило повысить точность синхронизации, так как при совпадении во времени передних фронтов управляющих и тактовых импульсов на выходе устройства сразу же формируется выходной импульс, синхронный с импульсом тактовой частоты. Формула изобретения Устройство тактовой синхронизации, содержащее последовательно соединенные запоминающий и управляющий триггеры и первый эле мент И-НЕ, последовате;1ьно соединенные инвер тор и второй элемент И-НЕ, второй вход которого подключен к инверсному выходу запоминающего триггера, а выход второго элемента И-НЕ соединен с нулевым входом угфавляющего триггера, а также логический формирователь импульсов, так:товый вход которого соединен с вторым входом первого элемента И-НЕ и с щиной тактовых импульсов, отличающееся тем, что, с целью-повышения быстродействия и точности синхронизации, в него введены два дополнительных триггера, два дополнительных элемента И-НЕ и элемент И, первый вход которого соединен с инве|хным выходом управляющего триггера, второй вход элемента И соединен с выходом первого дополнительного элемента И-НЕ и с первЕ 1м рходом второго дополнительного элемента И-НЕ, первьш вход первого дополнительного элемента И-НЕ подключен к тактовому входу логического формирователя, а второй и третий Bxo/ibi первого дополнительного элемента И-НЕ соединены с прямыми выходами первого и второго дополнительных триггеров, при этом нулевые входы дополнительных триггеров сое;линены с выходом логического формирователя импульсов, инверсные выходы первого ивторого дополнительных триггеров соединены с информационными входами второго и первого дополнительных триггеров соответственно, синхровходы первого и -второго дополнительных триггеров подключены к шине управляющих импульсов и к щине тактовых импульсов соответственно, выход элемента И соединен с нулевым входом запоминающего триггера, второй вход второго дополнительного элемента И-НЕ соединен с выходом первого элемента И-НЕ, а вход инвертора подключен к щине тактовых импульсов, тактовый вход запоминающего триггера подсоединен к щине управляющих импульсов, а синхровход управляющего триггера подсоединен к щине тактовь1Х импульсов. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР N 478429, кл. Н 03. К 5/13, 1975 2.Авторское свидетельство СССР № 453791, кл. Н. 03 К 5/153, 1974 (прототип).

12 0

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1104590A1 |

| Устройство тактовой синхронизации | 1978 |

|

SU748839A1 |

| Мажоритарное декодирующее устройство | 1986 |

|

SU1372627A1 |

| Счетное устройство | 1987 |

|

SU1492473A1 |

| Формирователь тестов | 1985 |

|

SU1259271A1 |

| Формирователь импульсов | 1982 |

|

SU1050102A1 |

| Нанопрограммное устройство управления | 1983 |

|

SU1136160A1 |

| Устройство для измерения рассогласования между углом и кодом | 1987 |

|

SU1411973A1 |

| Формирователь длительности импульсов | 1984 |

|

SU1213525A1 |

| Мажоритарное декодирующее устройство | 1987 |

|

SU1471313A1 |

/J P-hf

Авторы

Даты

1980-09-15—Публикация

1978-07-24—Подача