20 121

Фиг.1

Изобретение относится к вычиспитель- ной технике и технике связи и может быть использовано в сетях ЭВМ и каналах связи дискретных систем передачи информации, на внутренней ступени которых применяются многопозиционные сигналы.

Цель изобретения - повышение помехоустойчивости.

На фиг.1 изображена блок-схема декодера; на фиг.2 - блок-схема анализатора проверок; на фиг.З - блок-схема блока управления; на фиг,4-блок-схема формирователя синдрома; на фиг.5 - блок-схема блока выбора минимума; на фиг.6 - временные диаграммы сигналов, поясняющие работу декодера.

Пороговый декодер q-ичного кода содержит формирователь 1 синдрома, формирователь 2 проверок, регистр 3 данных, первый-четвертый коммутаторы 4-7, регистр 8 надежностей символов, блок 9 выбора минимума, регистр 10 надежностей проверок, анализатор 11 проверок, блок 12 вычитания, первый-третий блоки 13-15 сравнения, сумматор 16 по модулю q и блок 17 управления. На фиг.1 обозначены первые 18 и вторые 19 информационные входы, тактовый вход 20 и вход 21 синхронизации.

Анализатор 11 проверок для случая четырех входных символов содержит (фиг.2) блок 22 вычисления суммы надежностей одинаковых символов, блок 23 дешифрации нулевых символов, блок 24 выбора максимума, группу 25 коммутаторов, первый-третий мультиплексоры 26-28 и группу 29 элементов сравнения. На фиг.2 обозначены первые 30 и вторые 31 входы и первые-четвертые выходы 32-35.

Входящий в состав анализатора 11 блок 22 вычисления суммы надежностей одинаковых символов содержит (фиг.2) мультиплексоры 36, двоичные счетчики 37, элементы 38 сравнения, сумматоры 39 и элементы И 40.

Блок 23 дешифрации нулевых символов, также входящий в анализатор 11, выполнен (фиг,2) на дешифраторах 41 нуля и элементах И 42.

Блок 17 управления содержит (фиг.З) первый-четвертый двоичные счетчики 43- 46, первый-третий источники 47-49 постоянного кода и делитель 50 частоты. На фиг.З обозначены вход 51 синхронизации, тактовый вход 52, первый-пятые выходы 53-57.

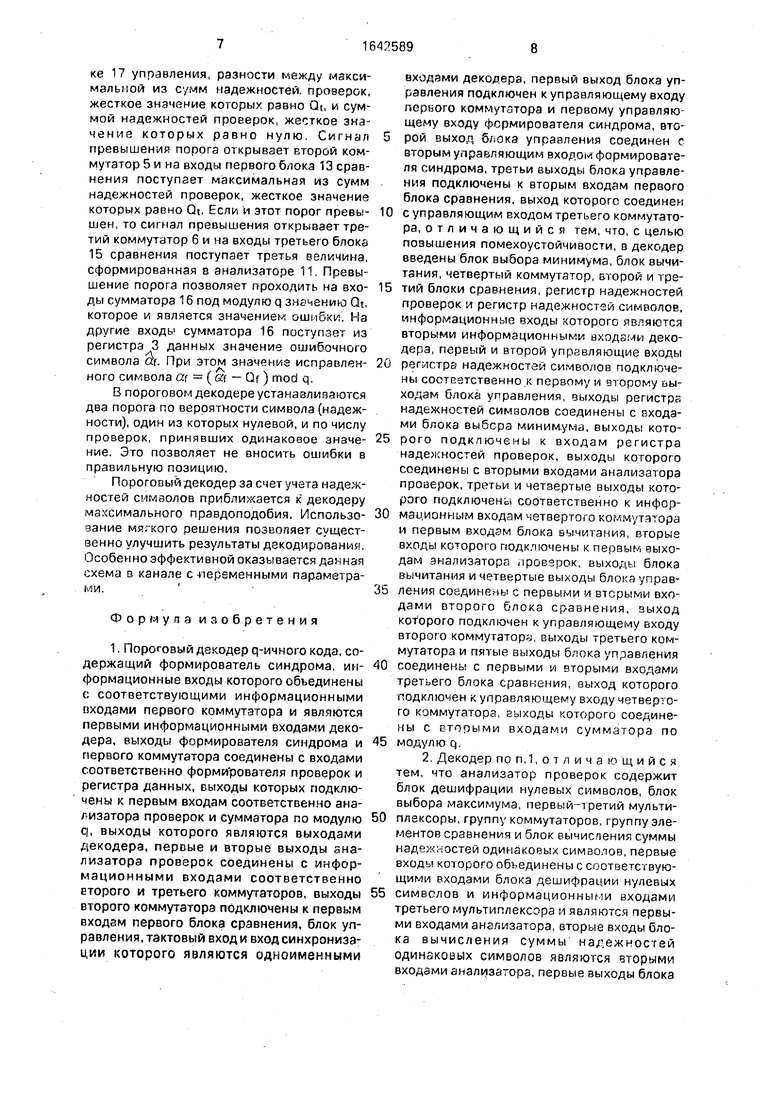

Формирователь 1 синдрома выполнен в соответствии с используемым кодом (фиг,4) на регистрах 58-61. коммутаторах 62 и 63 и сумматоре 64 по модулю q.

Регистр 8 надежностей символов выполнен так же, как и формирователь 1 синдрома, за исключением сумматора 64 по модулю q, а выходы регистров 58-61 соединены с блоком 9.

Формирователь 2 проверок реализуется в соответствии с проверочной матрицей выбранного кода на сумматорах по модулю q.

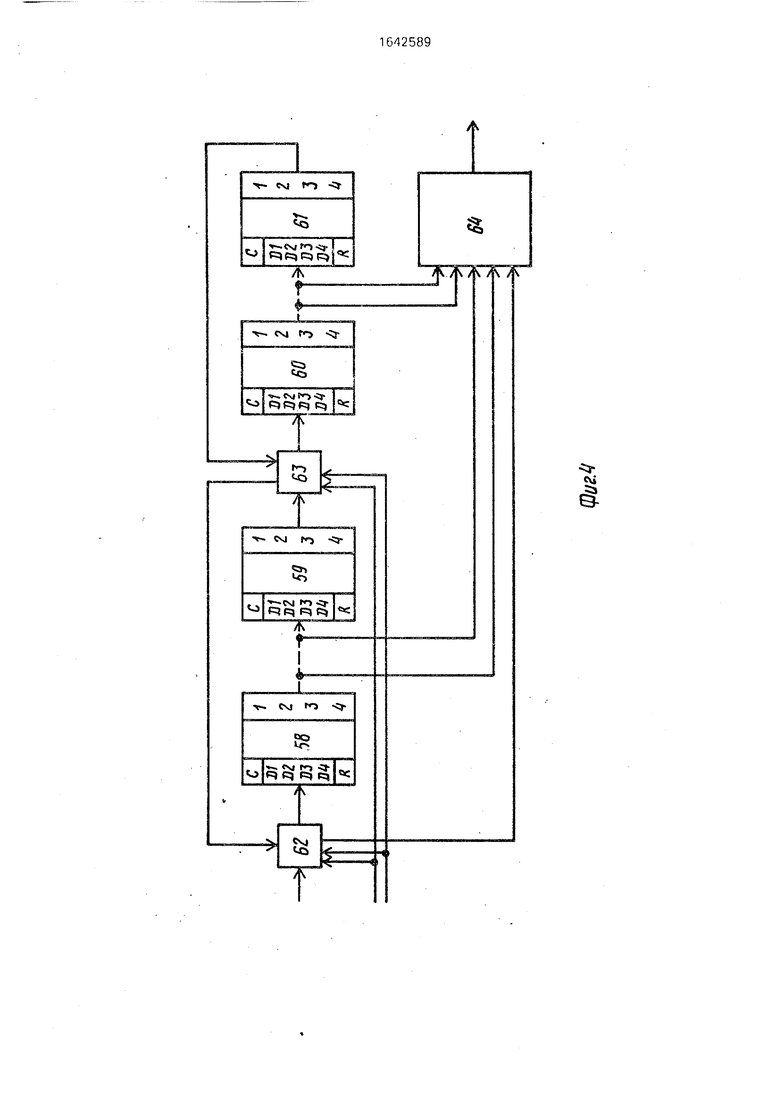

Блок 9 выбора минимума содержит (фиг.5), например, элементы 65-67 сравнения и мультиплексоры 68 и 69.

Блок 24 выбора максимума, входящий в анализатор 11, выполнен так же, как и блок 9, но в элементах 65-67 сравнения используются выходы Больше.

Источники 47-49 постоянного кода блока 17 формируют коды, значения которых указаны ниже.

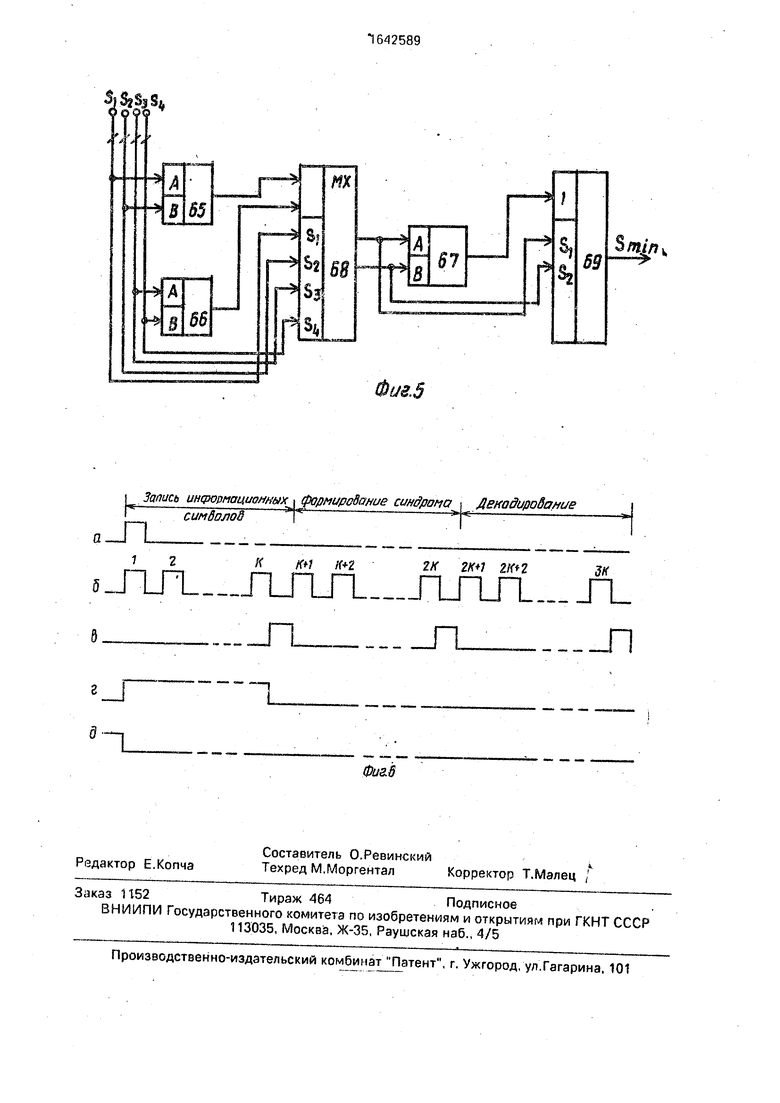

На фиг.б обозначены следующие сигналы в блоке 17 управления: а - импульсы

синхронизации; б - тактовые импульсы;.в - импульсы на выходе делителя 50 часто ты; г - сигнал на втором выходе 54 (первом выходе счетчика 43); д - сигнал установки счетчиков 44-46 (с последнего выхода счетчика43).

Алгоритм декодирования q-ичного мажоритарного кода с использованием надежности символов состоит в следующем. Имеем (п,к,5)ч-код, где п -длина кода; k

- число информационных символов; S - число проверок; V - минимальное кодовое рас- стояние; q - значность кода. Пусть «1 , QZ ,..., On - значения принятых кодовых символов; , fofin - надежность принятых символов, причем at {0,1..., g -1}, а

/ft Ј {0,12W}, где W - кратность входов

19, в общем виде/ г Ј{0, I. 2II (2W - 1)},

где I - целое. Последовательно декодируются все символы кода. При декодировании

f-ro символа вычисляем шп (f 1 ,n; p 1,5} значение р -и проверки относительно f-ro символа. Каждой проверке Qfn приписываем все ytn, равный минимальной надежно- сти символа, входящего в нее

(f rn;,o ). Далее вычисляем величины At и АО:

At 2 у(приО От),т Ј{1,S}; АО 2) ( при Qt 0 ), t Ј-{1,S};

т.е. сумму надежностей проверок, жесткое значение которых равно Qt, и сумму надежностей проверок, жесткое значение которых равно нулю. Затем находим величины

fan - At - ---, максимальную из которых

сравниваем с порогом , а соответствующее /up & 0 значение t сравниваем с порогом Т. В случае превышения величины 0 над порогом/ и соответствующего значения t над порогом 1 считаем, что значение ошибки равно Qt. Тогда ttf (at - Of ) mod q. В случае непревышения любого из указанных порогов исправления не происходит и . Затем осуществляется декодирование следующего символа.

С учетом изложенного алгоритма пороговый декодер работает следующим образом.

Поступающая на входы 18 информация, представляющая собой слово q-ичного мажоритарного (n, k, у)-кода, записывается в формирователь 1 синдрома и через первый коммутатор 4- в регистр 3 данных. Коммутатор 4 находится в положении, обеспечивающем запись k информационных символов из последовательности длины п. Одновременно в регистр 8 надежностей символов с входов 19 записываются значения надежностей символов кода. После окончания записи начинается процесс формирования синдрома. При этом символы кодового слова продвигаются по регистру формирователя 1 синдрома и с соответствующих отводов поступают на сумматор 64 по модулю q. Одновременно с этим по регистру 8 надежностей символов продвигаются числа , соответствующие надежности символов.

В формировании каждого символа синдрома участвует несколько символов кода (в соответствии со свойствами кода). Одновременно на входы блока 9 выбора минимума поступают значения, соответствующие надежности каждого из символов кода, участвующих в формировании данного символа синдрома. В соответствии с приведенным алгоритмом данному символу синдрома будет соответствовать минимальная надежность из надежностей символов кода, входящих в него (синдром). Каждый символ синдрома последовательно записывается в формирователь 2 проверок, одновременно соответствующее значение надежности записывается в регистр 10 надежностей проверок. Выходы блоков 2 и 10 подключены к анализатору 11. При этом выходы формирователя 2 и регистра 10 выбираются в соответствии со свойствами кода (например, для самоортогонального квазициклического кода (32, 26) это отводы 1, 2, 5, и 1, 3, 8). С регистра 10 на входы анализатора 11 поступают значения соответствующих надежностей проверок.

Анализатор 11 предназначен для фор- мирования следующих величин: суммы надежностей проверок, жесткое значение которых равно нулю; максимальной из сумм

надежностей проверок, жесткое значение которых равно Qt; количества проверок, принявших одинаковое значение Qt и имеющих максимальную сумму надежностей; значения проверок, принявших одинаковое

0 значение и имеющих максимальную сумму надежностей.

Анализатор 11 работает следующим образом.

На входы 30 блока 22 вычисления суммы

5 надежностей одинаковых символов поступают значения символов Si,..., Sn с выходов формирователя 2 проверок, а на входы 31 - соответствующие им значения надежности Pi Рп с выходов регистра 10 надежно0 стей проверок. В элементах 38 сравнения происходит попарное сравнение поступивших значений проверок между собой на предмет обнаружения одинаковых значений. Сигналы с выходов элементов 38 срав5 нения управляют мультиплексором 36, который по этим сигналам пропускает на входы сумматоров 39 соответствующее значение надежности (в случае, если нет одинаковых символов, задействованы все четыре

0 сумматора 39). Кроме того, в счетчиках 37 накапливается информация о числе одинаковых среди входных символов. Одновременно в блоке 23 дешифрации нулевых символов происходит выявление наличия

5 нулевых символов среди входных. Кодовая последовательность, образующаяся на выходах дешифраторов 41 нуля блока 23, управляет коммутаторами 25, пропускающими на блок 24 выбора максимума сумму

0 надежностей символов с одинаковым ненулевым значением (первые выходы 32), а также мультиплексором 26, на выходы которого поступает сумма надежностей проверок, жесткое значение которых равно нулю (чет5 вертые выходы 35). Далее надежности символов, принявших одинаковое значение, сравниваются в элементах 29 с максимальной надежностью и образующийся код управляет мультиплексором 27, с которого на

0 вторые выходы 33 поступает значение количества проверок, принявших одинаковое значение и имеющих максимальную надежность, Тот же код управляет следующим мультиплексором 28 и пропускает на третьи

5 выходы 34 значения числа проверок, принявших одинаковое значение.

После сформирования на выходах анализатора 11 указанных величин во втором блоке 14 сравнения происходит сравнение с нулевым порогом, сформированным в блоке 17 управления, разности между максимальной из сумм надежностей. проверок, жесткое значение которых равно Qt, и суммой надежностей проверок, жесткое значение которых равно нулю. Сигнал превышений порога открывает второй коммутатор 5 и на входы первого блока 13 сравнения поступает максимальная из сумм надежностей проверок, жесткое значение которых равно Qt. Если и этот порог превы- шен, то сигнал превышения открывает третий коммутатор 6 и на входы третьего блока 15 сравнения поступает третья величина, сформированная в анализаторе 11. Превышение порога позволяет проходить на вхо- ды сумматора 16 под модулю q значению Qt. которое и является значением ошибки. На другие входы сумматора 16 поступает из регистра 3 данных значение ошибочного символа ад. При этом значение исправлен- ного символа а; ( од - Qf ) mod q.

В пороговом декодере устанавливаются два порога по вероятности символа (надежности), один из которых нулевой, и по числу проверок, принявших одинаковое значе- ние. Это позволяет не вносить ошибки в правильную позицию.

Пороговый декодер за счет учета надеж- носгей символов приближается к декодеру максимального правдоподобия. Использо- зание мягкого решения позволяет существенно улучшить результаты декодирования, Особенно эффективной оказывается данная схема в канале с -переменными параметрами.

Формула изобретения

1. Пороговый декодер q-ичного кода, содержащий формирователь синдрома, ин- формационные входы которого объединены с соответствующими информационными пходами первого коммутатора и являются первыми информационными входами декодера, выходы формирователя синдрома и первого коммутатора соединены с входами соответственно форми рователя проверок и регистра данных, выходы которых подключены к первым входам соответственно анализатора проверок и сумматора по модулю q, выходы которого являются выходами декодера, первые и вторые выходы анализатора проверок соединены с информационными входами соответственно второго и третьего коммутаторов, выходы второго коммутатора подключены к первым входам первого блока сравнения, блок управления, тактовый входи вход синхронизации которого являются одноименными

входами декодера, первый выход блока управления подключен к управляющему входу первого коммутатора и первому управляющему входу формирователя синдрома, второй выход блока управления соединен с вторым управляющим входом формирователя синдрома, третьи выходы блока управления подключены к вторым входам первого блока сравнения, выход которого соединен с управляющим входом третьего коммутатора, отличающийся тем, что, с целью повышения помехоустойчивости, в декодер введены блок выбора минимума, блок вычитания, четвертый коммутатор, второй и третий блоки сравнения, регистр надежностей проверок и регистр надежностзй символов, информационные входы которого являются вторыми информационными входами декодера, первый и второй управляющие входы регистре надежностзй символов подключены соотеетственно к первому и второму ьы- ходам блока управления, выходы регистре надежностей символов соединены с входами блока выбора минимума, выходы которого подключены к входам регистра надежностей проверок, выходы которого соединены с вторыми входами анализатора проверок, третьи и четвертые выходы которого подключены соответственно к информационным входам четвертого коммутатора и первым входам блока вычитания, вторые входы которого подключены к первым выходам анализатора проверок, выходы блока вычитания и четвертые выходы блока управления соединены с первыми и вторыми входами второго блока ср-авнения, зыход котЪрого подключен к управляющему входу второго коммутатору, выходы третьего коммутатора и пятые выходы блока управления соединены с первыми и вторыми входами третьего блока сравнения, выход которого подключен к управляющему входу четвертого коммутатора, выходы которого соединены с сторыми входами сумматора по модулю q,

2. Декодер по п.1,отличающийся тем, что анализатор проверок содержит блок дешифрации нулевых символов, блок выбора максимума, первый-третий мультиплексоры, группу коммутаторов, группу элементов сравнения и блок вычисления суммы надежностей одинаковых символов, первые входы которого объединены с соответствующими входами блока дешифрации нулевых символов и информационными входами третьего мультиплексора и являются первыми входами анализатора, вторые входы блока вычисления суммы надежностей одинаковых символов являются вторыми входами анализатора, первые выходы блока

вычисления суммы надежностей одинаковых символов подключены к информационным входам соответствующих коммутаторов группы, к первым входам соответствующих элементов сравнения группы и к соответствующие информационным входам первого мультиплексора, выходы блока дешифрации нулевых символов соединены с соответствующими адресными входами первого мультиплексора и управляющими входами соответствующих коммутаторов группы, выходы которых подключены к соответствующим входам блока выделения максимума, выходы которого соединены с вторыми входами всех элементов сравнения группы и являются первыми выходами анализатора, вторые выходы блока вычисления суммы надежностей одинаковых символов подключены к соответствующим информационным входам второго мультиплексора, выходы элементов сравнения группы соединены с соответствующими адресными входами второго и третьего мультиплексоров, выходы которых и выходы первого мультиплексора являются соответственно вторыми-четвертыми выходами анализатора.

3. Декодер по п.2, отличающийся тем, что блок вычисления суммы надежностей одинаковых символов содержит h мультиплексоров (h - число групп в первых и вторых входах анализатора проверок), h двоичных счетчиков, h сумматоров, Ь-2 элементов И и Ch2 элементов сравнения, первые и вторые входы каждого из которых подключены к соответствующей паре групп первых блока, i-e информационные входы (I 1,h) первого - 1-го мультиплексоров подключены к i-й группе вторых входов блока, выходы элементов сравнения, первые входы которых подключены к i-й группе первых входов блока, соединены с соответствующими адресными входами 1-го мультиплексора и счетными входами i-ro двоичного счетчика, выходы элементов сравнения, вторые входы которых подключены к i-й (кроме i h) группе первых входов блока, соединены с входами соответствующего элемента И, выход которого подключен к управляющим входам i-x мультиплексора и двоичного счетчика, выход элемента сравнения, входы которого подключены к паре последних групп первых

входов блока, соединен с прямыми адресными зходами (п-1)-х и инверсными адресными входами h-x мультиплексоров и двоичных счетчиков, выходы мультиплексоров соединены с входами одноименных сумматоров, выходы которых и выходы двоичных счетчиков являются соответственно первыми и вторыми выходами блока,

4.Декодер по п.2, отличающийся тем/что блок дешифрации нулевых символов содержит h дешифраторов нуля и h-2 элементов И, первые входы первого - h-ro дешифраторов нуля являются соответствующими входами блока, выход первого дешифратора нуля подключен к второму входу

второго дешифратора нуля и первым зходам всех элементов И и является первым разрядом выходов блока, выход Ко дешифратора нуля (j 2,h-1) соединен с j-ми входами (J-1}- го - (h-2)-ro элементов И и является j-м разрядом выходов блока, выход h-ro дешифратора нуля является h-м разрядом выходов блока.

5.Декодер по п.1,отличающийся тем, что блок управления содержит первыйчетвертый двоичные счетчики, первый-тре- тий источники постоянного кода и делитель частоты, тактовый вход которого является тактовым входом блока, входы обнуления делителя частоты и первого двоичного счетчика объединены и являются входом синхронизации блока, выход делителя частоты подключен к счетным входам всех двоичных счетчиков и является первым выходом блока, первый выход двоичного счетчика является вторым выходом блока, последний выход первого двоичного счетчика подключен к его управляющему входу и входам обнуления второго-четвертого двоичных счетчиков, выходы первого-третьего источников постоянного кода соединены с установочными входами соответственно второго-четвертого двоичных счетчиков, выходы которых являются соответственно третьими-пятыми выходами блока.

1

| название | год | авторы | номер документа |

|---|---|---|---|

| ДЕКОДЕР СВЕРТОЧНОГО КОДА | 1992 |

|

RU2085035C1 |

| Устройство для устранения неопределенности дискретнофазовой модуляции | 1983 |

|

SU1095428A1 |

| Кодек квазициклического кода | 1986 |

|

SU1349010A1 |

| Декодер сверточного кода | 1986 |

|

SU1388998A1 |

| Устройство цикловой синхронизации | 1984 |

|

SU1197122A1 |

| Вероятностный мажоритарный декодер | 1986 |

|

SU1396282A1 |

| ПОРОГОВЫЙ ДЕКОДЕР СВЕРТОЧНОГО КОДА | 1991 |

|

RU2023349C1 |

| Кодек несистематического сверточного кода | 1988 |

|

SU1580567A1 |

| Пороговый декодер сверточного кода | 1982 |

|

SU1078654A1 |

| Кодек блочного кода | 1985 |

|

SU1358098A1 |

Изобретение относится к вычислительной технике и технике связи. Его использование в сетях ЭВМ и каналах связи дискретных систем передачи информации повышает помехоустойчивость. Пороговый декодер содержит формирователь 1 синдрома, формирователь 2 проверок, регистр 3 данных, коммутаторы 4-6, анализатор 11 проверок, блок 13 сравнения, сумматор 16 по модулю q и блок 17 управления. Благодаря введению коммутатора 7, регистра 8 на- дежностей символов, блока 9 выбора минимума, регистра 10 надежностей проверок, блока 12 вычитания и блоков 14, 15 сравнения в декодере осуществляется мягкое декодирование, не вносящее ошибки в правильную позицию. 4 з.п. ф-лы, 6 ил. в 44М СЛ С

t

«M

-t

Mj

Hesfes

Ј -.

tabd 1зь

-t- O4 ГЧ5-.

гча .

ta fcdfcdta съ

. . i

-OjfS

-fi Oj IN .

V

b )tatdta

I S-U4«V -

H

t- a -Jw

5

з&Ч

Запись информационных формирование синдрома Декодиробание

П-П

символов

1 г

К /f+2

.

dmtn

2/f

J/r

..п

П.

| Некоторые вопросы теории кодирования /Под ред | |||

| Э.Л.Блоха и М.С.Пинсхера | |||

| М.: Мир, 1970, с | |||

| Прибор для нагревания перетягиваемых бандажей подвижного состава | 1917 |

|

SU15A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Зарубежная радиоэлектроника, 1986, № 7, с | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Авторское свидетельство СССР № 1301283 | |||

| кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-04-15—Публикация

1989-02-20—Подача