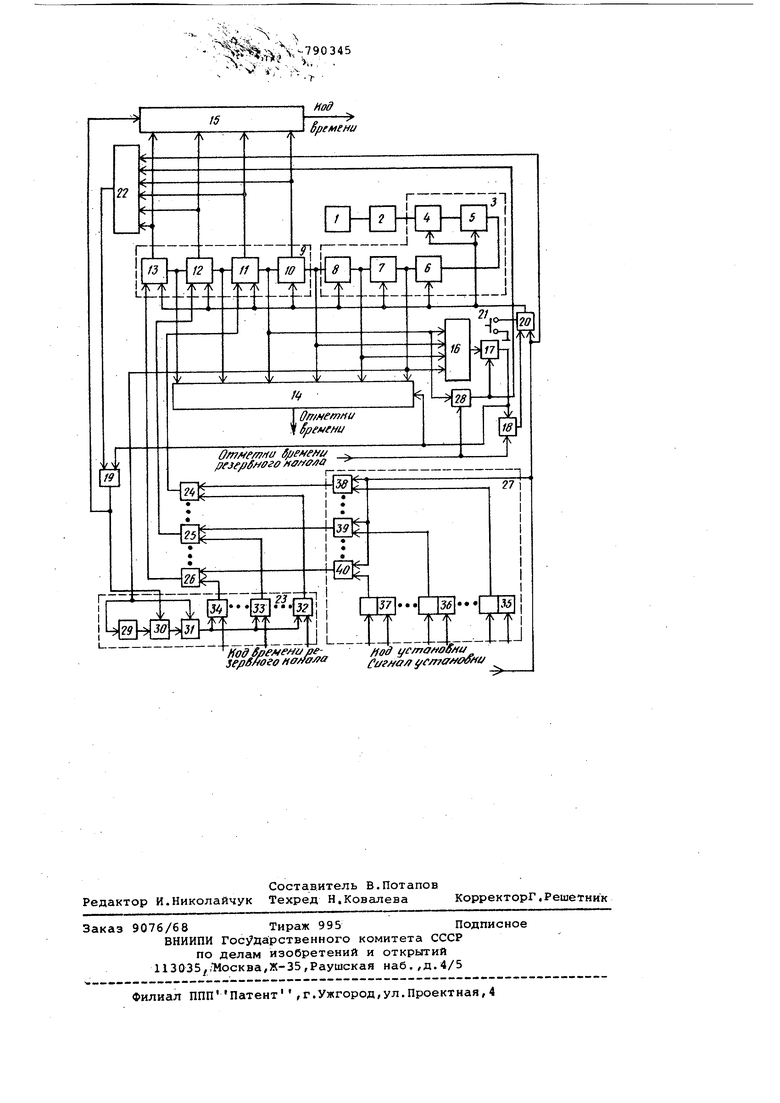

Изобретение относится к импульсной технике и предназначено для надежного счета и деления частоты следо вания импульсов в условиях сбоев и отказов отдельных элементов. Известно устройство Нормирования отметок времени, содержащее генератор стабильной частоты, делители, счетчик и светодиоды l. Недостатками этого устройства являются невозможность точной коррек тировки сигналов времени и низкая надежность из-за отсутствия устройств контроля. Наиболее близким к предлагаемому по технической сущности является устройство для формирования отметок времени , включающее генератор стабильной частоты,формирователь импульсов,блок деления частоты,блок формирования кода,формирователь отметок времени,бло выходных усилителей, блок сигнала ошибки, триггер и блок автоматическо го запуска 2 Недостаток известного устройства - его относительно низкая информативная надежность, так как имеется только контроль сигналов с выходов блока деления частоты. Кроме того, при отказе блока деления основной канал. отключается и может быть включен только вручную или по сигналам точного времени, т.е. 1 раз в течение часа. Таким образом, в течение часа устройство работает на одном канале, что резко снижает надёжность устройства в целом,А также поскольку коррек Ция кода времени осуществляется обнулением, то выставив правильнып код можно тоже только 1 раз в час, что увеличивает время подготовки к работе устройства в целом. Цель изобретения - повышение надежности устройства. Указанная цель достигается тем, что в устройство для формирования отметок времени,содержащее последовательно соединенные генератор стабильной частоты, формирователь импульсов, блок деления частоты и блок формирования кода, выходы которого подключены ко входам формирователя отметок времени и блока выходных усилителей,блок запуска,блок сигнала ошибки,входы которого подключены к выходам блока деления частоты, а выход соединен с первым входом триггера, выход которого соединен со входом запрета формирователя отметок време ни, введены два элемента совпадения . два элемента ИЛИ, блок элементов ИЛИ, блок коррекции и блок контроля информационные входы которого подключены к выходам блока формировани кода, а выход через первый элемент ИЛИ соединен с запрещающим входом блока выходных усилителей и первым входом блока коррекции, второй вход которого подключен к выходу блока деления частоты,а выходы блока коррекции через блок элементов ИЛИ, другие входы которых соединены с выходами блока запуска, подключены к установочным входам блока формирования кода, при этом третий вход блока коррекции является входом кодавремени резервного канала,второй вход триггера соединен со входом сброса блока контроля и выходом первого элемента совпадения, входы которого подключены соответственно к выходу блока деления частоты и пер вому входу второго элемента совпадения, второй вход которого соединен с выходом триггера и вторым входом первого элемента ИЛИ, а выход первого элемента совпадения подключен к первому входу второго элемента ИЛИ, .второй вход которого соединен с шиной сигнала установки, перБмм входом блока запуска и запрещающим входом блока контроля, выход второго элемента ИЛИ подключен к установочным входам блоков деления частоты и формирования кода, при этом второй вход блока запуска является входом кода установки, при это блок коррекций содержит последова- . тельно соединенные расширитель импул сов, первый элемент совпадения и элемент запрета, выход которого сое динен с первыми, входами других элементов совпадения, вторые входы и выходы которых .соединены соответственно с третьим входом и выходом блока коррекции,. при этом второй вход первого элемента совпадения со единен с первым входом блока коррек ции , а вход расширителя импульсов подключен ко второму входу элемента запрета и второму входу блока коррек ции,а блок запуска содержит триггеры входы которых соединены со вторым вх дом блока запуска,а выходы поразрядн соединены с первыми входами элементов совпадения, вторые входы и выхо ды которых подключены соответственно к первому входу и выходу блока запуска. На чертеже приведена функциональ ная схема устройства для формирован отметок времени. Устройство содержит опорный гене ратор 1, формирователь 2 импульсов, блок 3 деления частоты, делители 48 частоты, блок 9 формирования кода счетчики 10-13 миллисекунд, секунд, минут и часов соответственно, форми рователь 14 отметок времени, блок 15 выходных усилителей,блок 16 сигнала ощибки, триггер 17 , элемент 18 совпадения, элементы ИЛИ 19 и 20, кнопку 21 сброса, блок 22 контроля, блок 23 коррекции, блок элементов ИЛИ 24-26, блок 27 запуска, элемент 28 совпадения, расширитель 29 импульсов, элемент 30 совпадения, элемент 31 запрета, элементы 32-34 совпадения, триггеры 35-37 и элементы 38 38,39 и 40 совпадения. Устройство работает следующим образом. Сигналы опорного генератора 1 через формирователь 2 импульсов поступают в каждый канал для запуска блока деления частоты, с помощью которого формируется требуемая сетка частот. Сигналы частотой следования, например, 1 кГц поступают на вход блока 9 формирования кода, где происходит оцифровка временных меток в пределах суток. Запуск блоков деления частоты и формирования кода осуществляется с помощью кнопки 21 сброса. Первоначальная установка значения текущего кода времени производится с помощью блока 27 запуска. Для этого вручную или авт(.-:-:Птн чески набирается код установки. По сигналу установки этот код поступает с триггеров 35-37 через элементы совпадения 38-40 и блок элементов ИЛИ 24-26 на установочные входы блока формирования кода. Сигнал установки одновременно поступает на запирающий вход блока 22 контроля,°тем самым предотвращая появление сигнала ошибки при установке кода в блоке формирования кода. в случае сбоя или отказа блока деления частоты блок 16-сигнала ошибки вырабатывает сигнал переключения триггера 17, который в свою очередь через элемент 18 совпадения подключает к цепи сброса сбившихся делителей отметки времени и резервного ,канала. Сигнал с триггера 17 через элемент ИЛИ 19 поступает также на запрещающий вход блока 15 выходных усилителей и на первый вход блока 23 коррекции. Одновременно на второй вход блока коррекции подаются сигналы с блока деления частоты. При . совпадении этих сигналов на элементе 30 вырабатывается управляющий сигнал, по которому код времени из резервного канала через элементы 32-34 совпадения и блок элементов ИЛИ 24, 25 и 26 переписываетса .в.отключенный канал,После коррекции кода и частот сигнал совпадения отметок времени основного и резервного каналов через элемент 28 совпадения сбрасывает триггер 17,при этом снимается запрет с формирователя 14 отметок времени и блока 15 выходных усилителей.

3 случае отказа или сбоя блока формирования кода блок 22 контроля вырабатывает сигнал, который через элемент ИЛИ 19 поступает на вхо блока коррекции. При этом коррекция кода происходит аналогично описаннму выше. После коррекции сигнал с выхода блока контроля кода снимается сигналом, который поступает с элемента 28 совпадения.

Автоматическое восстановление работоспособности устройства с затратой минимального времени позволяет повысить надежность устройства и одновременно уменьшить время подготовки к работе.

Оормула изобретения

1. Устройство для формирования отметок времени, содержащее последовательно соединенные генератор стабильной частоты, формирователь импульсов, блок деления частоты и блок формирования кода, выходы которого подключены ко входам формирователя отметок времени и блока выходных усилителей, блок запуска, блок сигнала ошибки, в.ходы которого подключены к выходам блока деления частоты, а выход соединен с первым входом триггера, выход которого соединен со входом запрета формирователя отметок времени, отличающееся тем, что, с целью повышения надежности, в него введены дв элемента совпадения, два элемента ИЛИ, блок элементов ИЛИ, блок корреции и блок контроля, информационные входы которого подключены к выходам блока формирования кода, а выход через первый элемент ИЛИ соединен с запрещающим входом блока выходных усилителей и первым входом коррекции , второй вход которого подключен к выходу блока деления частоты, а выходы блока коррекции через блок элементов ИЛИ, другие входы которых соединены с выходами блока запуска, подключены к установочным входам блока формирования кода, при этом третий вход блока коррекции

и

является входом кода времени резервного канала, второй вход триггера соединен со входом сброса блока контроля и выходом первого элемента совпадения, входы которого подключены соответственно к выходу блока деления частоты и первому входу второго элемента совпадения, второй вход которого соединен с выходом триггера и вторым входом первого элемента ИЛИ, а выход первого элемента совпадения подключен к первому входу второго элемента ИЛИ, второй вход которой соедин ен с шиной сигнала установки, первым входом блока запуска и запре1щающим входом блока контроля, выход второго элемента ИЛИ подключен к установочным входам блоков деления частоты и формирования кода, при этом второй вход блока запуска является

0 входом кода установки.

2. Устройство по п. 1, о т л и чающееся тем, что блок коррекции содержит последовательно соединенные расширитель импульсов,

5 первый элемент совпадения и элемент запрета, выход которого соединен с первыми входами других элементов совпадения, вторые входы и выходы которых соединены соответственно с третьим входом и выходом блока кор0рекции , при этом второй вход первого элемента совпадения соединен с первым входом блока коррекции, а вход расширителя импульсов подключен ко второму входу элемента запрета и второ5му входу блока коррекции. 3. Устройство по п. 1, отличающееся тем, что блок запуска содержит триггеры, входы которых соединены со вторым входом блока за0пуска, а выходы поразрядно соединены с первыми входами элементов совпадения, вторые входы и выходы которых подключены соответственно к первому входу и выходу блока запуска.

Источники информации,

5 принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 355597, кл. G 04 С 3/00,1971.

2.Авторское свидетельство СССР 419836,кл. Н 05 К 10/00, 1971,

0

..л.

. . ..v

/ ycmoMoS/ta

Се/г/fa/f yf/na ff tJ

.W

L IT-UJ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования отметок времени | 1983 |

|

SU1092729A2 |

| Устройство коррекции шкалы времени | 1988 |

|

SU1525932A1 |

| Устройство для формирования отметок времени | 1987 |

|

SU1684777A1 |

| Устройство для формирования управляемых отметок времени | 1986 |

|

SU1370645A2 |

| Устройство для формирования отметок времени | 1979 |

|

SU972470A1 |

| Устройство для коррекции шкалы времени | 1987 |

|

SU1432451A2 |

| Устройство для коррекции шкалы времени | 1986 |

|

SU1370643A2 |

| Устройство для коррекции шкалы времени | 1982 |

|

SU1095431A1 |

| Устройство для коррекции шкалы времени | 1986 |

|

SU1365039A2 |

| Устройство коррекции шкалы времени | 1986 |

|

SU1363509A1 |

Авторы

Даты

1980-12-23—Публикация

1979-01-08—Подача