tuuA

СП

го

СЛ

QO со

ьо

1

Изобретение относится к радиотехнике и приборостроению и может быть использовано в синхронизирующих устройствах и хранителях времени для коррек ции шкалы времени.

Целью изобретения является повышение точности коррекции шкалы времени.

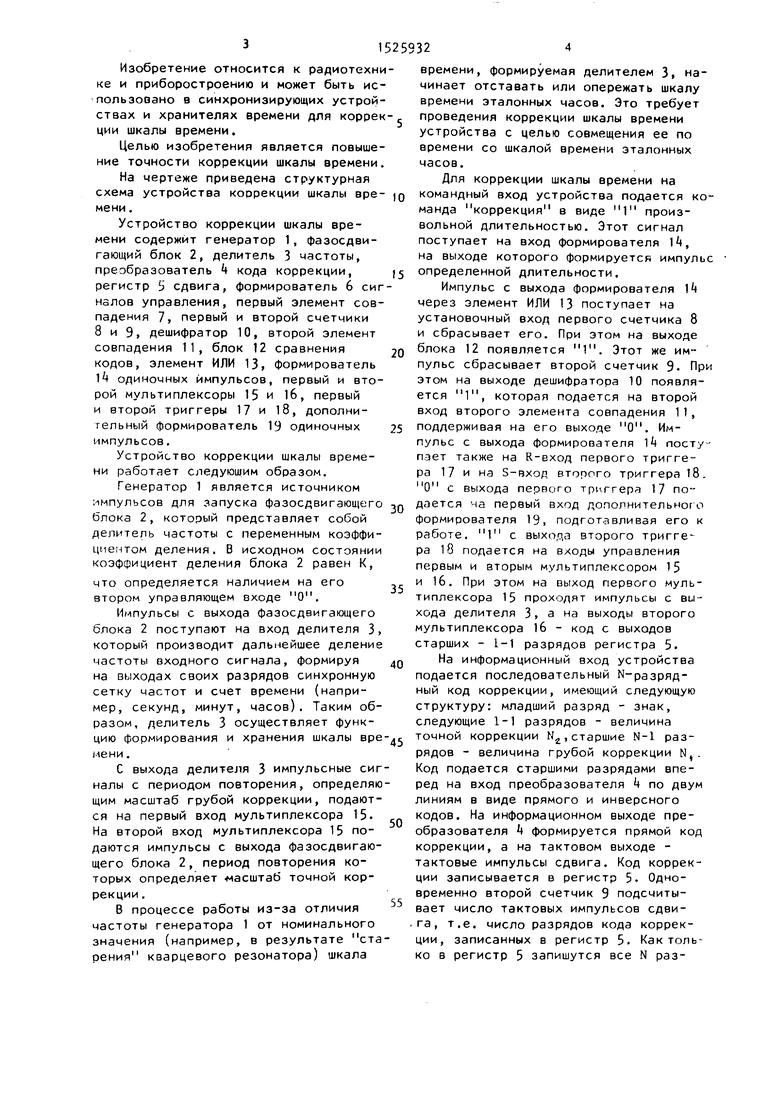

На чертеже приведена структурная схема устройства коррекции шкалы вре- мени,

Устройство коррекции шкалы времени содержит генератор 1, фазосдви- гающий блок 2, делитель 3 частоты, преобразователь кода коррекции, регистр 5 сдвига, формирователь 6 сигналов управления, первый элемент совпадения 7, первый и второй счетчики 8 и 9, дешифратор 10, второй элемент совпадения 11, блок 12 сравнения кодов, элемент ИЛИ 13, формирователь И одиночных импульсов, первый и второй мультиплексоры 15 и 1б, первый и второй триггеры 17 и 18, дополнительный формирователь 19 одиночных импульсов,

Устройство коррекции шкалы времени работает следующим образом.

Генератор 1 является источником импульсов для запуска фазосдвигающего блока 2, который представляет собой делитель частоты с переменным коэффициентом деления. В исходном состоянии коэффициент деления блока 2 равен К,

что определяется наличием на его втором управляющем входе О.

Импульсы с выхода фазосдвигающего блока 2 поступают на вход делителя 3, который производит дальнейшее деление частоты входного сигнала, формируя на выходах своих разрядов синхронную сетку частот и счет времени (например, секунд, минут, часов). Таким образом, делитель 3 осуществляет функцию формирования и хранения шкалы вре мени.

С выхода делителя 3 импульсные сигналы с периодом повторения, определяющим масштаб грубой коррекции, подаются на первый вход мультиплексора 15. На второй вход мультиплексора 15 подаются импульсы с выхода фазосдвигающего блока 2, период повторения которых определяет масштаб точной коррекции.

В процессе работы из-за отличия частоты генератора 1 от номинального значения (например, в результате старения кварцевого резонатора) шкала

0 5

Q

5

Q

п

5

324

времени, формируемая делителем 3, начинает отставать или опережать шкалу времени эталонных часов. Это требует проведения коррекции шкалы времени устройства с целью совмещения ее по времени со шкалой времени эталонных часов.

Для коррекции шкалы времени на командный вход устройства подается команда коррекция в виде 1 произвольной длительностью. Этот сигнал поступает на вход формирователя И, на выходе которого формируется импульс определенной длительности.

Импульс с выхода формирователя через элемент ИЛИ 13 поступает на установочный вход первого счетчика 8 и сбрасывает его. При этом на выходе блока 12 появллется 1. Этот же импульс сбрасывает второй счетчик 9- При этом на выходе дешифратора 10 появляется 1, которая подается на второй вход второго элемента совпадения 11, поддерживая на его выходе О. Импульс с выхода формирователя И поступает также на R-вход первого триггера 17 и на S-вход второго триггера 18. О с выхода первого триггера 17 подается на первый вход дополнительного формирователя 19, подготавливая его к работе. 1 с выхода второго триггера 18 подается на входы управления первым и вторым мультиплексором 15 и 16. При этом на выход первого мультиплексора 15 проходят импульсы с выхода делителя 3, а на выходы второго мультиплексора 1б - код с выходов старших - 1-1 разрядов регистра 5.

На информационный вход устройства подается последовательный N-разряд- ный код коррекции, имеющий следующую структуру: младший разряд - знак, следующие 1-1 разрядов - величина точной коррекции N.старшие N-1 разрядов - величина грубой коррекции N. Код подается старшими разрядами вперед на вход преобразователя 4 по двум линиям в виде прямого и инверсного кодов. На информационном выходе преобразователя t формируется прямой код коррекции, а на тактовом выходе - тактовые импульсы сдвига. Код коррекции записывается в регистр 5. Одновременно второй счетчик 9 подсчитывает число тактовых импульсов сдвига, т.е. число разрядов кода коррекции, записанных в регистр 5. Как только в регистр 5 запишутся все N раз51S25932

ов кода, на выходе дешифратора 10 вляется О, который поступает второй (инверсный) вход второго мента 11 совпадения.

5

по н сл в п п т во и 15 т п в н мл ч

О, поступающий на второй вход второго элемента 11 совпадения, выII t II

зывает появление на его выходе 1 так как на первом входе присутствует 1 с выхода блока 12.

1 с выхода второго элемента 11 совпадения подается на первый вход формирователя 6. После этого по заднему фронту импульса, поступающего на второй вход, на выходе формирователя 6 появляется сигнал управления в виде 1. Сигнал управления поступает на второй управляющий вход фазосдви- гающего блока 2 и изменяет его коэффициент деления на КЦ в зависимости от знака, поступающего на первый управляющий вход с выхода младшего разряда регистра 5. Одновременно сигнал управления открывает первый элемент совпадения 7. При этом импульсы с выхода первого мультиплексора 15 начинают проходить на счетный вход первого счетчика 8.

Изменение коэффициента деления фа- зосдвигающего блока 2 на К±1 приводит к тому, что каждый импульс на выходе сдвигается в сторону отставания или опережения относительно импульсов на выходе блока 2 при исходном коэффициенте деления. Это приводит к сдвигу шкалы времени, формируемой делителем 3. Первый счетчик 8 подсчитывает число импульсов, поступающих на его вход. Двоичный код с выходов его разрядов поступает на первые входы блока 12, на вторые входы которого поступает двоичный код величины грубой коррекции с выходов второго мультиплексора 1б. При совпадении кодов на выходе блока 12 формируется перепад напряжения из состояния 1 в состояние О. По этому перепаду переворачивается первый триггер 17. Логический О с выхода блока 12 запирает второй элемент совпадения 11, с выход которого П поступает на первый вход формирователя 6. Формирователь 6 возвращается в исходное состояние, и логический О с его выхода восстанавливает исходный коэффициент деления фазосдвигающего блока 2 и запрещает прохождение сигналов через первый элемент совпадения 7.

1 с выхода первого триггера 17

5

10

20

поступает на перрыи вход дополнительного формирователя 19, на выходе которого выделяется второй импульс из последовательности, поступающей на его второй вход с выхода делителя 3 через первый мультиплексор 15. Этот, импульс поступает на R-вход второго триггера 18 и устанавливает его нулевое состояние. О с выхода второго триггера 18 подается на управляющие гаходы первого и второго мультиплексоров 15 и 16, при этом на выход первого муль- 15 типлексора 15 начинают проходить импульсы с выхода блока 2, а на выходы второго мультиплексора 1б - на двоичный код точной коррекции с выходов младших разрядов регистра 5 за исключением первого разряда.

0

5

0

5

5

Импульс с выхода дополнительного формирователя 19 через элемент ИЛИ 13 подается на установочный вход первого счетчика 8 и сбрасывает его. На выходе блока 12 появляется 1, которая подается на первый вход второго элемента совпадения 11. На втором входе второго элемента совпапения 11 присутствует О с выхола дешифратора 10. На вторсто элемента совпадения 11 появляется 1, которая запускает формирователь 6. По заднему фронту второго импульса на втором входе формирователь 6 формирует на выходе сигнал управления в виде логической 1, который изменяет коэффициент деления блока 2 на (Ktl) в зависимости от знака .коррекции и разрешает прохождение импульсов, поступающих с выход а блока 2 через первый мультиплексор 13, на счетный вход первого счетчика 8 через первый элемент совпадения 7. При совпадении кода, поступающего с выходов разрядов первого счетчика 8 на первый вход блока 12 с кодом точной коррекции, поступающим с выходов второго мультиплексора 16 на вторые входы, на выходе блока 12 появляется О, который запирает второй элемент совпадения 11. О с выхода второго элемента совпадения 11 возвращает формирователь 6 в исходное состояние. О с выхода формирователя 6 восстанавливает исходный коэффициент деления блока 2 и запрещает прохождение сигналов через первый элемент совпадения 7. Одновременно перепад напряжения из 1 в О с выхода блока

12 переворачивает первый триггер 17, на выходе которого появляется О.

Величина сдвига шкалы времени, полученная в результате коррекции, равна

ключены объединенные второй вход первого элемента совпадения и выход первого мультиплексора, к второму инфор- мационному входу которого подключен выход фазосдвигающего блока, выход де шифратора подключен к второму входу второго элемента совпадения, вход преобразователя кода коррекции являет- g ся кодовым входом устройства, отличающееся тем, что, с целью повышения точности коррекции шкалы времени, введены первый и второй триггеры, дополнительный формирователь

Т - период повторения импульсов | одиночных импульсов и второй мульти- генераторд 1.плексор, к управляюи1ему входу которого подключены объединенные выход втоФормула изобретениярого триггера и третий информационный

вход первого мультиплексора, выход Устройство коррекции шкалы времени, формирователя одиночных импульсов

содержащее последовательно соединенные подключен к объединенным первому вхоit iT(N,K,-fN,),

где К( - коэффициент деления делителя 3 от входа до выхода, соединенного с первым входом первого мультиплексора 15; N, - величина грубой коррекции; N,j - величина точной коррекции;

генератор, фазосдвигаю1ций блок, делитель частоты и первый мультиплексор, последовательно соединенные первый элемент совпадения, первый счетчик, блок сравнения кодов, второй элемент совпадении и формирователь сигналов управления, формирователь одиночных импульсов, элемент ИЛИ, последовательно соединенные преобразователь ко да коррекции, второй счетчик и дешифратор, а также регистр сдвига, к первому и второму входам которого подключены соответственно первый выход преобразователя кода коррекции и второй выход преобразователя кода коррекции, объединенный со счетным входом второго счетчика , выход младшего разряда регистра сдвига подключен к первому управляющему входу фазосдвигающего блока, к второму управляюи ему входу которого подключены объединенные первый вход первого элемента совпадения и выход формирователя сигналов управления, к второму входу которого под25

30

35

40

45

ду элемента ИЛИ, установочным входам первого и второго триггеров и установочным входам второго счетчика, выход первого триггера через дополнительный формирователь одиночных импульсов подключен к объединенным счетному входу второго триггера и второму входу элемента ИЛИ, выход которого подключен к установочному входу первого счег1|ика, счетный вхол, первого тригге ра подключен к выходу блока сравнения кодов, к первой и второй группам информационных входов вторс о мультиплексора подключены соотвеiственно первая и вторая группы выходом регист ра сдвига, выходы второго мультиплексора подключены к второй группе входов блока сравнения кодов, вход Фор- миоователя одиночных импульсов является командным входом устройства, вто рой вход дополнительного форммроватепп одиночных импульсов подключек к зюро му входу формирователя cvirH-H/ior управления ,

ду элемента ИЛИ, установочным входам первого и второго триггеров и установочным входам второго счетчика, выход первого триггера через дополнительный формирователь одиночных импульсов подключен к объединенным счетному входу второго триггера и второму входу элемента ИЛИ, выход которого подключен к установочному входу первого счег1|ика, счетный вхол, первого тригге ра подключен к выходу блока сравнения кодов, к первой и второй группам информационных входов вторс о мультиплексора подключены соотвеiственно первая и вторая группы выходом регист ра сдвига, выходы второго мультиплексора подключены к второй группе входов блока сравнения кодов, вход Фор- миоователя одиночных импульсов является командным входом устройства, вто рой вход дополнительного форммроватепп одиночных импульсов подключек к зюро му входу формирователя cvirH-H/ior управления ,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для коррекции шкалы времени | 1987 |

|

SU1506570A1 |

| Устройство для коррекции шкалы времени | 1986 |

|

SU1365039A2 |

| Устройство для коррекции шкалы времени | 1982 |

|

SU1095431A1 |

| Устройство для коррекции шкалы времени | 1985 |

|

SU1247828A2 |

| Устройство для коррекции шкалы времени | 1987 |

|

SU1432451A2 |

| Устройство для коррекции шкалы времени | 1985 |

|

SU1277413A2 |

| Устройство для коррекции шкалы времени | 1985 |

|

SU1307598A1 |

| Устройство для коррекции шкалы времени | 1986 |

|

SU1370643A2 |

| Устройство для коррекции шкалы времени | 1986 |

|

SU1413590A2 |

| Устройство для коррекции шкалы времени | 1991 |

|

SU1781669A1 |

Изобретение относится к радиотехнике. Цель изобретения - повышение точности коррекции шкалы времени. Устройство содержит г-р 1, фазосдвигающий блок 2, делитель 3 частоты, преобразователь 4 кода коррекции, регистр 5 сдвига, формирователь 6 сигналов управления, эл-ты совпадения 7 и 11, счетчики 8 и 9, дефифратор 10, блок сравнения 12 кодов, эл-т ИЛИ 13,формирователь 14 одиночных импульсов и мультиплексор 15. Цель достигается введением мультиплексора 16, триггеров 17 и 18 и формирователя 19 одиночных импульсов, с помощью которых осуществляется формирование величины кодов грубой и точной коррекции шкалы времени. 1 ил.

Авторы

Даты

1989-11-30—Публикация

1988-01-04—Подача