(54) ДЕСЯТИЧНЫЙ СЧЕТЧИК

| название | год | авторы | номер документа |

|---|---|---|---|

| Десятичный счетчик | 1978 |

|

SU782164A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1262504A1 |

| Генератор спектрометрических импульсов | 1986 |

|

SU1325671A1 |

| Многофункциональное счетное устройство | 1975 |

|

SU655073A1 |

| Устройство для определения направления и угла поворота вращающегося объекта | 1991 |

|

SU1786441A1 |

| Устройство для программного управления | 1987 |

|

SU1474595A1 |

| Счетчик импульсов с цифровой индикацией | 1984 |

|

SU1231602A1 |

| СПЕЦПРОЦЕССОР ДЛЯ ЗАДАЧИ ВЫПОЛНИМОСТИ БУЛЕВЫХ ФОРМУЛ | 2017 |

|

RU2644505C1 |

| МОДУЛЬ ВВОДА-ВЫВОДА СИСТЕМЫ ЦИФРОВОГО УПРАВЛЕНИЯ | 1991 |

|

RU2032201C1 |

| УСТРОЙСТВО ВВОДА-ВЫВОДА ИНФОРМАЦИИ ДЛЯ СИСТЕМЫ ЦИФРОВОГО УПРАВЛЕНИЯ | 1993 |

|

RU2042183C1 |

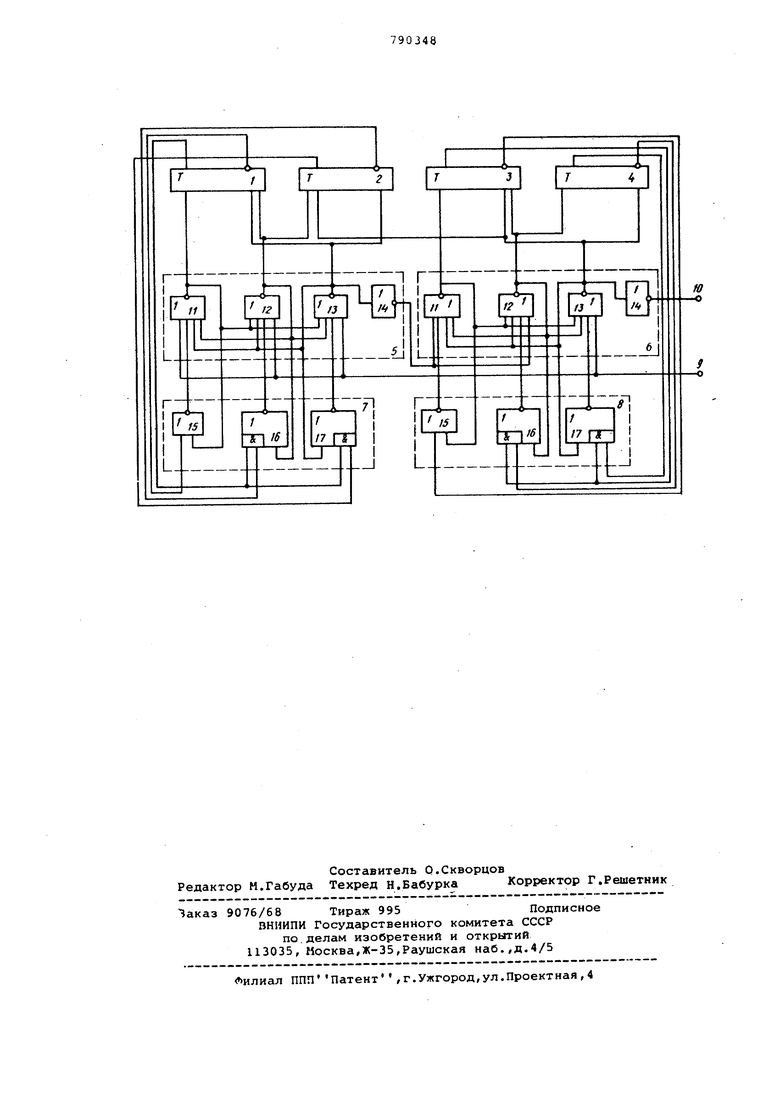

Изобретение относится к импульсной технике и может быть использовано для счета и деления сигналов в различных (преимущественно десятичных) цифровых вычислительных и измерительных устройствах, реализованных средствами интегральной технологии в базисе потенцигшьных логических элементов. Известен десятичный счетчик , содержгиций четыре --RS-трйггёра и блок управления, выходы которого соединены с входами установки и сброса RS-триггеров 11, Наиболее олизким по технической сущности к предлагаемому является десятичный счетчик, содержагчий четы ре RS-триггера и блок управления 2 Недостатком этих десятичных счет чиков является их относительно низ кая надежность. Цель изобретения - повышение над ности десятичного счетчика. Указанная цель достигается тем, что в десятичный счетчик,содержащий четыре RS-триггера и блок управлени введены дополнительный блок управл . ния и первый и второй дешифраторы, первый выход блока управления соеди нен с входом установки первого RS-триггера и первым входом первого дешифратора, первый выход которого соединен с первым входом блока управления, второй выход соединен с первым входом сброса первого RS-триггера, Первым входом установки второго RSтриггера и вторым входом первого дешифратора, второй выход которого соединен с вторым входом блока управления, третий выход которого соединен со вторим входом сброса первого RSтриггера, входом сброса второго Sтриггера и третьим входом первого дешифратора, третий выход которого соединен с. третьим входом блока управления, четвертый вход первого дешифратора соединен с инверсным выходом первого RS-триггера, прямой выход которого соединен с пятым и шестым входами первого дииифратора,ч седьмой вход которого соединен с инверсным выходом второго RS-тpиг epa, прямой выход которого соединен с восьмым входом первого дешифратора, первый выход дополнительного блока управления соединен с входом установки третьего RS-триггера и первым входом второго дешифратора, первый выход которого соединен с первым входом дополнительного блока управления. второй выход которого соединен с первым входом сброса третьего RSтриггера , входом установки четверто го RS-тригГера и вторым входом второ го дешифратора, второй выход которог соединен с вторым входом дополнитель кого блока управления, третий выход которого соединен с вторым входом установки второго RS-триггера, вторы входом сброса третьего RS-триггера входом сброса четвертого RS-триггера и третьим входом второго дешифратора, третий выход которого соединен третьим входом дополнительного блока управления, четвертый вход второ.го дешифратора соединен с инверсным выходом третьего RS-триггера, прямой выход которого соединен с пятым и ше .тым входами второго дешифратора,сед мой вход которого соединен с инверс ным выходом четвертого RS-триггера, мой выход которого соединен с восьмым входом второго дешифратора, четвертый, пятый и шестой входы блока управления соедине ы с входом десятичного счетчика, а четвертый выход блока управления соединен с четвертым и пятым входами дополнител ного блока управления, шестой вход и четвертый выход которого соединены соответственно с входом и выходом десятичного счетчика. Каждый блок управления содержит первый, второй и третий элементы ИЛИ-НЕ (ИНЕ) и инвертор, выход первого элемента ИЛ11-ПЕ (И-НЕ) соединен с первы выходом блока управления и входами второго и третьего элементов ИЛИ-НЕ (И-НЕ), выход второго элемента ИЛИНЕ (И-НЕ) соединен с вторым выходом блока управления и входами первого и третьего элеме 1тов ИЛИ-НЕ (И-НЕ), выход третьего элемента ИЛИНЕ (И-НЕ) соединен с третьим выходом блока управления, входами первого и второго элементов ИЛИ-НЕ (И- ЧЕ) и входом инвертора, выход которого соединен с четвертым выходом блока управления, первый и четвертый входы блока управления соединены с входами первого элемента ИЛИ-НЕ (И-НЕ), второй и пятый входы блока управления соединены с входами второ го элемента ИЛИ-НЕ (И-НЕ), третий и шестой входы блока управления соединены с входами.третьего элемента ЙЛИ-НЕ (И-НЕ). Каждый дешифратор содержит элемент ИЛИ-НЕ (И-НЕ) и первый и второй элементы И-ИЛИ-НЕ первый выход дешифратора соединен с выходом элемента ИЛИ-НЕ (И-НЕ), первый и второй входы которого соединены с первым и четвертым входами дешифратора, второй выход которого соединен с выходом первого элемента И-ИЛИ-НЕ, вход ИЛИ и первый и второй входы.И которого соединены соответственно с вторым, пятым и седьмым входами дешифраора, третий выход которого соединен с выходом второго элемента И-ИЛИЕ; вход ИЛИ и первый и второй входы по И которого соединены соответтвенно с третьим, шестым и восьым входами дешифратора. Структурная схема десятичного счетчика показана на чертеже. Десятичный счетчик содержит чеыре RS-триггера 1,2,3 и 4, блок 5 управления, дополнительный блок 6 управления, первый 7 и второй 8 дешифраторы. Первый выход блока 5 управления соединен с входом установки первого RS-триггера 1 и первым входом первого дешифратора 7, первый выход которого соединен с первым входом блока 5 управления, второй выход которого соединен с первым входом сброса первого RS-триггера 1, первым входом установки второго RSтриггера 2 и вторым входом первого дешифратора 7, второй выход которого соединен с вторым входом блока 5 управления,третий выход которого соединен с вторым входом сброса первого КЗ-триггера 1, входом сброса второго RS-триггера 2 и третьим входом первого дешифратора 7, третий выход которого соединен с третьим входом блока 5 управления. Четвертый вход первого дешифратора 7 соединен с инверсным выходом первого RS-триггера 1, прямой выход которого соединен с пятым и шестым входами первого дешифратора 7, седьмой вход, котррого соединен с инверсным выходом второго RS-триггера 2, прямой выход которого соединен с восьмым входом первого дешифратора 7. Первый выход дополнительного блока б управлениясоединен с входом установки третьего RS-триггера 3 и первым входом второго дешифратора 8, первый выход которого соединен с первым входом дополнительного блока б управления, второй выход которого соединен с первым входом сброса третьего RS-триггера 3, входом установки четвертого RS-триггера 4 и вторым входом второго дешифратора 8, второй выход которого соединен с вторым входом дополнительного блока 6 управления, третий выход которого соединен с вторым входом установки второго RS-триггера 2, вторым входом сброса третьего RS-триггера 3, входом сброса четвертого RS-триггера 4 и третьим входом второго дешифратора 8, третий выход которого соединен с третьим входом дополнительного блока б управления. Четвертый вход второго дешифратора 8 соединен с инверсным выходом третьего КЗ-триггера 3, прямой выход которого соединен с пятым и шестым входами второго дешифратора 8, седьмой вход которого соединен с инверсным выходом четвертого RSтриггера 4, прямой выход которого

соединен с восьмым входом второго дешифратора 8. Четвертый, пятый и шестой входы блока 5 управления соединены с входом 9 десятичного счетчика, а четвертый выход блока 5 управления соединен с четвертым и пятым входами дополнительного блока 6 управления, шестой вход и четвертый выход которого соединены соответственно с входом 9 и выходом 10 десятичного счетчика. Каждый блок 5 и б управления содержит первый 11, второй 12 и третий 13 элементы ИЛИ-НЕ (И-НЕ) и инвертор 14. Выход первого элемента ИЛИ-НЕ (И-НЕ) 11 соединен с первым выходом блока упраления и выходами второго и третьего 13 элементов ИЛИ-НЕ (И-НЕ), выход второго элемента ИЛИ-НЕ (И-НЕ) 12 соединен с вторым выходом блока упраления и входами первого 11 и третьего 13 элементов ИЛИ-НЕ (И-НЕ), выход третьего элемента ИЛИ-НЕ (И-НЕ) соединен с третьим выходом блока управления, входами первого 11 и второго 12 элементов ИЛИ-НЕ (И-НЕ) и входом инвертора 14, выход которого соединен с четвертым выходом блока управления. Первый и четвертый входы блока управления соединены с входами первого элемента ИЛИ-НЕ (И- НЕ) 11, второй и пятый входы блока управления соединены с входами второго элемента ИЛИ-НЕ (И-НЕ) 12, третий и шестой входы блока управления соединены с входами третьего элемента ИЛИ-НЕ (И-НЕ) 13. Каждый дешифратор 7 и 8 содержит элемент ИЛИ-НЕ (И-НЕ) 15, первый 16 и второй 17 элементы И-ИЛИ-НЕ. Первый выход дешифратора соединен с выходом элемента ИЛИ-НЕ (И-НЕ) 15, первый и второй входы которого соединены с первым и четвертым входами дешифратора, второй выход которого соединен с выходом первого элемента И-ИЛИ-НЕ 16, вход ИЛИ и первый и второй входы по И которого соединены соответственно с вторым, пятым и седьмым входами дешифратора, третий выход которого соединен с выходом второго элемента И-ИЛИ-НЕ 17, вход ИЛИ и певый и второй входы по И которого соединены соответственно с третьим, шестым и восьмым входами дешифратора

Десятичный счетчик работает следующим образом.

В исходном состоянии на входе 9 присутствует единичный логический сигнал (высокий уровень), а на прямых выходах RS-триггеров 1,2,3 и 4

1100

При этом

присутствует код

на первых трех выходах блоков 5 и 6 управления поддерживаются нулевые логические сигналы (низкий уровень), .на четвертом входе блока 5 управления - единичный логический сигнал, который и свою очередь поддерживает нулевые логические сигналы на первых

трех выходах блока 6 управления. В taKOM исходном состоянии устройство остается до прихода первого счетного импульса.

Появление на входе 9 нулевого логического сигнала (первого импульса) выэывает изменение состояния блока 5 управления в соответствии с выходными сигналами дешифратора 7. Сигналы с выходов блока 5 управления, поступая на R-входы RS-триггеров 1

o и 2, устанавливают их в нуль, т.е. код на прямых выходах этих триггеров будет 00.На четвертом выходе блока 5 управления появляется нулевой логический сигнал, разрешающий

5 изменение состояния блока 6 управления, который по входу установки устанавливает RS-триггер 3 в единичное логическое состояние. Во время изменения сигналов на выходах RS-триггеров

0 сигналы, поступакицие на входы дешифраторов 7 и 8, могут изменяться на выходах этих дешифраторов. Однако эти кратковременные изменения не нарушают работы устройства, пос5кольку единичный логический сигнал на соответствующем выходе блока управления поддерживает состояние других выходов блока управления на нулевом логическом уровне и, кроме того, не позволяет изменяться сигналу на

0 том выходе дешифратора, который мог бы изменять состояние блока управления. После окончания переходных процессов, вызванных появлением первого .импульса, на прямых выходах RS-триг5геров установится код 0010. В таком состоянии устройство остается до изменения сигнала на входе 9 с нуля в единицу. Второй импульс установит на выходах RS-триггеров

0

Очередной (третий)

1010

код

счетный импульс на входе 9 устанавливает на выходах RS-триггеров аналогично вышеописанному код ОНО и т.д. После девятого импульса код на выходах RS-триггеров будет 0011,

5 Десятый импульс вызывает появление на выходах блоков 5 и 6 управления единичных логических сигналов, которые устанавливают RS-тpиггeF l в

1100

При этом

состояние кода

на выходе 10 формируется выходной импульс деления входной частоты десятый импульс, совпадаюсШй по фазе с десятым входным импульсом. Этот импульс может использоваться для запуска старших декад счетчика при увеличении его разрядности, ири появлении на входе 9 единичного логического сигнала устройства возвращается в исходное состояние.

Формула изобретения

.1. Десятичный счетчик, содержащий четыре RS-трнггера и блок управления о т л и ч а ю.щ и и с я тем, что, с целью повышения надежности, в него введены дополнительный блок управления и первый и второй дешифраторы, первый выход блока управления со единен с входом установки первого RS- триггера и первым входом первого дешифратора, первый выход которого соединен с первым входом блока управ ления, второй выход соединен с первым чходом сброса первого RS-триггера, первым входом установки второго RS-триггера и вторым входом первого дешифратора, второй выход которогр соединен с вторым входом блока управления, третий выход которого соединен с вторым входом сброса первого RS-триггера, входом сброса второго RS-тригггера и третьим входом первого дешифратора, третий выход которого соединен с третьим входом блока управления, четвертый вkoд первого дешифратора соединен с инверсным выходом первого RS-трйггера прямой выход которого соединен с пятым и шестым входами первого дешифратора, седьмой вход которого соединен с инверсным выходом второго RS - триггера, прямой выход которо го соединен с восьмым входом первого дешифратора, первый выход дополнйтел ного блока управления соединен с входом установки третьего RS-тригге ра и первым входом второго дешифратора, первый выход которого соедине с первым входом дополнительного бло ка управления, второй выход которого соединен с первым входом сброса тре его RS-триггера, входом установки четвертого RS-триггера и вторым вхо дом второгхэ дешифратора,второй выход которого соединен с вторым входом дополнительного блока управления, третий выход которого соединен с вторым входом установки второго RSтриггера, вторым входом сброса трет его RS-триггера, входом сброса четвертого RS-триггера и третьим входо второго дешифратора, третий выход которого соединен с третьим входом дополнительного блока управления, четвертый вход второго дешифратора соединен с ин;версным выходом третьего RS-триггера, прямой выход котор го соединен с пятым и шестым входами второго дешифратора, седьмой вход которого соединен с инверсным выходом четвертого RS-триггера, пря мой выход которого соединен с восьмым входом второго дешифратора, четвертый, пятый и шестой входы бло управления соединены с входом десятичного счетчика, а четвертый выход блока управления соединен с четвергым и пятым входами дополнительного лока управления, шестой вход и четертый выход которого соединены сответственно с входом и выходом деятичного счетчика. 2. Десятичный счетчик по п.1, отличающийся тем, что каждый блок управления содержит первый, и третий элементы ИЛИ-НЕ (И-НЕ) и инвертор, выход первого элемента ИЛИ-НЕ (и-НЕ) соединен спервым ,выходом блока управления и входами второго и третьего элементов ИЛИ-НЕ (И-НЕ), выход второго элемента ИЛИ-НЕ (И-НЕ) соединен с вторым выходом блока -управления и входами первого и третьего элементов ИЛИ-НЕ (И-НЕ), выход третьего элемента ИЛИ-НЕ (И-НЕ) соединен с третьим выходом блока управления, входами первого и второго элементов ИЛИ-НЕ (И-НЕ) и входом инвертора, выход которого соединен с четвертым выходом блока управления, первый и четвертый входы блока управления соединены с входами первого элемента ИЛИ-НЕ (И-НЕ), второй и пятый входы блока управления соединены с входами второго элемента ИЛИ-ИЕ (И-НЕ),третий и шестой входы блока управления соединены с входами третьего элемента ИЛИ-НЕ (И-НЕ). 3. Десятичный счетчик по п. 1, отличающийся, тем, что каждый дешифратор содержит элемент ИЛИ-НЕ (И-НЕ) и первый и второй элементы И-ИЛИ-НЕ, первый вход дешифратора соединен с выходом элемента ИЛИНЕ (И-НЕ), первый и рторой входы которого соединены с первым и четвертым входами дешифратора, второй выход которого соединен с выходом первого элемента И-ИЛИ-НЕ, вход ИЛИ и первый и второй входы И которого соединены соответственно с вто{дам, пятым и седьмым входами дешиф атора, третий выход которого соединен с выходом второго элемента И-ИЛИ-НЕ, вход ИЛИ и первый и второй входы по И которого соединены соответственно с третьим, шестым и восьмым входами дешифратора. Источники информации, принятые во внимание при экспертизе 1.Шурыгин И.Т., Новиков Л.Г.Десятичные пересчетные устройства на гибридных интегральных микросхемах, Приборы и системы управления , 1976, 11, с. 44-45. 2. Проектирование радиоэлектронных устройств на интегральных микросхемах. -Под ред. С.Я.Шаца.И., Советское радио , 1976, с. 242, рис. 5.52 (прототип),

Авторы

Даты

1980-12-23—Публикация

1978-12-26—Подача