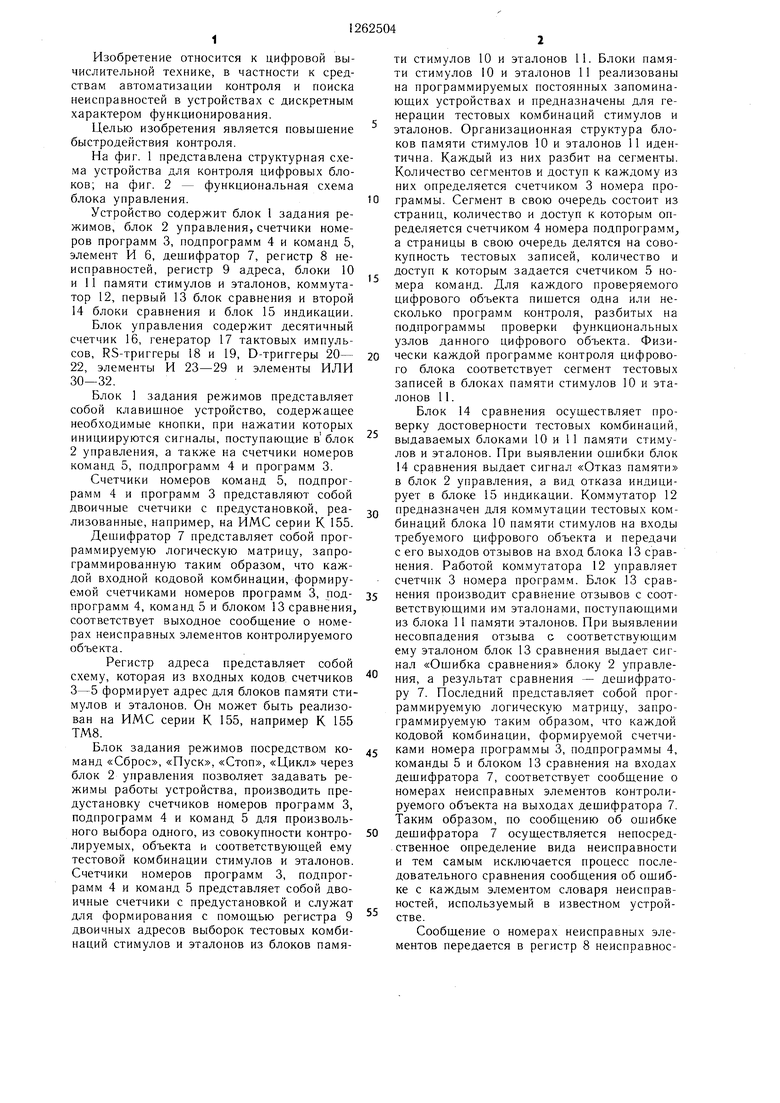

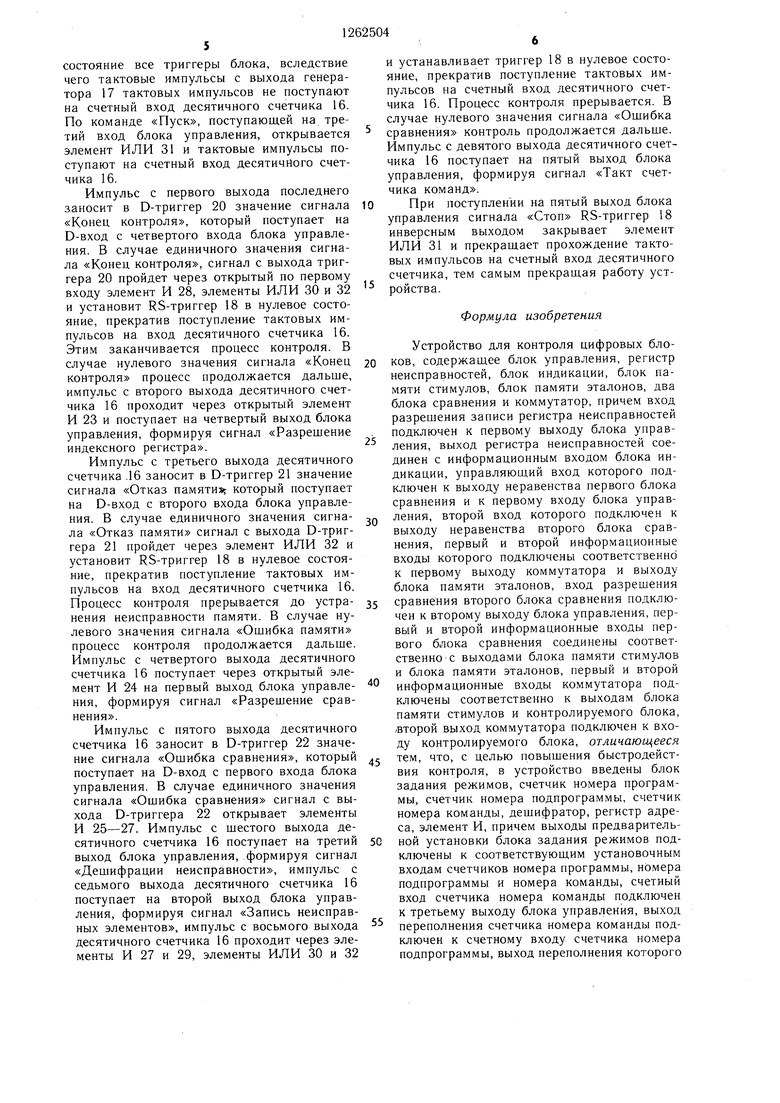

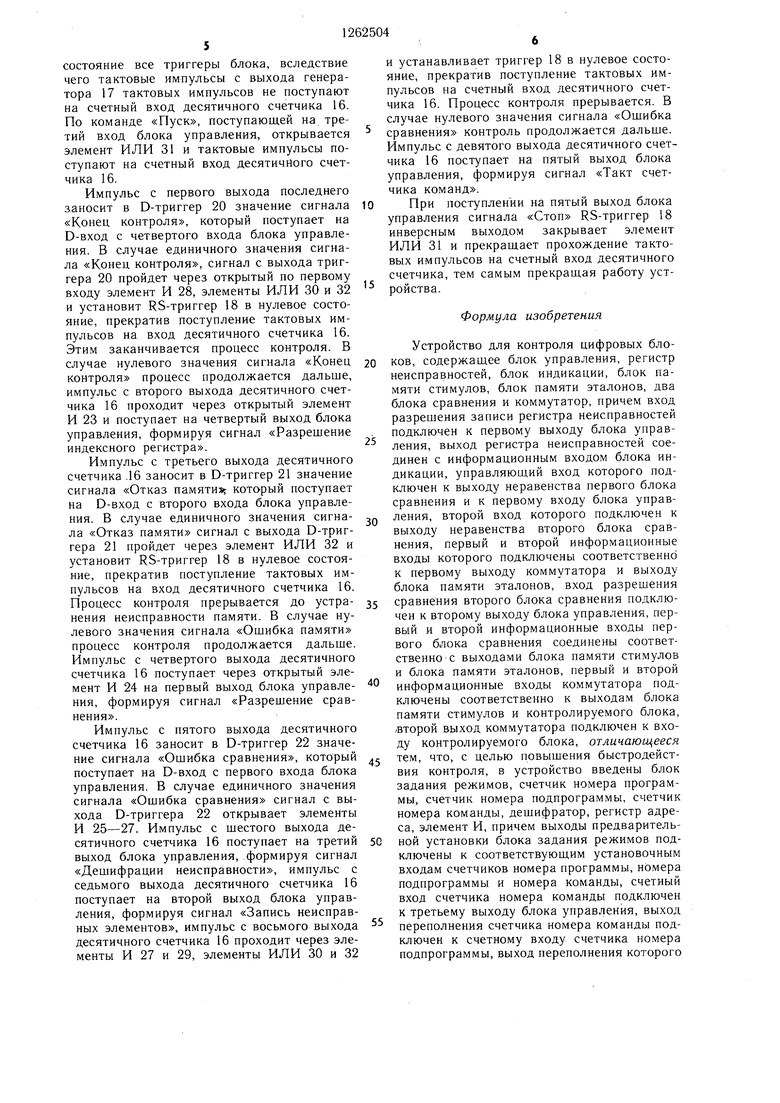

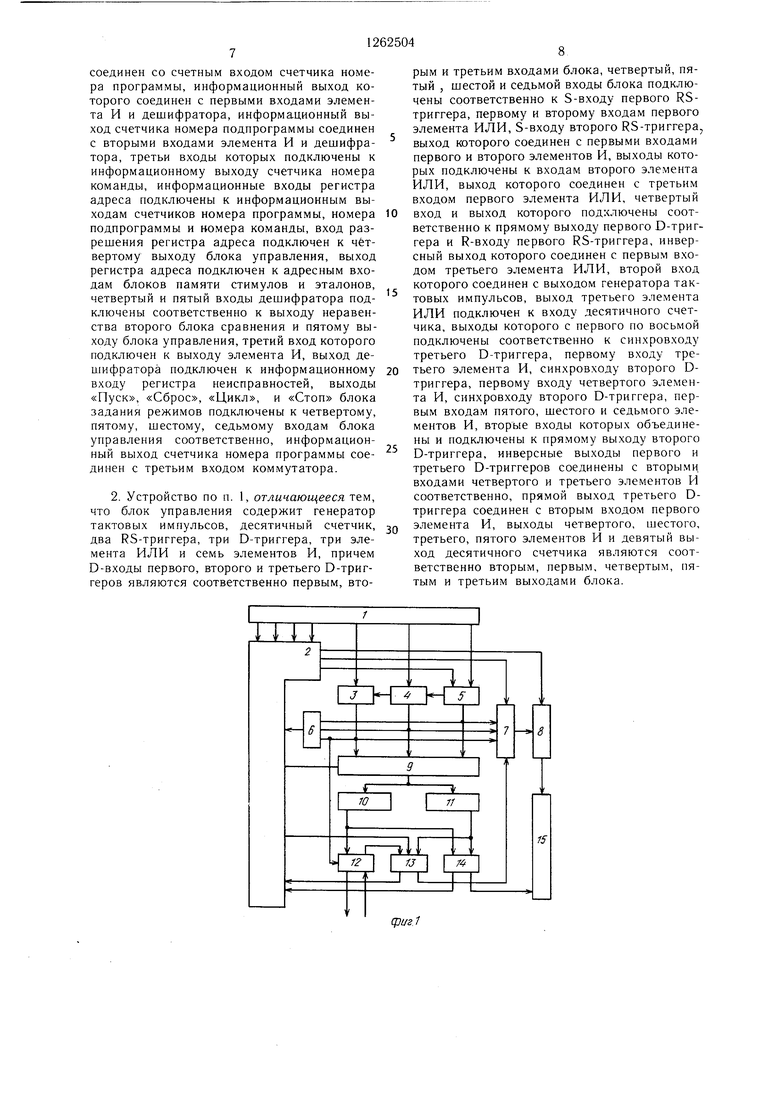

Изобретение относится к цифровой вычислительной технике, в частности к средствам автоматизации контроля и поиска неисправностей в устройствах с дискретным характером функционирования. Целью изобретения является повышение быстродействия контроля. На фиг. 1 представлена структурная схема устройства для контроля цифровых блоков; на фиг. 2 - функциональная схема блока управления. Устройство содержит блок 1 задания режимов, блок 2 управления,счетчики номеров программ 3, подпрограмм 4 и команд 5, элемент И 6, дешифратор 7, регистр 8 неисправностей, регистр 9 адреса, блоки 10 и 11 памяти стимулов и эталонов, коммутатор 12, первый 13 блок сравнения и второй 14 блоки сравнения и блок 15 индикации. Блок управления содержит десятичный счетчик 16, генератор 17 тактовых импульсов, RS-триггеры 18 и 19, D-триггеры 20- 22, элементы И 23-29 и элементы ИЛИ 30-32. Блок задания режимов представляет собой клавишное устройство, содержащее необходимые кнопки, при нажатии которых инициируются сигналы, поступающие в блок 2 управления, а также на счетчики номеров команд 5, подпрограмм 4 и программ 3. Счетчики номеров команд 5, подпрограмм 4 и программ 3 представляют собой двоичные счетчики с предустановкой, peaлизованные, например, на ИМС серии К 155. Дешифратор 7 представляет собой программируемую логическую матрицу, запрограммированную таким образом, что каждой входной кодовой комбинации, формируемой счетчиками номеров программ 3, подпрограмм 4, команд 5 и блоком 13 сравнения, соответствует выходное сообщение о номерах неисправных элементов контролируемого объекта. Регистр адреса представляет собой схему, которая из входных кодов счетчиков 3-5 формирует адрес для блоков памяти стимулов и эталонов. Он может быть реализован на ИМС серии К 155, например К 155 ТМ8. Блок задания режимов посредством команд «Сброс, «Пуск, «Стоп, «Цикл через блок 2 управления позволяет задавать режимы работы устройства, производить предустановку счетчиков номеров программ 3, подпрограмм 4 и команд 5 д.ля произвольного выбора одного, из совокупности контролируемых, объекта и соответствующей ему тестовой комбинации стимулов и эталонов. Счетчики номеров программ 3, подпрограмм 4 и команд 5 представляет собой двоичные счетчики с предустановкой и служат для формирования с помощью регистра 9 двоичных адресов выборок тестовых комбинаций стимулов и эталонов из блоков памяти стимулов 10 и эталонов 11. Блоки памяти стимулов 10 и эталонов 11 реализованы на программируемых постоянных запоминающих устройствах и предназначены для генерации тестовых комбинаций стимулов и эталонов. Организационная структура блоков памяти стимулов 10 и эталонов 11 идентична. Каждый из них разбит на сегменты. Количество сегментов и доступ к каждому из них определяется счетчиком 3 номера программы. Сегмент в свою очередь состоит из страниц, количество и доступ к которым определяется счетчиком 4 но.мера подпрограмм, а страницы в свою очередь делятся на совокупность тестовых записей, количество и доступ к которым задается счетчиком 5 номера команд. Для каждого проверяемого цифрового объекта пишется одна или несколько программ контроля, разбитых на подпрограммы проверки функциональных узлов данного цифрового объекта. Физически каждой программе контроля цифрового блока соответствует сегмент тестовых записей в блоках памяти стимулов 10 и эталонов 11. Блок 14 сравнения осуществляет проверку достоверности тестовых комбинаций, выдаваемых блоками 10 и 11 памяти стимулов и эталонов. При выявлении ошибки блок 14 сравнения выдает сигнал «Отказ памяти в блок 2 управления, а вид отказа индицирует в блоке 15 индикации. Коммутатор 12 предназначен для коммутации тестовых комбинаций блока 10 памяти стимулов на входы требуемого цифрового объекта и передачи с его выходов отзывов на вход блока 13 сравнения. Работой коммутатора 12 управляет счетчик 3 номера программ. Блок 13 сравнения производит сравнение отзывов с соответствуюшими им эталонами, поступающими из блока 11 памяти эталонов. При выявлении несовпадения отзыва с соответствующи.м ему эталоном блок 13 сравнения выдает сигнал «Ошибка сравнения блоку 2 управления, а результат сравнения - дешифратору 7. Последний представляет собой программируемую логическую матрицу, запрограммируемую таким образом, что каждой кодовой комбинации, формируемой счетчиками номера программы 3, подпрограммы 4, команды 5 и блоком 13 сравнения на входах дешифратора 7, соответствует сообщение о номерах неисправных элементов контролируемого объекта на выходах дещифратора 7. Таким образом, по сообщению об ошибке дешифратора 7 осуществляется непосредственное определение вида неисправности и тем самым исключается процесс последовательного сравнения сообщения об ощибке с каждым элементом словаря неисправностей, используемый в известном устройстве. Сообщение о номерах неисправных элементов передается в регистр 8 неисправноетей. Он представляет собой стековый регистр и предназначен для накопления сообщений о номерах неисправных элементов во всех контролируемых объектах с целью последующей визуализации их блоком 15 индикации. Элемент И 6 осуществляет контроль за состоянием счетчиков программ 3, подпрограмм 4 и команд 5. При выявлении состояния счетчиков, соответствующего завершению выполнения последней программы, элемент И 6 выдает в блок 2 управления сигнал «Конец контроля цифровых объектов. Блок 2 управления осуществляет управление и синхронизацию работы всех составных элементов устройства для контроля цифровых блоков. Он принимает из блока 1 команды о режиме работы, из блока 13 сравнения - сигнал «Ошибка сравнения, из блока 14 сравнения - сигнал «Отказ памяти, из элемента И 6 - сигнал «Конец контроля цифровых объектов и выдает тактовые импульсы для счетчика 5 команд, управляющие сигналы «Разрешение индексного регистра, «Сравнение, «Дешифрация неисправности, «Запись неисправных элементов. Устройство работает следующим образом. С блока 1 в блок 2 управления поступает команда «Сброс, осуществляющая установку в исходное состояние всех элементов устройства. При этом счетчики номеров программ 3, подпрограмм 4 и команд 5 обнуляются. Если необходимо произвести проверку не по всем программам, а по какой-то наперед заданной, то производится предварительная запись ее номера с блока 1 в счетчики 3-5. Затем с блока 1 в блок 2 управления подается команда «Пуск устройства в работу. Блок 2 управления выдает сигнал разрешения регистру 9, адрес и двоичный адрес, сформированный из выходных кодов счетчиков 3-5, поступает на шины адреса блоков 10 и 11 памяти стимулов эталонов. Считанные по данному адресу стимулы поступают в коммутатор 12, а эталоны - в блок 13 сравнения. При этом блок 14 сравнения производит проверку достоверности считанных стимула и эталона, а в случае выявления ошибки выдает блоку 2 управления сигнал «Отказ памяти. Блок 2 управления прерывает заданный режим работы и выходит на останов, а блок 15 индикации производит индикацию вида отказа памяти. Если считанные стимул и эталон верны, то заданный режим работы не прерывается. Стимул через коммутатор 12 подается на входы контролируемого объекта, а полученный в результате на выходных контактах отзыв подается через коммутатор 12 на вход блока 13 сравнения. По сигналу «Сравнение блока 2 управления в блоке 13 сравнения производится сравнение полученного отзыва с соответствующи.м ему эталоном. Если отзыв и эталон совпадают, что свидетельствует о правильной отработке стимула контролируемым объектом, то блок 2 управления увеличивает на единицу содержимое счетчика 5 номера команд. Производится считывание из блоков 10 и-11 памяти очередной тестовой комбинации и проверка на отработку ее в контролируемом объекте. Если она отработалась верно, то опять изменяется содержимое счетчика 5 номера команд. Этот процесс будет продолжаться до выполнения последней команды данной подпрограммы. Затем произойдет переход на новую подпрограмму (увеличится на единицу содержимое счетчика 4 номера подпрограмм и обнулится счетчик 5 номера команд и повторится командный цикл проверок). При переборе таким образом всех подпрограмм произойдет переход к исполнению новой программы (увеличится на единицу содержимое счетчика 3 ломера программ и обнулятся счетчики 4 и 5 номеров подпрограмм и команд). При этом коммутатор 12 произведет подключение, если требуется, нового контролируемого объекта. Процесс будет длиться до завершения отработки всех программ и выдачи элементом И 6 блоку 2 управления сигнала «Конец контроля. По этому сигналу блок 2 управления переводит устройство в режим останова, а блок 15 индикации производит индикацию списка проверенных цифровых объектов с указанием годности каждого из них. Если в ходе контроля произойдет несовпадение какого-либо отзыва н эталона, то блок 13 сравнения выдает сигнал «Ошибка сравнения блоку 2 управления, а результат сравнения - сообщение об ошибке - дешифратору 7. При этом блок 2 управления переведет устройство в режим прерывания и выдает сигнал «Дешифрация неисправности дешифратору 7 для определения вида неисправности, т.е. номеров неисправных элементов контролируемого объекта. Номера неисправных элементов записываются в регистр 8 неисправностей с одновременной индикацией в виде номера контролируемого объекта и перечня номеров неисправных элементов в нем блоком 15 индикации. Для продолжения прерванного режима проверок необходимо повторно с блока 1 подать в блок 2 управления команду «Пуск. При необходимости прерывать ход процесса проверок из блока 1 подается команда «Стоп. По команде «Цикл устройство переходит на режим многократной проверки контролируемого объекта. Блок управления работает следующим образом. По команде «Сброс, поступающей с пульта оператора на щестой вход блока управления, приводятся в исходное (нулевое) состояние все триггеры блока, вследствие чего тактовые импульсы с выхода генератора 17 тактовых импульсов не поступают на счетный вход десятичного счетчика 16. По команде «Пуск, поступающей на третий вход блока управления, открывается элемент ИЛИ 31 и тактовые импульсы поступают на счетный вход десятичйого счетчика 16. Импульс с первого выхода последнего заносит в D-триггер 20 значение сигнала «Конец контроля, который поступает на D-вход с четвертого входа блока управления. В случае единичного значения сигнала «Конец контроля, сигнал с выхода триггера 20 пройдет через открытый по первому входу элемент И 28, элементы ИЛИ 30 и 32 и установит RS-триггер 18 в нулевое состояние, прекратив поступление тактовых импульсов на вход десятичного счетчика 16. Этим заканчивается процесс контроля. В случае нулевого значения сигнала «Конец контроля процесс продолжается дальше, импульс с второго выхода десятичного счетчика 16 проходит через открытый элемент И 23 и поступает на четвертый выход блока управления, формируя сигнал «Разрешение индексного регистра. Импульс с третьего выхода десятичного счетчика .16 заносит в D-триггер 21 значение сигнала «Отказ памяти% который поступает на D-вход с второго входа блока управления. В случае единичного значения сигнала «Отказ памяти сигнал с выхода D-триггера 21 пройдет через элемент ИЛИ 32 и установит RS-триггер 18 в нулевое состояние, прекратив поступление тактовых импульсов на вход десятичного счетчика 16. Процесс контроля прерывается до устранения неисправности памяти. В случае нулевого значения сигнала «Ошибка памяти процесс контроля продолжается дальше. Импульс с четвертого выхода десятичного счетчика 16 поступает через открытый элемент И 24 на первый выход блока управления, формируя сигнал «Разрешение сравнения. Импульс с пятого выхода десятичного счетчика 16 заносит в D-триггер 22 значение сигнала «Ошибка сравнения, который поступает на D-вход с первого входа блока управления. В случае единичного значения сигнала «Ошибка сравнения сигнал с выхода D-триггера 22 открывает элементы И 25-27. Импульс с шестого выхода десятичного счетчика 16 поступает на третий выход блока управления, формируя сигнал «Дешифрации неисправности, импульс с седьмого выхода десятичного счетчика 16 поступает на второй выход блока управления, формируя сигнал «Запись неисправных элементов, импульс с восьмого выхода десятичного счетчика 16 проходит через элементы И 27 и 29, элементы ИЛИ 30 и 32 и устанавливает триггер 18 в нулевое состояние, прекратив поступление тактовых импульсов на счетный вход десятичного счетчика 16. Процесс контроля прерывается. В случае нулевого значения сигнала «Ошибка сравнения контроль продолжается дальше. Импульс с девятого выхода десятичного счетчика 16 поступает на пятый выход блока управления, формируя сигнал «Такт счетчика команд. При поступлении на пятый выход блока управления сигнала «Стоп RS-триггер 18 инверсным выходом закрывает элемент ИЛИ 31 и прекращает прохождение тактовых импульсов на счетный вход десятичного счетчика, тем самым прекращая работу устройства. Формула изобретения Устройство для контроля цифровых блоков, содержащее блок управления, регистр неисправностей, блок индикации, блок памяти стимулов, блок памяти эталонов, два блока сравнения и коммутатор, причем вход разрешения записи регистра неисправностей подключен к первому выходу блока управления, выход регистра неисправностей соединен с информационным входом блока индикации, управляющий вход которого подключен к выходу неравенства первого блока сравнения и к первому входу блока управления, второй вход которого подключен к выходу неравенства второго блока сравнения, первый и второй информационные входы которого подключены соответственно к первому выходу коммутатора и выходу блока памяти эталонов, вход разрешения сравнения второго блока сравнения подключен к второму выходу блока управления, первый и второй информационные входы первого блока сравнения соединены соответственно -с выходами блока памяти стимулов и блока памяти эталонов, первый и второй информационные входы коммутатора подключены соответственно к выходам блока памяти стимулов и контролируемого блока, второй выход коммутатора подключен к входу контролируемого блока, отличающееся тем, что, с целью повышения быстродействия контроля, в устройство введены блок задания режимов, счетчик номера программы, счетчик номера подпрограммы, счетчик номера команды, дешифратор, регистр адреса, элемент И, причем выходы предварительной установки блока задания режимов подключены к соответствующим установочным входам счетчиков номера программы, номера подпрограммы и номера команды, счетный вход счетчика номера команды подключен к третьему выходу блока управления, выход переполнения счетчика номера команды подключен к счетному входу счетчика номера подпрограммы, выход переполнения которого соединен со счетным входом счетчика номера программы, информационный выход которого соединен с первыми входами элемента И и дешифратора, информационный выход счетчика номера подпрограммы соединен с вторыми входами элемента И и дешифратора, третьи входы которых подключены к информационному выходу счетчика номера команды, информационные входы регистра адреса подключены к информационным выходам счетчиков номера программы, номера подпрограммы и номера команды, вход разрешения регистра адреса подключен к четвертому выходу блока управления, выход регистра адреса подключен к адресным входам блоков памяти стимулов и эталонов, четвертый и пятый входы дешифратора подключены соответственно к выходу неравенства второго блока сравнения и пятому выходу блока управления, третий вход которого подключен к выходу элемента И, выход де|lVJ/j, 14 DDi/i.o/J, J V.II I СД i Л, шифоатора подключен к информационному ц входу регистра неисправностей, выходы «Пуск, «Сброс, «Цикл, и «Стоп блока задания режимов подключены к четвертому, пятому, шестому, седьмому входам блока управления соответственно, информационный выход счетчика номера программы соединен с третьим входом коммутатора. 2. Устройство по п. 1, отличающееся тем, что блок управления содержит генератор тактовых импульсов, десятичный счетчик, два RS-триггера, три D-триггера, три элемента ИЛИ и семь элементов И, причем D-входы первого, второго и третьего D-триггеров являются соответственно первым, вто. . рым и третьим входами блока, четвертый, пятый , шестой и седьмой входы блока подключены соответственно к S-входу первого RSтриггера, первому и второму входам первого элемента ИЛИ, S-входу второго RS-триггера, выход которого соединен с первыми входами первого и второго элементов И, выходы которых подключены к входам второго элемента ИЛИ, выход которого соединен с третьим входом первого элемента ИЛИ, четвертый вход и выход которого подключены соответственно к прямому выходу первого D-триг,,.гл. tr r-irvn / (1 ГГ I I -ТПЫ Г гера и R-входу первого RS-триггера, инверсный выход которого соединен с первым входом третьего элемента ИЛИ, второй вход которого соединен с выходом генератора тактовых импульсов, выход третьего элемента ИЛИ подключен к входу десятичного счетчика, выходы которого с первого по восьмой подключены соответственно к синхровходу третьего D-триггера, первому входу треlJJ ix,..- -j-- --j1 тьего элемента И, синхровходу второго Dтриггера, первому входу четвертого элемен ,-,л.ч«.т.« т1- 17л- пчг1ЮТГ1ЛТ ГОП/Л Г1Р ЛРНта И, синхровходу второго D-триггера, первым входам пятого, шестого и седьмого элементов И, вторые входы которых объединены и подключены к прямому выходу второго D-триггера, инверсные выходы первого и третьего D-триггеров соединены с вторыми, входами четвертого и третьего элементов И соответственно, прямой выход третьего Dтриггера соединен с вторым входом первого - гэлемента И, выходы четвертого, шecJoгo, третьего, пятого элементов И и девятый выход десятичного счетчика являются соответственно вторым, первым, четвертым, пятым и третьим выходами блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых блоков | 1988 |

|

SU1661768A1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| Устройство для контроля микропроцессорных программных блоков | 1983 |

|

SU1267424A1 |

| УСТРОЙСТВО для КОДИРОВАНИЯ РЕЗУЛЬТАТОВ ПРОГРАММНОГО КОНТРОЛЯ | 1969 |

|

SU249058A1 |

| Устройство для контроля логических узлов | 1983 |

|

SU1129616A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ И ВОССТАНОВЛЕНИЯ ТЕХНИЧЕСКИХ СРЕДСТВ МЕДИЦИНСКОГО НАЗНАЧЕНИЯ | 1992 |

|

RU2072788C1 |

| АВТОМАТИЗИРОВАННАЯ СИСТЕМА КОНТРОЛЯ ПАРАМЕТРОВ ЭЛЕКТРОННЫХ СХЕМ | 1991 |

|

RU2106677C1 |

| Устройство для контроля электрических параметров цифровых узлов | 1984 |

|

SU1260974A1 |

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1753474A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1247898A2 |

Изобретение относится к цифровой вычислительной технике, в частности к средствам автоматизации контроля и поиска неисправностей в устройствах с дискретным характером функционирования. Изобретение позволяет повысить быстродействие устройства за счет непосредстве П1Ого определения дешифратором вида неисправности, исключая тем самым процесс последовательного сравнения сообщения об ошибке с каждым элементом словаря неисправностей. Блок задания режимов задает режимы работы устройства, производит предустановку счетчиков номеров программ, подпрограмм и команд для произвольного выбора одного из контролируемых объектов и соответствуюших ему тестовых комбинаций стимулов и эталонов, которые генерируются реализованными на программируемых постоянных запоминаюш их устройствах блоками памяти стимулов и эталонов. Второй блок сравнения проверяет достоверность тестовых комбинаций и при выявлении ошибки выдает сигнал «Отказ памяти в блок управления, вид отказа индицируется в блоке индикации. Коммутатор подключает тестовые комбинации с блока памяти стимулов на входы требуемого цифрового объекта, а отзывы с его выходов подключает на вход первого блока сравнения. При выявлении несовпадения отзыва с соответствующим ему эталоном первый блок сравнения выдает сигнал «Ошибка сравнения блоку управления, а результат сравнения дешифратору. Последний представляет собой программируемую логичес( кую матрицу, запрограммированную таким образом, что каждой кодовой ко.мбинации, (Л формируемой счетчиками номеров программ, подпрограмм, команд и первым блоком сравнения, на входах дешифратора, соответствует выходное сообщение о номерах неисправных элементов контролируемого объекта, т.е. дешифратор непосредственно определякэ ет вид неисправности и тем самым исключает процесс последовательного сравнения о: сообщения об ошибке с каждым элементом 1чЭ словаря неисправностей, используемый в ОТ устройстве по прототипу. 1 з.п.ф-лы, 2 ил.

| Устройство для контроля цифровых блоков | 1975 |

|

SU607218A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля логическихблОКОВ | 1978 |

|

SU813430A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-10-07—Публикация

1985-04-17—Подача