f

Изобретение относится к импульсной технике, Б частности к счетчикаи импульсов и может быть использовано для счета и деления последовательностей двоичных сигналов в различ- 5 ных цифровых вычислительных и измерительных системах.

Известен десятичный счетчик с естественным порядком счета, построенный по схеме с параллельным переносомЮ на основе RS-триггеров со схемами управления,:образующих четыре однотактных счетчика Т-триггера с шестью потенциальными логическими элементами И, ИЛИ }. 15

Недостатки этого десятичного счет чика - относительно низкое быстродействие и значительные аппаратурные затраты.

Известен также счетчик, содержа- 20 щий четыре RS-триггера и десять логических элементов, инверсный выход первого RS-триггера соединен с перBfcJM входом первого логического элемента, выход которого соединен с пер-25 вым входом второго логического элемента, выход которого соединен с входом установки первого RS-триггера, инверсный выход второго RS-триггера сог. динен с первым разрешающим входом 30

третьего логического элемента, выход которого соединен с первым входом че вертого логического элемента, выход которого соединен с входом установки второго й5 Триггера инверсный вход третьего RS-триггера соединен с первым разрешающим входом пятого логического элемента, выход которого соединен с первым входом шестого логического элемента, выход которого соединен с входом установки третьего RS-триггера, выход седьмого логического элемента соединен с первым входом восьмого логического элемента, выход которого соединен с входом установки четвертого RS-триггера, а вторые входы второго, четвертого, шестого и восьмого, а также первый вход девятого логических элементов соединены с входом десятичного счетчика 2j .

Недостатком этого десятичного счетчика являетсябтносительно низкоебыстродействие.

: Цель изобретения - повышение быст:родействия.

Поставленная цель достигается тем что в десятичном счетчике, содержащем четыре RS-триггера и десять логи ческих элементов, инверсный выход ,

rii pBoro RS-триггера соединен с пер.;.гм а ходом первого логического; эле;.: :г1та, выход которого соединен с пер BtJM входом второго логического элеус-нта, выход которого соединен с вхо д6« устанЬвкй первого RS-триггера, инверсный выход второго RS-триггёра

соединен с первым разрешающим входом

третьего логического элемента,- выход которого соединен с первым входом , четвертого логического элемента, выход которого соединен с входом уста y6SiKH Stbp6V6;.RS-триггера, инверсный выходтретьего RS-триггбра соединен с первым разрешающим входом пятого логического элемента,выход которого соединен с первым входом шестого логического элемента, выход крторого соединен с входом установки третьего RS-тригтера, выход седь- - - його логического элемента соедйней С первым входом восьмого логического элемента, выход которого соединен с входом установки четвертого RS-триггера,а вторые входы второго, .четвертого, шестого и восьмого

а также первый вход девятого логических элементов соединены с входом десятичного счетчика, выход девятого логического элемента соединен с выходом десятичного счетчика, входом сброса четвертого RS-tpniгера, первым входомсброса первого R S - т рй ггё|)а, третьими;: входалш в торо т я- ё Пё1 тогб Ж):ШёШ и входом десятого логического элемён„ „ 1ШШзГ а с 81г Г1: ёдайШ т входом девятого логического элемента, третий вход которого соединен с четвертыми вхЪдамИ втйрого и 4etEiej)Tdго логических элементовJ .э ретьим входом шестого логического элемента,

выходомвосьмбг р 10гиче :;кого эле мента и входом седьмого логического элемента, первый разрешающий вход которого соединей с nepBtavT pat peiuaющим входом десятого ;логическрго элемента, вторыми разрешайяцимй входами третьегои; пятого лргическИх;элементов и пряглом выходсэм первого RS-триггера, вход устаиовки которого соединен с вторым BXOJJOM nepSo o логического .элемента, пятым входом четвертого логического элемента, четвертцм входом шестого логического элемента, третьим входом вОсбМОго логического элемента и четвертым входом дев1ятрго логического элемента, выход чётв ёртЬго логического элемента соединен с вто|мым входом сброса первого RS-триггера, входом третьего логического элемента, пятыми входами второго и шестого ло1гических элементов и четвертым входом рсьмого логического элемента, выход ко торого соединен с тр етьим s fi&S/t

сброса первого RS-триггёра, первымвходом сброса второго RS-триггера и входом сброса третьего RS-тipИfгepal п1рямой вйхЪд которого соединён с вторым разрешающим входом седьмого логического элемента, третий разре шающий вход которого соединён с пряNbJM выходом второго RS-триггера, и третьим разрешающим входом пятого логического элемента, вход которого соединен с шестыми входами второго и четв ртого логических элементов, пятьом входом восьмого логического элемента, выходом шестого, логического элемента, а также с четвертым входом сброса первого RS-триггера и вторым входом сброса второго RS-триггера, а прямой и инверсный выходы четвертого RS-TpKrrepa соединены соответственно с вторым разреша- i ющим входом десятого логического элемента и третьим разрешающим входом третьего логического элемента.

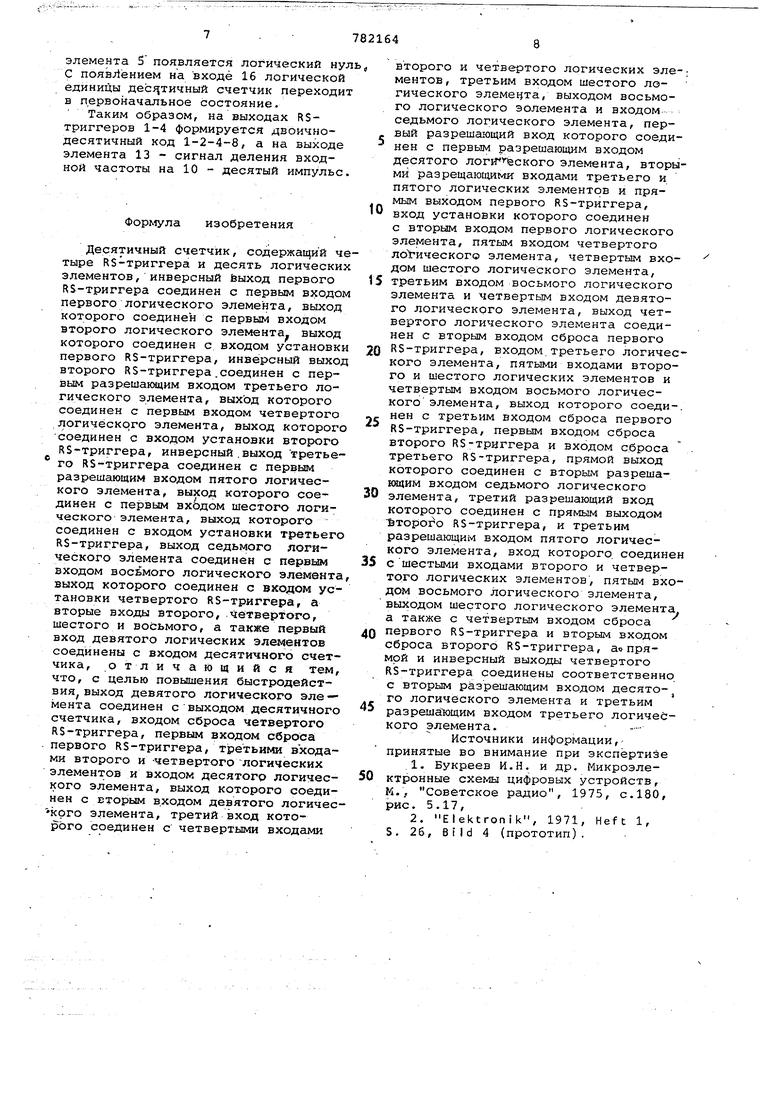

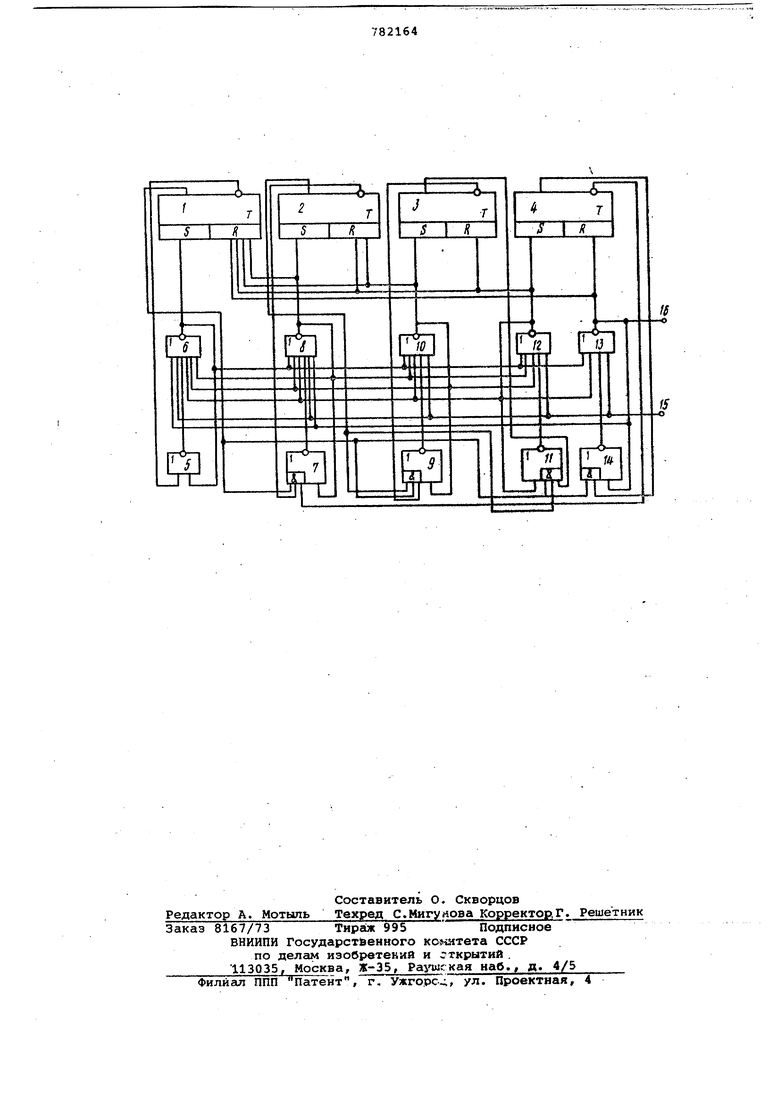

На чертеже показана структурная

0 схема десятичного счетчика.

Десятичный счетчик содержит четыре RS-триггера 1-4 и десять логических элементов 5-14, инверсный выход первого RS-триггера 1 соединен с первым входом пёрёого логического элемента 5/выход которого соединен с первым входом-второго логического элемента б,выход которого соединен с входом установки первого RS-триггера,

Q инверсный выход второго RS-триггера

2соединен с первнлм разрешающим входом третьего логического элемента 7, выход которого соединен с первым входей четй1ёргЪгб.йотичёс1 б го элемента

с 8, выход которого соединен с входом установки второго RS-триггера 2, инверсный выход третьего RS-триггера

3сЬединен с первым разрещающим входом пятого логического элемента 9 выход которого соединен с первым

Р входом шестого логического элемен/та 10,выход которого соединение входЬмустйнбвки третьего RS-триггера 3, вйход седьмого логического элемента 1 соединён с первым входом восьмого

5 логического элемента 12, выход которого соединен с входом установки четвертого RS-триггера 4, а вторые входы ВТОРОГО б, четвертого 8, шестого 10 и восьмого 12, а также первый

0 вход девятого 13 логических элеменtOB соединены с входом 15 десятичного счетчика, выход девятого логического элемента 13 соединен с выходом 16 десятичного счетчика, входом сброса четвертого RS-триггера 4, первьм входом сброса первого RS-триггера 1, третьими входами второго б и четвертого 8 логических элементов и входом десятого логического элемента 14, выход которого

Q соединен с вторым входом девятого лоГ-ического элемента 13, третий вход которого соединен с четвертыми входг1МИ б и четвертого 8 логических Элементов, третьим входом шестого

5 10 логйчеШЬго элемента, выходом

восьмого логического элеме нта 12 и входом седьмого 11 логического элемента, первый разрешающий вход которого соединен с первым разрешающим входом десятого логического элемента 14, вторыми разрешающими входами третьего 7 и пятого 9 логических элементов и прямым выходом первого RS-триггера 1, вход установки которого соединен с вторым входом первого логического элемента 5, пятым входом четвертого логического элемента 9, четвертым входом шестого логического элемента 10, третьим входом восьмого логического элемента 12 и четвертым входом девятого логического элемента 13, выход четвертого логического элемента 8 соединен с вторым входом сброса первого триггера 1, входом третьего логического элемента 7, пятыми входами второго 6 и шестого 10 логических элементов и четвертым входом восьмого логического элемента 12, выход которого соединен с третьим входом сброса первого RS-триггера 1, первым входом сброса второго RS-триггера 2 и входом сброса третьего RS-триггера 3, прямой выход которого соединен с в.торЕлм разрешающим входом седьмого логического элемента 11, третий разрешающий вход которого соединен с прямым выходом второго RS-триггера 2 и третьим разрешанхдим входом пятого логического элемента 9, вход которого соединен с шестыми входами второго б и четвертого 8 логических элементов, пятым входом восьмого логического элемента 12, выходом шестого логического элемента 10, а также с четвертым входом сброса первого триггера 1 и вторым входом сброса второго RS-триггвра 2, а прямой и инверсный выходы четвертого RS-триггера 4 соединены соответственно с вторым разрешающим входом десятого логического элемента 14 и третьим разрешающим входом третьего логического элемента 7.

Десятичный счетчик работает следующим образом.

Пусть в исходном состоянии .RS-триггеры 1-4 находятся в нуле,т. на их прямых выходах присутствует логический нуль (низкий потенциал), а йа инверсных выходах - логическая единица (высокий потенциал)и пусть на выходе 15 сигнал равен логической единице. Тогда на выходах элементов 6, 8, 10 и 12 и на выходе элемента 13 присутствует логический нуль. Так как RS-триггеры 1-4 в состоянии логического нуля, т,о сигнлы с прямых выходов этих триггеров устанавливают на выходах элементов 7, 9, 11 и 14 логические единицы и только ни выходе элемента 5 устанавливается логический нуль, так

тгак на вход этого элемента подаетсЛ логическая единица с инверсного выхода RS-триггера 1. Таким образом, определено распределение эначенни логических сигналов в устройстве в начальный момент времени. При изменении значения сигнёьпа на входе 16 с единицы в нуль элементы 6, 8, 10 и 12 устанавливаются в первое состояние (1000). Логическая единица с выхода элемента б, во-первых, блокирует последующие возможные изменения сигналов на выходах элементов 5 и 13, во-вторых, устанавливает RS-триггер 1 в единичное логическое состояние. При этом на прямом

s выходе этого триггера появляется логическая единица, а на инверсном выходе - логический нуль, который не меняет состояния элемента 5, так как этот элемент заблокирован логической единицей с выхода элемента

0 6, а, единица с пятого выхода первого RS-триггера 1, поступая на вход разрешения элемента 7, устанавливает на выходе элемента 7 логический нуль. В таком состоянии устройство

5 остается до следующего изменения сигнала на входе 15. Появление на входе 15 логической единицы устанавливает на выходе элементов 6, 8, 10 и 12 внОвь код (0000). При этом на

0 выходе элемента 5 появляется логическая единица. Состояния остальных элементов схемы не изменяются до очередного изменения на входе 15. Второй импульс (нуль) на входе 15

5 устанавливает второе состояние (0100). Единица с выхода элемента

8блокирует изменение состояния элемента 7 и устанавливает RS-триггеры

1и 2 соответственно в логическое состояние нуль и единицу. При этом

0 единица с инверсного выхода триггера

2устанавливает нуль на выходе элемента 5. Состояние выхода элемента 7 не меняется, хотя на входе разрешения этого элемента появляется

5 логический нуль с выхода R5-TpHrrepa 1. Новое изменение сигнала на входе 15 с логического нуля в логическую единицу вновь устанавливает код (0000). Далее работа устройства

0 происходит аналогично описанному: 3-й импульс устанавливает код на выходе RS-триггеров 1-4 код (1100), 4-ый - (0010), 5-ый - (1010), 6-оЯ(0110), 7-6й - (1110), 8-й (0001),

5 9-ый - (1001). Перед 10-ым импульсом на выходах элементов 5j 7,

9и 11 появляется логическая едини- ца, а на выходе элемента 14 - логический нуль. Поэтому с приходои 10-го импульса срабатывает элемент 9, ло0гическая единица с его выхода блокирует элемент 14, блокирует срабатывание элементов б и 8 и устанавливает триггеры 1 и 4 в нулевое логическое состояние. При этом на выходе

5

элемента 5 появляется логический нуль, С появ/1ёнием на входе 16 логической единицы деспотичный счетчик переходит в первоначальное состояние.

Таким образом, на выходах RSтриггеров 1-4 формируется двоичнодесятичный код 1-2-4-8, а на выходе элемента 13 - сигнал деления входной частоты на 10 - десятый импульс.

Формула изобретения

Десятичный счетчик, содержащий четыре RS-триггера и десять логических элементов, инверсный йыход первого RS-триггера соединен с первым входом первого логического элемента, ВЕЛХОД которого соединен с первым входом второго логического элемента, выход которого соединен с входом установки первого RS-триггера, инверсный выход второго RS-триггера .соединен с первым разрешающим входом третьего логического элемента, выход которого соединен с первым входом четвертого логического элемента, выход которого соединен с входом установки второго RS-триггера, инверсный .выход третьего RS-триггера соединен с первым разрешающим входом пятого логического элемента, выход которого соединен с первым входом шестого логического элемента, выход которого соединен с входом установки третьего RS-триггера, выход седьмого логического элемента соединен с первым входом восьмого логического элемента, выход которого соединен с входом установки четвертого RS-триггера, а вторые входы второго, четвертого, шестого и восьмого, а также первый вход девятого логических элементов соединены с входом десятичного счетчика, отличающийся тем, что, с целью повышения быстродействия, выход девятого логического эле - мента соединен с выходом десятичного счетчика, входом сброса четвертого RS-триггера, первым входом сброса первого RS-триггера, третьими входами второго и -четвертого логических элементов и входом десятого логического элемента, выход которого соединен с вторым входом девятого логическрго элемента, третий вход которого соединен с четвертыми входами

второго и четвертого логических элементов, третьим входом шестого логического элемента, выходом восьмого логического эолемента и входом седьмого логического элемента, первый разрешающий вход которого соединен с первым разрешающим входом десятого логй ёского элемента, вторыми разрещающими входами третьего и пятого логических элементов и прямым выходом первого RS-триггера, вход установки которого соединен с вторым входом первого логического элемента, пятым входом четвертого ло гического элемента, четвертым входом шестого логического элемента, третьим входом восьмого логического элемента и четвертьгм входом девятого логического элемента, выход четвертого логического элемента соединен с вторым входом сброса первого RS-триггера, входом.третьего логического элемента, пятыми входами второго и шестого логических элементов и четвертым входом восьмого логического элемента, выход которого соедииен с третьим входом сброса первого RS-триггера, первым входом сброса второго RS-триггера и входом сброса третьего RS-триггера, прямой выход которого соединен с вторым разрешаКйдим входом седьмого логического элемента, третий разрешающий вход которого соединен с прямым выходом TopoiPo RS-триггера, и третьим разрешающим входом пятого логического элемента, вход которого, соедине с шестыми входами второго и четвертого логических элементов, пятым входом восьмого логического элемента, выходом шестого логического элемента а также с четвертым входом сброса первого RS-триггера и вторым входом сброса второго RS-триггера, аопрямой и инверсный выходы четвертого RS-триггера соединены соответственно с вторым разрешающим входом десятого логического элемента и третьим разреша1ощим входом третьего логического элемента.

Источники информации, принятые во внимание при экспертизе

1.Букреев И.Н, и др. Микроэлектронные схемы цифровых устройств, К., Советское радио, 1975, с.180, рис.5.17,

2. Elektronik, 1971, Heft 1, S. 26, Btld 4 (прототип).

S Т К

5Т ff

5

S I к I

ГТЛ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения направления и угла поворота вращающегося объекта | 1991 |

|

SU1786441A1 |

| Десятичный счетчик | 1978 |

|

SU790348A1 |

| Счетчик импульсов с цифровой индикацией | 1984 |

|

SU1231602A1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ РТСМ | 2008 |

|

RU2390930C2 |

| Счетчик импульсов с цифровой индикацией | 1986 |

|

SU1336230A1 |

| Измеритель напряжения прикосновения и тока короткого замыкания | 1990 |

|

SU1764002A1 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2386998C1 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ И ВЫЧИТАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2389064C1 |

| Интегрирующий преобразователь напряжения в код | 1986 |

|

SU1410275A1 |

| Делитель частоты импульсов | 1979 |

|

SU845292A1 |

Авторы

Даты

1980-11-23—Публикация

1978-12-18—Подача