(54) УСТРОЙСТВО ДЛЯ РЕШЕНИЯ УРАВНЕНИЙ ВИДА

Устройство относится к области вычислительной техники и может быть использовано в специализированных вычислительных системах и измерителы ых преобразователях.

Известно устройство, содержащее регистр, группу элементов И, сумматор, элемент И, элемент задержки и квадратор.

Недостаток зтого устройства заключается в его чрезмерной cлoжIiOcти, обусловленной наличием в его составе квадратора 1.

Наиболее близкое по своей супцтости к предлагаемому устройству-устройство.содержащее две схемы сравнения, дешифратор, две группы элементов И, группу элементов ИЛИ, реверсивный счеттак, сумматор, два элемента И и два триггера 2.

Недостатком такого устройства является его сложность.

Другой недостаток устройства - низкое быстродействие, обусловленное тем, что процесс решения уравнений в известном устройстве происходит в два этапа: на первом этапе формируется квадрат одного из аргумен1 -. х2

У

тов, а на втором - результирующее выражение.

Цель изобретения - повышение быстродействия устройства.

Поставленная цель достигается тем, что в устройство, содержащее первую и вторую группы элементов И, первый элемент ИЛИ, деш1 фратор, введены блок суммирова1гая, блок вычитания, суммир аощий счетчик, вычитающий , второй элемент ИЛИ. При

10 этом выходы блока суммирования и блока вычитания соедш1ены соответственно со входами суммирующего и вычитающего счет1шков, группа выходов суммирующего счетчика через соответствующие элементы И первой груп15пы - с группой входов первого элемента ИЛИ, вход которого подключен к выходу cyм шpyющeгo счегшка. Группа выходов вычитающего счетчика соединена с группой входов дешифратора непосредственно и через

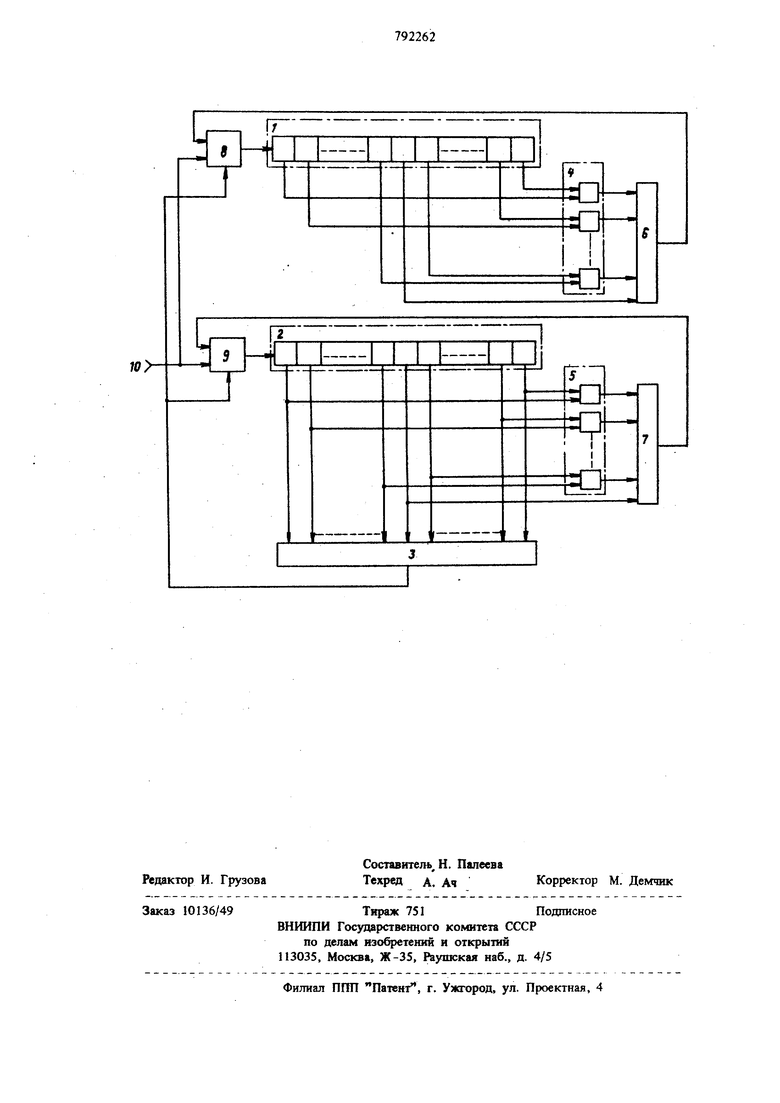

20 вторую группу элеме1гтов И с гр ппой входов второго элемента ИЛИ. Вход дещифратора под1сяючен к вььходу вычитающего счетчика и ко входу второго элемента ИЛИ. 3 выходы первого и второго элементов ИЛИ соединены соответственно с первыми входами блока суммирования и блока вычитания, вторые входы которых подключены ко входу тактовых импульсов устройства, а их третьи входы - к выходу дешифратора. На чертеже представлена схема устройства. Оно содержит суммирующий счетчик 1, вычитающий счетчик 2, дещифратор 3, две группы элементов И 4 и 5, элементы ИЛИ 6 и 7, блок 8 суммирования и блок 9 вычитания, вход 10 устройства. Счетчики 1 и 2 являются t разрядными. Процесс вьпшсления в устройстве начинается в момент записи числа х в счетчик 2 и числа у в счетчик 1. При этом дещифратор 3 открьгоает ключевые элементы, расположенные в блоках 8, 9, и тактовые импульсы с входа 10 устройства поступают на входы счетчиков 1 и 2. В момент перехода счетчика 2 в нулевое состояние дешифратор 3 закрывает ключевые элементы, расположен1п 1е в блоках 8, 9, и процесс вычисления в устройстве заканчивается. Таким образом, в процессе вычисления про исходит изменение «тела в счетчике 1 от у до 2 , а в счетчике 2 - от х до О, где т; - решение уравнения. Повышение быстродействия достигается бла годаря тому, что результат решения уравнения формируется в устройстве в один этап, а в прототипе - в два этапа, причем одного этапа вычисления в данном устройстве не больше времени вышсления первого этапа в прототипе. 2 Формула изобретения Устройство для рещения уравнений вида у, содержащее первую и вторую гругаты элементов И, первый элемент ИЛИ, дещифратор, отличающееся тем, что, с целью повышения быстродействия, в него введены блок суммирования, блок вычитания, суммирующий счетчик, вычитающий счетчик, второй элемент ИЛИ, причем выходы блока суммирования и блока вычитания соединены соответственно со входами суммкрующего и вычитающего счетчиков, группа выходов суммирующего счетчика соединена через соответствующие элементы И первой группы с группой входов первого элемента ИЛИ, вход которого подключен к выходу суммирующего счетчика, группа выходов вычитающего счетчика соединена с группой входов дешифратора непосредственно и через вторую группу элементов И с группой входов второго элемента ИЛИ, вход дешифратора подключен к выходу вычитающего счетчика и ко входу второго элемента ИЛИ, выходы первого и второго элементов ИЛИ соединены соответственно с первыми входами блока суммирования и блока вычитания, вторые входы которых подключены ко входу тактовых импульсов устройства, а их третьи входы к вы.ходу дешифратора. IИсточники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 392494, кл. G 06 F 7/38, 1971. 2.Авторское свидетельство СССР № 453697, кл. G 06 F 15/32, 1973.

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство | 1978 |

|

SU742930A1 |

| Арифметическое устройство | 1977 |

|

SU674016A1 |

| Цифровой фильтр с многоуровневой дельта-модуляцией | 1988 |

|

SU1587624A1 |

| Цифровое устройство для вычисления показательных функций | 1974 |

|

SU633015A1 |

| Генератор векторов | 1985 |

|

SU1300541A1 |

| Устройство для вычисления квадратного корня | 1981 |

|

SU1008736A1 |

| Устройство для сравнения чисел с допусками | 1986 |

|

SU1413620A1 |

| Генератор векторов | 1981 |

|

SU1010646A1 |

| Устройство для вычисления факториала | 1985 |

|

SU1297071A1 |

| Генератор векторов | 1986 |

|

SU1361613A1 |

Авторы

Даты

1980-12-30—Публикация

1978-12-04—Подача