(21)4139919/24-24

(22)21.10.86

(46) 30.07.88. Бюл. № 28 (72) Е,Я. Ваврук

(53)681.325.5(088.8)

(56)Авторское свидетельство СССР № 783790, кл. G 06 F 7/04, 1979.

Авторское свидетельство СССР № 1119005, кл. С 06 F 7/04, 1983.

(54)УСТРОЙСТВО ДЛЯ СРАВНЕНИЯ ЧИСЕЛ С ДОПУСКАМИ

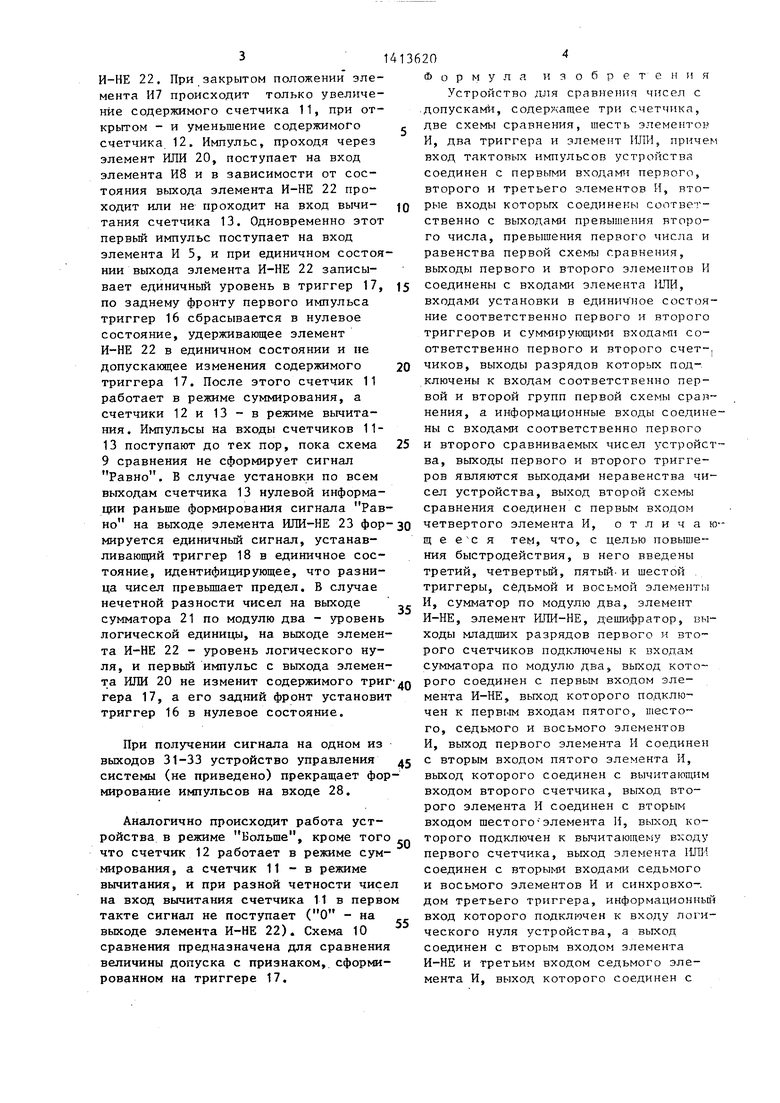

(57)Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах контроля и регулирования для сравнения разности двух чисел с третьим числом. Цель изобретения -- повышение быстродействия. Устройство содержит элементы И 1-8, схемы сравнения 9

и 10, счетчики 11-13, триггеры 14-19, элемент ИЛИ 20, сумматор 21 по модулю два, элемент И-НЕ 22, элемент ИШ1-НЕ 23, дешифратор 24, шины 25, 26 соответственно первого и второго сравниваемых чисел, входы 27 задания величины допуска, вход 28 тактовых импульсов, выходы 29 и 30 неравенства чисел, выходы 31-33 результата сравнения соответственно в пределах допуска, превышения величины допуска и равенства величине допуска. Сущ-i- ность изобретения заключается в организации суммирования и вычитания на первом и втором счетчиках, что ускоряет процесс приближения чисел, и в оперативном формировании признака превьшения величины допуска. Изобретение позволяет повысить быстродействие устройства. 1 ил. 1 табл.

«

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для автоматического контроля генератора случайных чисел | 1982 |

|

SU1038942A1 |

| Устройство для сравнения чисел | 1981 |

|

SU993247A1 |

| Устройство для контроля параллельного кода на четность | 1987 |

|

SU1413632A1 |

| Устройство для сравнения числа с допусками | 1984 |

|

SU1160392A1 |

| Устройство для обнаружения и исправления ошибок | 1985 |

|

SU1368995A1 |

| Генератор случайных процессов | 1984 |

|

SU1309021A1 |

| Вероятностный интегратор | 1980 |

|

SU900283A1 |

| Устройство для сравнения двоичных кодов | 1990 |

|

SU1784965A1 |

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1619278A1 |

| Устройство для многоканальной записи-воспроизведения информации | 1985 |

|

SU1273992A1 |

зг зг аз t t f

11413620

Изобретение относится к автомати-.

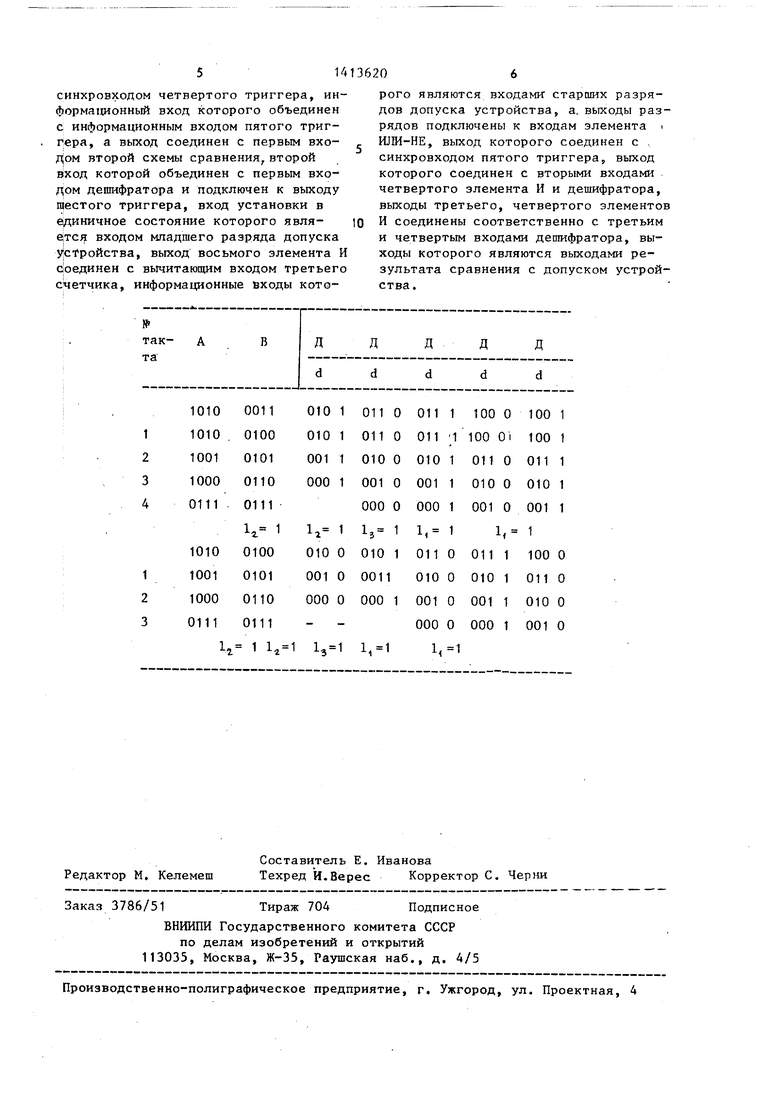

лах допуска 1. аЬ V а-b C d, равенство чисел величине допуска- 1, а-Ь С числа превышают величину допуска i 1 a-bv abcd,гдe 1 г соответст-. вующие выходы, a,b,c,d - сигналы соответственно на первом, втором, третьем, четвертом входах дешифратора.

Приведенные зависимости подтверждают числовые значения D величины допуска (см. таблицу).

Устройство работает следующим образом.

По сигналу начальной установки (не приведен) триггеры 14,15,17,18 устанавливаются в нулевое состояние, триггер 16 - в единичное состояние. В счетчики 11 и 12 по входам 25 и 26 записываются первое и второе число, в счетчик 13 - старшие п-1 разряды числа допуска, в триггер 19 - младший разряд числа допуска (сигналы записи не приведены). Схема 9 сравнения, входы которой соединены с вы- На сумматоре 21 по модулю два фор-25 ходами счетчиков 11 и 12, производит

ке и вычислительной технике и может быть использовано в системах контроля и регулирования для сравнения раз- с ности двух чисел с третьим числом.

Цель изобретения - повьш1ение быстродействия.

На чертеже приведена функциональная схема предложенного устройства. ю

Устройство содержит элементы И 1-8, схемы 9 и 10 сравнения, счетчики 11- 13, триггеры 14-19, элемент ИЛИ 20, сумматор 21 по модулю два, элемент И-НЕ 22, элемент ИЛИ-НЕ 23, дешифратор 5 24, входы 25,26 соответственно первого и второго сравниваемого числа, входы 27 задания величины допуска, вход 28 тактовых импульсов, выходы 29 и 30 неравенства чисел, выходы 31-33 результата сравнения соответственно в пределах допуска, превьшения величины допуска и равенства величине допуска,

20

мируется признак четности (логический О) и нечетности (логическая 1) разности чисел. При наличии признака нечетности содержимое меньшего из с

сравнение первого и второго чисел и формирует на одном из трех своих выходов сигнал. При равенстве чисе открывается элемент ИЗ, соединенн

сравниваемых чисел (в счетчике 11 или 30 с выходом Равно схемы 9 сравне12) в первом такте работы увеличивается на + 1 , а в следующих тактах одновременно идет увеличение меньшего и уменьшение большего из сравниваемых чисел. При наличии признака четности -jj идет одновременное увеличение меньшего и уменьшение большего числа, сразу начиная из первого такта работы (прихода первого импульса по шине 28), например:

40

45

А 1010, ,,, г, +1 2x0011j + 0001.J

Такт работы,А В №

010100011

110100100

210010101

310000110

401110111

В счетчик 13 записываются старшие п-1 разряды величины допуска, в триггер 19 - младший разряд. Счетчик 13 постоянно работает в режиме вычитания, которое происходит только в момент од новременной работы счетчиков 11 и 12 в разных режимах (вычитания и сложения) . Дешифратор 24 работает согласно следукипим зависимостям: числа в предесравнение первого и второго чисел и формирует на одном из трех своих выходов сигнал. При равенстве чисел открывается элемент ИЗ, соединенный

j

0

ния. Если число, занесенное в счетчик 11, больше числа в счетчике 12, то открывается элемент И2, соединенный с выходом Больше схемы 9 сравнения, и если число в счетчике 11 меньше, то открывается элемент И1, соединенный с вьпсодом Меньше схемы 9 сравнения.

Мпадшие разряды счетчиков 11 и 12 поступают на входы сумматора 21 по модулю два, и если числа в c ZBi- чиках одинаковой четности (оба ч -т- ные или нечетные), на его BBIXJ; у формируется уровень логичес г о ну- 5 , которьй формирует на выходе элемента И-НЕ уровень логической единицы (на выходе триггера 16 в это время - единичньй уровень). При разных четностях чисел в счетчиках 11 и 12 на выходе сумматора 21 - 1, на выходе элемента И-НЕ 22 - О.

Импульсы с входа 28 тактовых импульсов поступают на первые входы элементов И 1-3, и если открыт, например, элемент И 1, то импульсы переходят на вход суммирования счетчика 11 и на вход элемента И7, которьй может быть закрыт или открыт в зависимости от состояния выхода элемента

0

5

И-ИЕ 22. При закрытом положении элемента И7 происходит только увеличение содержимого счетчика 11, при открытом - и уменьшение содержимого счетчика 12. Импульс, проходя через элемент ИЛИ 20, поступает на вход элемента И8 и в зависимости от состояния выхода элемента И-НЕ 22 проходит или не проходит на вход вычи- танин счетчика 13. Одновременно этот первый импульс поступает на вход элемента И 5, и при единичном состоянии выхода элемента И-НЕ 22 записывает единичный уровень в триггер 17, по заднему фронту первого импульса триггер 16 сбрасывается в нулевое состояние, удерживающее элемент И-НЕ 22 в единичном состоянии и не допускакщее изменения содержимого триггера 17. После этого счетчик 11 работает в режиме суммирования, а счетчики 12 и 13 - в режиме вычитания. Импульсы на входы счетчиков 11- 13 поступают до тех пор, пока схема 9 сравнения не сформирует сигнал Равно. В случае установки по всем выходам счетчика 13 нулевой информации раньше формирования сигнала Рав35

но на выходе элемента ШШ-НЕ 23 фор-зо четвертого элемента И, отличаю- мируется единичньй сигнал, устанавливающий триггер 18 в единичное состояние, идентифицирующее, что разница чисел превьшает предел. В случае нечетной разности чисел на выходе сумматора 21 по модулю два - уровень логической единицы, на выходе элемента И-НЕ 22 - уровень логического нуля, и первый импульс с выхода элемента ИЛИ 20 не изменит содержимого триг-д0 гера 17, а его задний фронт установит триггер 16 в нулевое состояние.

При получении сигнала на одном из выходов 31-33 устройство управления j системы (не приведено) прекращает формирование импульсов на входе 28.

щ е е с я тем, что, с целью повышения быстродействия, в него введены третий, четвертый, пятый-и шестой триггеры, седьмой и восьмой элементы И, сумматор по модулю два, элемент И-НЕ, элемент ИЛИ-НЕ, дешифратор, выходы младших разрядов первого и второго счетчиков подключены к входам сумматора по модулю два, выход которого соединен с первьм входом элемента И-НЕ, выход которого подключен к nepBi iM входам пятого, шестого, седьмого и восьмого элементов И, выход первого элемента И соединен с вторым входом пятого элемента И, выход которого соединен с вычитаюпц м входом второго счетчика, выход второго элемента И соединен с вторым входом шестого- элемента И, выход которого подключен к вычитающему входу первого счетчика, выход элемента 1Ш1 соединен с вторыми входами седьмого и восьмого элементов И и синхровхо-. дом третьего триггера, информационный вход которого подключен к входу логического нуля устройства, а выход соединен с вторым входом элемента И-НЕ и третьим входом седьмого элемента И, выход которого соединен с

Аналогично происходит работа устройства в режиме Больше, кроме того что счетчик 12 работает в режиме суммирования, а счетчик 11 - в режиме вычитания, и при разной четности чисел на вход вычитания счетчика 11 в первом такте сигнал не поступает (О - на выходе элемента И-НЕ 22). Схема 10 сравнения предназначена для сравнения величины допуска с признаком, сформированном на триггере 17.

Формула изобретения

Устройство для сравнения чисел с .допусками, содер чагцее три счетчика, две схемы сравнения, шесть элементов И, два триггера и элемент ИЛИ, причем вход тактовых импульсов устройства соединен с первыми входами первого, второго и третьего элементов И, вторые входы которых соединены соответственно с выходами превышения второго числа, превышения первого числа и равенства первой схемы сравнения, выходы первого и второго элементов И соединены с входами элемента ИЛИ, входами установки в единичное состояние соответственно первого и второго триггеров и суммирующими входам соответственно первого и второго счет-, чиков, выходы разрядов которых подключены к входам соответственно первой и второй групп первой схемы срап- нения, а информационные входы соединены с входами соответственно первого и второго сравниваемых чисел устройства, выходы первого и второго триггеров являются выходами неравенства чисел устройства, выход второй схемы сравнения соединен с первьм входом

5

о четвертого элемента И, отличаю- 0

j

0

5

щ е е с я тем, что, с целью повышения быстродействия, в него введены третий, четвертый, пятый-и шестой триггеры, седьмой и восьмой элементы И, сумматор по модулю два, элемент И-НЕ, элемент ИЛИ-НЕ, дешифратор, выходы младших разрядов первого и второго счетчиков подключены к входам сумматора по модулю два, выход которого соединен с первьм входом элемента И-НЕ, выход которого подключен к nepBi iM входам пятого, шестого, седьмого и восьмого элементов И, выход первого элемента И соединен с вторым входом пятого элемента И, выход которого соединен с вычитаюпц м входом второго счетчика, выход второго элемента И соединен с вторым входом шестого- элемента И, выход которого подключен к вычитающему входу первого счетчика, выход элемента 1Ш1 соединен с вторыми входами седьмого и восьмого элементов И и синхровхо-. дом третьего триггера, информационный вход которого подключен к входу логического нуля устройства, а выход соединен с вторым входом элемента И-НЕ и третьим входом седьмого элемента И, выход которого соединен с

синхровходом четвертого триггера, информационный вход которого объединен с информационным входом пятого триггера, а выход соединен с первым входом второй схемы сравнения, второй вход которой объединен с первым входом дешифратора и подключен к выходу шестого триггера, вход установки в единичное состояние которого являемся входом младшего разряда допуска yjcfpoAcTsa, выход восьмого элемента И соединен с вычитающим входом третьего счетчика, информационные входы кото

рого являются входамк старших разрядов допуска устройства, а. выходы разрядов подключены к входам элемента i ШМ-НЕ, выход которого соединен с , синхровходом пятого триггера, выход которого соединен с вторыми входами четвертого элемента И и дешифратора, выходы третьего, четвертого элементов И соединены соответственно с третьим и четвертым входами дешифратора, выходы которого являются выходами результата сравнения с допуском устройства.

Авторы

Даты

1988-07-30—Публикация

1986-10-21—Подача