Изобретение относится к из(./г9ритепьной и вычислительной технике и может быть использовано в геофизической и радиолокационной аппаратуре в качестве специализированных вычислителей 0ля обработки измерительной информации,

Известны ци4ровые устройства для извлечения квадратного корня, содержащие параллельный сумматор, дешифратор счетчик циклов и сдвигающий регистр tlj. Эти устройства не позволяют возводить числа в целую и дробную степень. Известны также устройства дпя вычисления степенных функций, содержашие реверсивный счетчик циклов, триггер, вентиль, генера;тор импульсов, множительно-делительное устройство и суммирующий счетчик. Наиболее близким к изобретению техническим решением является цифровое устройство для вычисления показательных функций, содержащее дешифратор, первые два вхо- да которого соединены с шинами показателя, степени, счетчик, выход которсио соединен с первой выходной шиной и через два последовательно соединенных сумматора - со второй выходной шиной и первыми входами элементов И первой группы, входная шина устройства соединена с первыми входами элементов И второй группы и через третью группу элементов И - со вторыми входами второго сумматора 2, Однако оно характериэуетхя невозможностью возводить числа в . пюбую степень, спожностью, cxeNfbi, сложностью организации циклов вычислений, недостаточным быстродействием и значительными погрешностями.

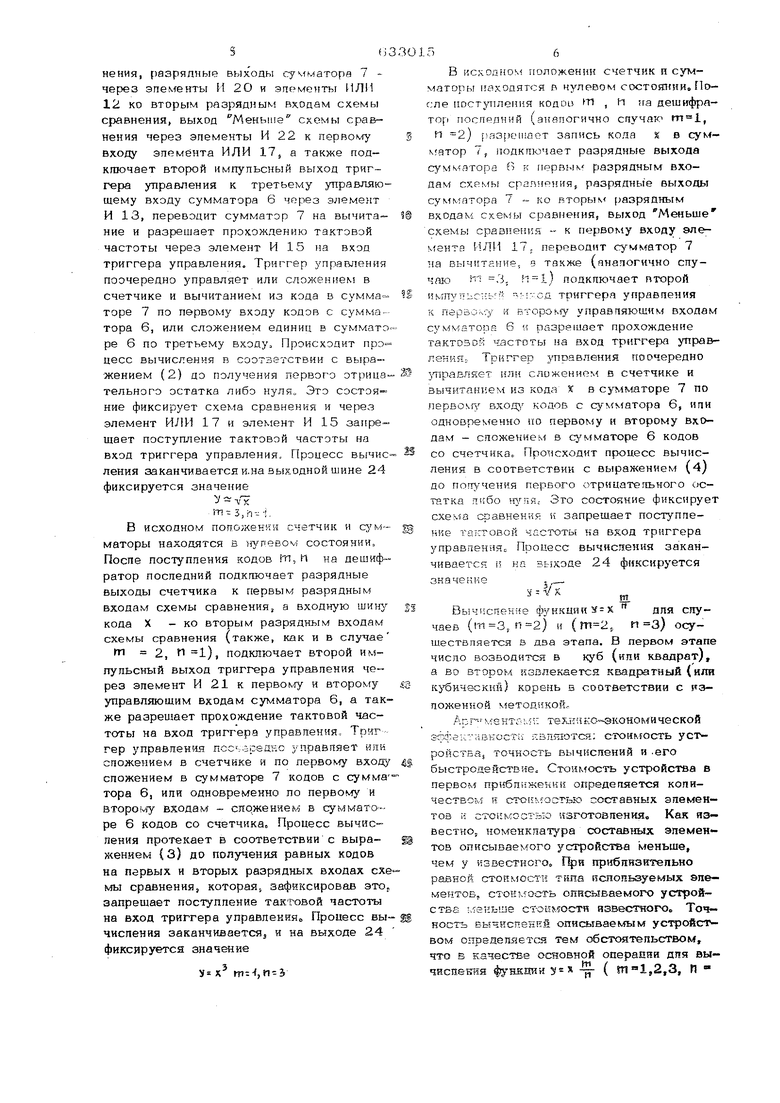

Целью изобретения является расширение класса решаемых задач, заключающего в вычислении показательных функций с дробным показателем степени. В описываемом устройстве это достигается тем, что оно содержит элементы И, эяементы ИЛИ, блок сравнения, элементы И четвертой группь и триггер, вход через первый элемент И соединен с тактовой шиной, первый выход триггера соединен со входом счетчика я управляющим входом второго сумматора, второй выход триггера соединен с первыми входами второго и

третьего элементов И, выходы эпементов И первой и второй группы через поспедоватег1Ь ю соединенные группы первых элементов ИЛИ, блок сравнения, группу вторых-элементов ИЛИ в четвертую группу элементов И подключены к выходам счетчике, первый выход блока сравнения через Гюспедоватепьно соединенные четвертый элемент И и третий элемент ИЛИ, а второй выход блока сравнения через третий элемент ИЛИ подкшочены к третьему выходу дешифратора и второму входу первого элемента И, первый выход дешифратора соединен со вторыми входами элементов И второй и четвертой групп, второй выход дешифратора соединен со вторыми входами первой н третьей групп элементов И, вторыми входами четвертого и пятого элементов И, третий и четвертый выходы дешифратора через второй и третий элементы И подключены соответственно к управляющим входам первого сумматора, выходы которого через пятый элемент И соединены со вторыми входами группы вторых элементов ИЛИ„

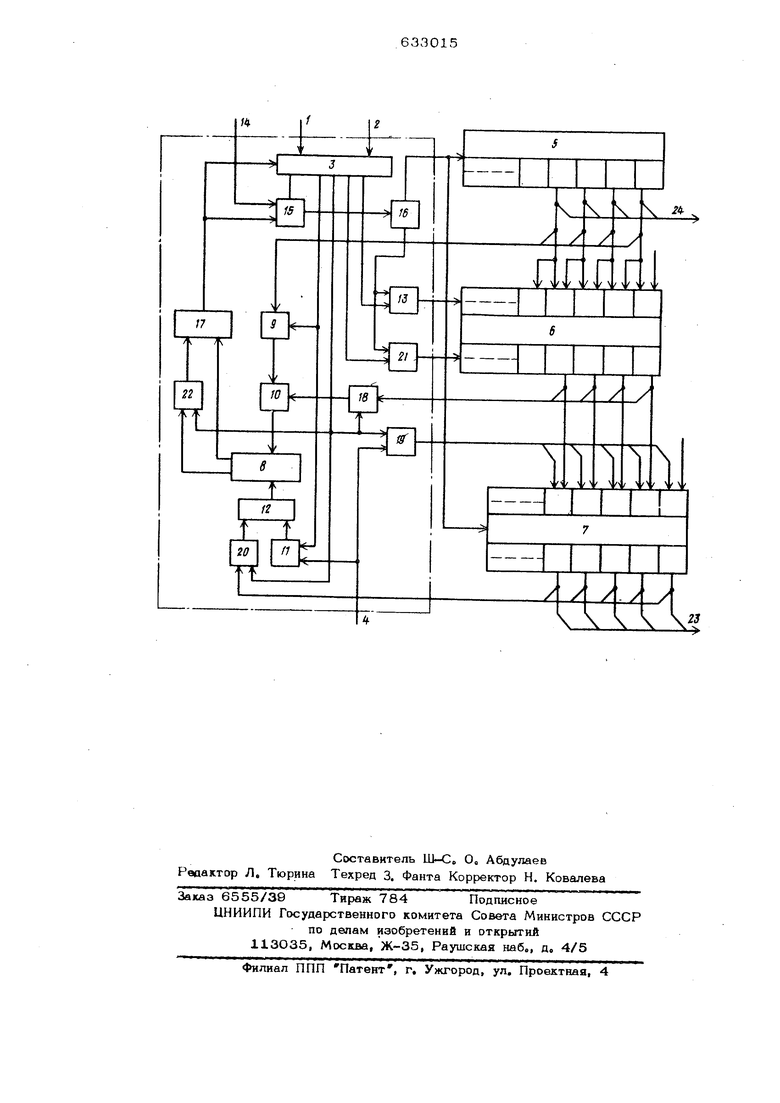

На чертеже представдена функциональная схема описываемого устройства

Оно содержит входные шины 1 и 2 по казателей степени tn к п соответственно, дешифратор 3s входную шину 4s счетчик 5, первый и второй параппельные сумматоры 6 и, 7, схему .8 cpaBHekHHj четвертую группу элементов И 9 группу вторых элементов ИЛИ 10 вторую груп пу элементов И 11, группу первых элементов ИЛИ 12, второй элемент И 13, тактовую шину 14, первый элемент И 15 триггер 16,,. третий элемент ИЛИ 17, пятый элемент И 18, третью группу элеметов И 19j перзую группу элементов И 2О, третий элемент И 21 и четвертый элемент И 22,

Устройство реализует апгоритмЫ; основанные на решении в целых числах уравнений и неравенств. Суть их различных значений тип состоит в следутошем

- к

fri - 1 . Г: - S

-1

,

m - -f, n 2 X

Первый при котором

) 3::;4ЛО;- 2Яс;ТСЯв

з,пг 3 ( + 1

(S.)

()-f($0.

-t ,п-э C4)

ir-f

.

N -первый номер, при котором неравентво (4) выполняется

т-3, п-2 :yrVF

Вычисление данной функции реализуется посредством последовательного выполнения рассмотренных выше операций (3) и (2),

т-2, п-3 y-4G

Вычисление этой функции реализуется посредством последовательного выполнения рассмотренных выше операций (l) и (4).

Принцип действия устройства рассмотрим в изложенном выше порядке для различных значений Ж и П . , hr-f

В исходном положении счетчик 5 и сумматоры 6 и 7 находятся в нулевом состояни. После поступления кодов т и f на дешифратор 3 последний подключает разрядные выходы счетчика 5 через элементы И 9 ИЛИ 10 и первым разрядным входам схемы 8 сравнения, входную шину 4 - через элементы И 11 и ИЛИ 12 ко вторым разрядным входам схемы 8 сравнения, разрешает прохождение тактовой частоты через элемент И IS на вход триггера 16, а также подключает второй импульсный выход триггера управления к третьему управляющему входу сумматора 6 через элемент И 13 Триггер управления поочередно управляет, или сложением в счетчике 5 и по первому входу сложением в сумматоре 7 кодов с сумматора 6, или по третьему входу сложением единиц в сумматоре 6. Происходит процесс вычисления в соответствии с выражением (l) до получения равных кодов на первых и вторых разрядных входах схемы 8 сравнения, которая, зафиксировав это через элемент ИЛИ 17 и элемент И 15, запрешает поступление тактовой частоты на вход триггера управления Процесс вычисгшния заканчивается, и на выходной шине 23 фиксируется значение

:( х n , исходном положении счетчик и сумматоры ка;;:с.к;тся s н падвоы состоянии. После поступления кодов in , И на дешифратор последний разрешает запись кода X через элементы И 19 по вторым раз- рядным входам в сумматор 7, подключает разрядные выходы сумматора 6 через

элементы И 18 и элементы ИЛИ 1О к первым разрядным входам схемы сравнения, разрядные выходы сумматора / через sne.vfeHTbi И 2О и эпементы ИЛИ 12 ко вторым разрядным входам схемы сравнения, выход Меньше схемы сравнения через эпементы Н 22 к первому входу элемента ИЛИ 17, а также подкшочает второй импульсный выход триггера утхравления к третьему управляю щему входу сумматора 6 через элемент И 13, переводит сумматор 7 на вычитание и разрешает прохождению тактовой частоты через элемент И 15 на вход триггера управления. Триггер управления поочередно управляет или сложением в счетчике и вычитанием из кода в сумматоре 7 по первому входу кодов с сумматора 6, или сложением единиц в суммато ре б по третьему входу Происходит прэ цесс вычисления в соответствии с выражением (2) до получения первого отрица тельного остатка либо нуля„ Это состояние фиксирует схема сравнения и через элемент ИЛИ 17 и элемент И 15 запрещает поступление тактовой частоты на вход триггера управления. Процесс вычис ления заканчивается и.на выходной шине 24 фиксируется значение s-n-i. В исходном поп.оженйн счетчик и сумматоры находятся в нупевоч. состоянии, Поспе поступления кодов №, и на дешифратор последний подключает разрядные выходы счетчика к первым разрядным входам схемы сравнения, а входную шин кода X - ко вторым разрядным входам схемы сравнения (также, как и в случае m 2, п 1), подключает второй импульсный выход триггера управления через элемент И 21 к первок-гу и второму управляющим входам сумматора 6, а так же разрешает прохождение тактовой частоты на вход триггера управления. Триг гер управления псс..5реако управпяет йлн сложением в счетчике и по первому входу сложением в сумматоре 7 кодов с сумма тора 6, или одновременно по первому и BTopois входам - спожение л в суммато-ре 6 кодов со счетчика. Процесс вычисления протекает в соответствии с выражением (3) до получения равных кодов на первых и вторых разрядных входах схе мы сравнения, которая зафиксировав это запрещает поступпение тактовой частоты на вход триггера управления Процесс вы чиспения заканчиваетсЯэ и на выходе 24 фиксируется значение у- f m:-f,ri-3 о6 в искойном положении счетчик п сумматоры находятся в нулевом состоялиш После поступления кодой fTl , И на дешифратор поспрдний (анапогично спучато т 1, П 2) fsaGjieMiiaoT запись кода % в сум- s;aTop 7j подключает разрядные выхода сумматора в к первык разрядным входам схемы срапиения, разрядные выходь сумматора 7 - ко втopы разрядным BxDAa vi сравнения, выход Меньше схемы сраапения -- к первому входу элемента И;ЛИ 17. переводит сумматор 7 на вычитанле, s также (аналогично случаю И 3, h i) подключает второй импупьСГЬй триггера управпения rt парволгу Л BTOpoKiy управляющим входам сум.;аторЕ 6 н разрешает прохождение тактовой ъчстогы на вход триггера управлениЯг Триггер зправления поочередно втравляет млн сложенне%-( в счетчике и вычитанием из кода X в сумматоре 7 по nepBovi) входз кодов с сук{ штора 6, или одновре 1енно по nepBONsy и второму входам - сложением в сумматоре 6 кодов со счетчика Происходит процесс вычисления в соответствии с выражением (4) до погг1чения первого отрицательного остатка Это состояние фиксирует схема сравнения ii запрещает поступление TaicTOBof част-оты на вход триггера управпенняс Процесс вычисления заканчивается п на выходе 24 фиксируется значенгие. Bbi4iicneH;ie функции s-x дпя случаев (, ) и (, ) осушествпяется а два этапа. В первом этапе число возводится в куб (ипи квадрат), а во втором извлекается квааратный (или к бич-ескнй) корень Б соответствии с изложенной ччетодгткой А с г-- Кге ктй V.5 i: т-е..ки ко-экономи че ской зффекглВЕОст;; лвпяются; стоимость устройстЕа точность вычислений и .его быстродействие. Стоикюсть устройства в первом пр :бп ;жекки опредепяется копичествсгч и сто И ,ОСТЬЮ составных эпемен- тов : стоимостью изготовпения Как известно, номенклатура сюставных элементов описываемого устройства меньше, чем у известного При приблизительно равной стоимостн тнпа испогеьзуемых элементов, сток,5оегь описываемого устройстве ;. ст-опмостн известного Точность вычиспенЕЙ описываемым устройством опредегыется тем обстоятепьством, что в качестве основной операпии дпя вы- чиспекйя ф5нк|тии -рр ( 1П 192,3, П

1,2,З) используется одна арифметическая операция (сложение). Известно, что погрешность сумматора при выполнении этой операции равна О и имеется топько погрешность кодирования, В известном устройстве основную операцию перемножения сомножителей выполняет множительно- делительное устройство, где источником погрешности является суммирующий интегратор; здесь же происходит и накоппение погрешности. Быстродействие устройства определяется временем, необходимым для вычисления степенной функции, а для реализации этого вычисления достаточно выполнять только X операций еложения (вычитания), так кик слагаемые получаются сразу в параллельном коде на выходе сумматора Быстродействие известного устройства определяется временем, необходимым на операции сумм,рования, временем для записи последовательного кода X в счетчик и временем счета счетчиками. Для вычисления функций в нем только операций суммиро.вания необходимо выполнять 2 Х,так как суммирование параллельных кодов в реверсивных счетчиках осуществляется последовательно.

Таким образом быстродействие описываемого устройства значительно повы- шается по сравнению с известным..

Формула изобретения

Цифровое устройство дпя вычисления показательных функций, содержащее дешифратор, первые два входа которого соединены с шинами показателя степени, счетчик, выход которого соединен с первой Выходной шиной и через два последовательно соединенных сумматора - со второй выходной шиной и первыми входами элементов И первой группы, входная шина устройства соединена с первыми

входами элементов И второй гдгппы и.

через третью группу элементов И - со вторыми входами второго сумматора, о т пичаюшееся тем, что, с целью расширения класса решаемых задач, заключающегося в вычислении показательных функций с дробным показателем стелени, устройствосодержит элементы И, элементы ИЛИ, блок сравнения, элементы И четвертой группы и триггер j вход которого через первый элемент И соединен с тактовой шиной, первый выход триггера соединен со входом счетчика и управляющим входом второго сумматора, второй выход триггера соединен с первыми входами второго и третьего элементов И, выходы элементов И первой и второй группы через последовательно соединенные группу первых элементов ИЛИ, блок сравнения, группу вторых элементов ИЛИ и четвертую группу элементов И подключены к выходам счетчика, первый выход блока сравнения через последовательно соединенные четвертый элемент И и третий элемент ИЛИ, а второй выход блока сравнения через третий элемент ИЛИ подключены к третьему входу дешифратора и второму входу первого элемента И, первый выход дещифрато- ра соединен со вторыми входами элементо И второй и четвертой групп, второй выход дешифратора соединен со вторыми входами первой и третьей групп элементов И, вторыми входами четвертого и пятого элементов И, третий и четвертый выходы дешифратора через второй и третий элементы И подключены соответственно к управл51юшим входам первого сумматора, выходы которого через пятый элемент И соединены со вторыми входами группы : вторых элементов ИЛИ.

Источники информации, принятые во внимание при экспертизе:

1,Авторское свидетельство СССР № 239665, кл. Q 06 F 7/38, 1970.

2.Авторское свидетельство СССР № 491129, кл. G 06 F 7/38, 1072,

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой функциональный преобразователь (варианты) | 1981 |

|

SU1015375A1 |

| Устройство для моделирования систем массового обслуживания | 1986 |

|

SU1399756A1 |

| Устройство для моделирования систем массового обслуживания | 1989 |

|

SU1652979A1 |

| Функциональный преобразователь | 1983 |

|

SU1108442A1 |

| Устройство для вычисления функции | 1984 |

|

SU1180884A1 |

| Устройство для поворота вектора | 1983 |

|

SU1132285A1 |

| Система программного управления технологическими процессами | 1989 |

|

SU1681297A1 |

| Устройство для вычисления функции @ =2 @ | 1981 |

|

SU1057942A1 |

| Специализированный процессор | 1981 |

|

SU1023339A1 |

| АРИФМЕТИКО-ЛОГИЧЕСКОЕ УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ, ВЫЧИТАНИЯ И УМНОЖЕНИЯ ЧИСЕЛ ПО МОДУЛЮ | 2019 |

|

RU2711051C1 |

Авторы

Даты

1978-11-15—Публикация

1974-03-28—Подача