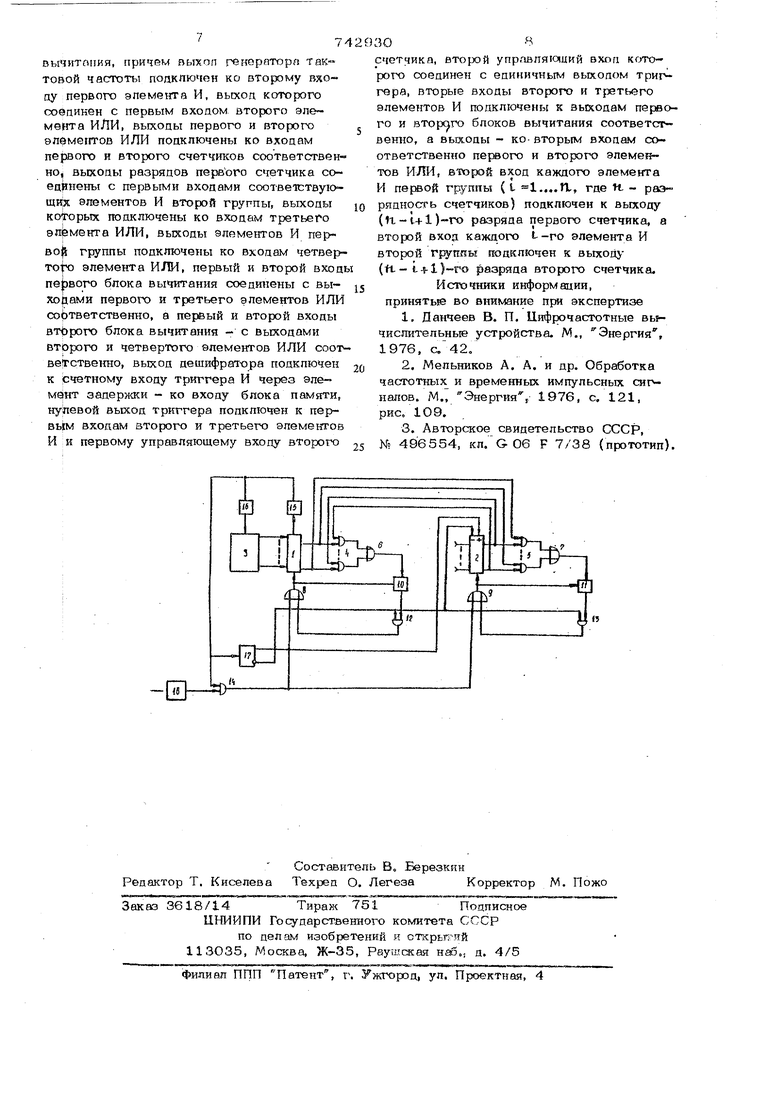

Устройство отнооггся к вычислительно технике и может быть исяюпьзовано в уст ройствах обработки информации. Известны вычислительные устройства, предназначенные ппя вычисления функции вица .. fil и И . Однако они являются довольно спожнь ми по св.оему выполнению. Наиболее близким к предлагаемому по технической сущности является вычислительное устройство, соцержащее четыре счетчика, регистр, две группы элементов И, блок памяти, два дешифратора, два эле мента задержки, три элемента И, элемент ИЛИ и генератор тактовых импульсов sj Недостатками этого устройства являют ся большое количество оборудования и низкое быстродействие, обусловленное наличием делителя частоты, генератора тактовых импульсов в цепи умножения устройства. Цель изобретения - упрощение устройства и повышение его быстропействия. Поставленная цель достигается тем, что вычислительное устройство, содержащее счетчики, бпок памяти, генератор тактовых импульсов, дешифратор, элементы И, ИЛИ и задержки, причем выход блока памяти подключен ко входам первого счетчика, выходы которого подключены ко входам дешифратора, выход которого соединен с первым входом первого элемента И, выход которого пооключен к первому входу первого элемента ИЛИ, выходы рею рядов второго счетчика подклюены к первым входам соответствующих элементов И первой группы, содержит триггер и два блока вычитания, причем выход генератора тактовой частоты подключен ко второму входу первого элемента И, выход которого соединен с первым входом второго элемента ИЛИ, выходы первого и второго элементов ИЛИ noriключены ко входам первого и второго счетчиков соответственно, выходы разрядов первого счетчика соединены с первыми входами соответствующих элементов И второй группы, выхопы которых подключены ко вхопом третьего ИЛИ, выходы элр) И первой группы попкпк)чоны ко входам четвертого элемента ИЛИ и второй входы первого блока вь читашш соединены с выходами первого и третьего впемента ИЛИ соответственно, ,а первый и второй второго блока вычитания - с выхопами второго и чет- вертЬго элементов ИЛИ соответственно, вы ход г(еши4)ратора пошглючен к счетному вход триггера и, через элемент задержки - ко входу блока памяти, нулевой выход триг гера подключен к первым входам второго и третьего элементов И и первому управляющему входу второго счетчика, второй управляющий вход которого соединен с единичным выходом триггера, вторые входы второго и третьего элементов И подключены к выходам первого и второго бло ков аычитвшя соответс1вен1га, а выходы ко вторым Входам соответственно первого и второтю элементов ИЛИ, второй вход .каждого элемента И первой группы (,..,, t1 , гдец-разрядность счетчиков) поцклю.чен к выводу (п -1 + 1)-го разряда первого счетчика, а второй вход каждого 1-го элемЬта И второй группы подключен к Bbixoioy ()-го ра:зряда второго сче чика. На чертеже представлена функциональная Схема устройства. Оно содержит счетчик 1, реверсивный счетчик 2, блок 3 памяти, группы элементов 4 и 5 И, элементы 6-9 ИЛИ, бло ки liO и 11 вычитания, элементы 12-14 И, дешифратор 15, элемент 16 задержки, триггер 17, генератор 18 тактовых импульсов. Работа устройства на примере вычисления многочлена дня случая ft 4. Предварительно в счетчик 1 заносится значение OL, в реверашный счетчик 2 .значение X , а в ячейки блока 3 памяти значения коэффициентов О-о в дополнительном коде и значение К . Триггер 17 устанавливается в О, при этом элементы 12 и 13 И поаготавл11ваются к открыт1по по первым входам, а реверсивный счетчик 2 устанавливается в режим вычитания. Импульсы с генератора 18, частота следования которых fт, поступают на вхо ды элементов 8 и 9 ИЛИ, На второй вхо элемента 8 ИЛИ поступают импульсы с выхода блока Ю вычитания, проходящие черйз элемент 12 И, частота следования которых f 10 . ПотенциальньЕе входы каждого из элементов 4 И поаключешг) к единиц ным выходам одного из триггеров реверсивного пчетчика 2, а импульа1ые входы соединены с единичными выходами одного из триггеров счетчика 1, причем ее- ли один из его входов подключен к триггеру младшего разряда счетчика 2, то второй вход подключен к триггеру старшего р133ряаа счетчика 1 и наоборот. Импульсы появляются на вьшоде того элемента 4 И группы, который подключен к нахогупцеыуся в ецинишом состоянии тригге1у счерчика 2 и переходящему из нулевого s единичное состояние Триггеру счетчика 1. Средняя частота б пования импульсов на выходе элемента 6 ИЛИ определяется частотой fa импульсов, поступающих на вход счетчика 1, и числом W(t), находящимся в реверсивном счетчике 2 и равна; .,,„ где М, - коэффициент пересчета счетчиков 1 и 2. На выходе схемы 10 вычитания частота импульсов равна разности частот, поступающих на ее входы : МП ifi LI Ио 8 Ь Частота импульсов на выходе элемента 8 ИЛИ равна: g- Ьт ,0 (3) Учитывая эти выражения, получим „ 1т Лт/ьх ) Аналогично, учитывая выражения I - Ь Nl(i) IH Ц f Ь - Ь fn , где N,(t) число, содержащееся в счетчике 1, получим „ --bi-Mjst 5NI (i) Частота fg и ig связана с числами, содержацимися в счетчиках 1 и 2, соотношениями:f Ct Ni(t)XQ, 1,.ажш. . (10)1 Попетасляя выражйння (9) и (1О) соответстветго в (4) и (8) получим dNXt). т -Nttt ,с 11 3t N(t) AN2.(t). fr-Nt ,.-. dt Nia) Разделив уравнение (11) на уравнение (12) и произведя разделение переменныя., получим d Мг . dNt(i) Ni(t) N(t) в момент переполнения счетчика 1 дешифратор 15 закроет элемент 14 И. При этом в реверсивном счетчике 2 записывается число У . Проинтегрировав выражение (13), поцставив пределы изменения переменных, получимdNx(tl- (i) Л N(t)- I Ni(t) Поспе этого, через проме куток времени i-i который определяется элементом 16 зааержки, число CLj в дополнительном коде переписывается с блока 3 памяти в счетчик 1, Дешифратор 15 перебрасывает три гер 17 в единичное положение, при этом элементы 12 и 13 И закрываются, а реверсивный счетчик 2 устанавливается в режим суммирования. Импульсы с генератора 18 через открытый элемент 14 И поступают на счетчики 1 и 2. За время прошедшее с момента поступления первого импульса на счетчик 1, до момента переполнения счетчика 1, при котором дешифратор 15 закрывает элемент 14 И, в реверсивный счетчик 2 поступает Qj импульсов. После этого число, записанное в реверс сивном счетчике 2, равно X ач Дальше процесс вычисления повторяется в аналогичном порядке, причем значения чисел переписьюаются с блока 3 памяти в счетчик 1 в следующем порядке XiClj. , Х.1 а, , X 1 ао в результате в реверсивном счетчике 2 содержится число Jt 7 ,15 20 25 О В обшем случае в счетчик 1 прюдварительио заносится значение d , , в реверсивный счетчик 2 - значение X , а в ячейке блока 3 памяти - значения коэффициетггов Q-n-t- Cto в дополнительном, коде и значение X . Результирутощее выражение в общем случае примет- вид: v x-...x.ao Таким образом, при включении в состав устройства реверсивного счетчика, трах элемеЕггоа ИЛИ, двух блоков вычитания и триггера и введении новых связей между элементами из состава вычислитель ного устройства исключается три счетчика, регист р, дешифратор и элемент задержки, чем достигается упрощение устройства по сравнению с известным. В известном устройстве-счетчик 4 уотанавливается в О через промежуток Т - певремени Т - Тт-а.- X риод импульсов тактового генератора, а Q-L - число, содержацееся в этом счет чике. В предлагаемом устройстве в режиме суммирования счетчик 1 устанавливается в через промежуток времени V TVCtL Clt - число, содержащееся в этом счетчике. В режиме умножения промежуток времени, необходимый для установления счетчика 1 в О, меньше Тз. , так как частота импульсов, поступающих на счетчик 1 больше f С учетом вышесказанного, быстродействие предлагаемого устройства выше быстродействия известного. формула изобретения Вычислительное устройство, содержащее счетчик, блок памяти, генератор тактовых импульсов, дешифратор, элементы И, ИЛИ и задержки, причем выход блока памяти подключен ко входам первого счетчика, выходы которого подключены ко входам дешифратора, выход которого сое- динен с первым входом первого элемента И, выход которого подключен к первому входу первого элемента ИЛИ, аыхоаы разрядов второго счетчика подключены к первым входам соответствующих элементов И первой группы, отличающее - с я тем, что, с целью упрощения устройства и повышения его быстродействия, уст ройство содержит триггер и два блока вычитопкя, причем выхоп генератора тактовой частоты подключен ко второму входу первого элемента И, вьосод которого соепикен с первым входом второго элемента ИЛИ, выходы первого и второго елемегггов ИЛИ подключены ко входам первого и второго счетчиков соответегвенно, выходы разрядов первого счетчика со ецинены с первьщи входами соответствующих элементов И второй группы, выходы подключены ко входам третьего вфмента ИЛИ, выходы 9пеме ггов И перBo|i группы подключены ко входам четверrofo элемента ИЛИ, первый и второй вход первого блока вычитания соединены с выхорами первого и третьего элементов ИЛИ соответственно, а пе{йый и второй входы BTJjporo блока вычитания - с выходами второго и четвертого элементов ИЛИ соот BeircTBeifflo, выход дешифрат-ора подключен к счетному входу триггера И через элемент эадернжи - ко входу блока памяти, нулевой выход триггера подключен к первым входам второго и третьего элементов И и первому управляющему входу второго 0в счетчика, второй управляющий вхоп которого соединен с единичным выходом триггера, вторые входы второго и третьего элементов И подключены к выходам первого и второго блоков вычитания соответственно, а выходы - ко- BTopbfM входам соответственно пе{жого и второго элементов ИЛИ, второй вход каждого элемента И первой группы (I 1..,.М, где tt - разрядность счетчиков) подключен к выходу (it-1+1 )-го разряда первого счетчика, а второй вход каждого t -го элемента И второй rf tifibi подключен к выходу(ft- 1.-1)-го разряда второго счетчика. Источники информации, принятые во внимание при экспертизе 1.Данчеев В. П. Иифрочастотные вычислительные устройства. М., Энергия, 1976, с,42, 2.Мельников А. А. и др. Обработка частотных и временных импульсных сигналов. М., Энергия, 1976, с, 121, рис, 10 9. 3.Авторское свидетельство СССР, № 496554, кл.&О6 F 7/38 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Дешифратор времяимпульсных кодов | 1989 |

|

SU1646058A1 |

| Псевдостохастический анализатор спектра | 1985 |

|

SU1278885A1 |

| Устройство для тактовой синхронизации | 1989 |

|

SU1642591A1 |

| Коррелятор | 1981 |

|

SU1024933A1 |

| Преобразователь угла поворота валаВ КОд | 1979 |

|

SU836643A1 |

| Устройство тактовой синхронизации | 1982 |

|

SU1104674A1 |

| Система управления многопозиционной индукционной нагревательной установкой | 1983 |

|

SU1121789A1 |

| Устройство для поверки цифровых измерителей девиации фазы | 1990 |

|

SU1781651A1 |

| Устройство для контроля импульсных последовательностей | 1980 |

|

SU930609A1 |

| Устройство для дифференцирования частотно-импульсных сигналов | 1979 |

|

SU862150A1 |

Авторы

Даты

1980-06-25—Публикация

1978-01-09—Подача