кроме того, блок выделения знаков отсчета выполнен в виде последовательно соединенных первого регистра сдвига, одноразрядного коммутатора и второго регистра сдвига, выход которого соединен с вторым входом одноразрядного коммутатора, кроме того, блок выделения опережающего импульса выполнен в виде последовательно соединенных элемента задержки, первого элемента И, первого триггера, второго элемента И и второго триггера, первый и второй выходы которого соединены соответственно с вторым входом первого элемента И и первым входом третьего триггера, второй вход которого соединен с вторым выходом первого триггера, кроме того, формирователь опорного сигнала выполнен в виде последовательно соединенных третьего регистра сдвига, дешифратора и многоразрядного коммутатора, второй вход которого соединен с выходом формирователя последовательности импульсов.

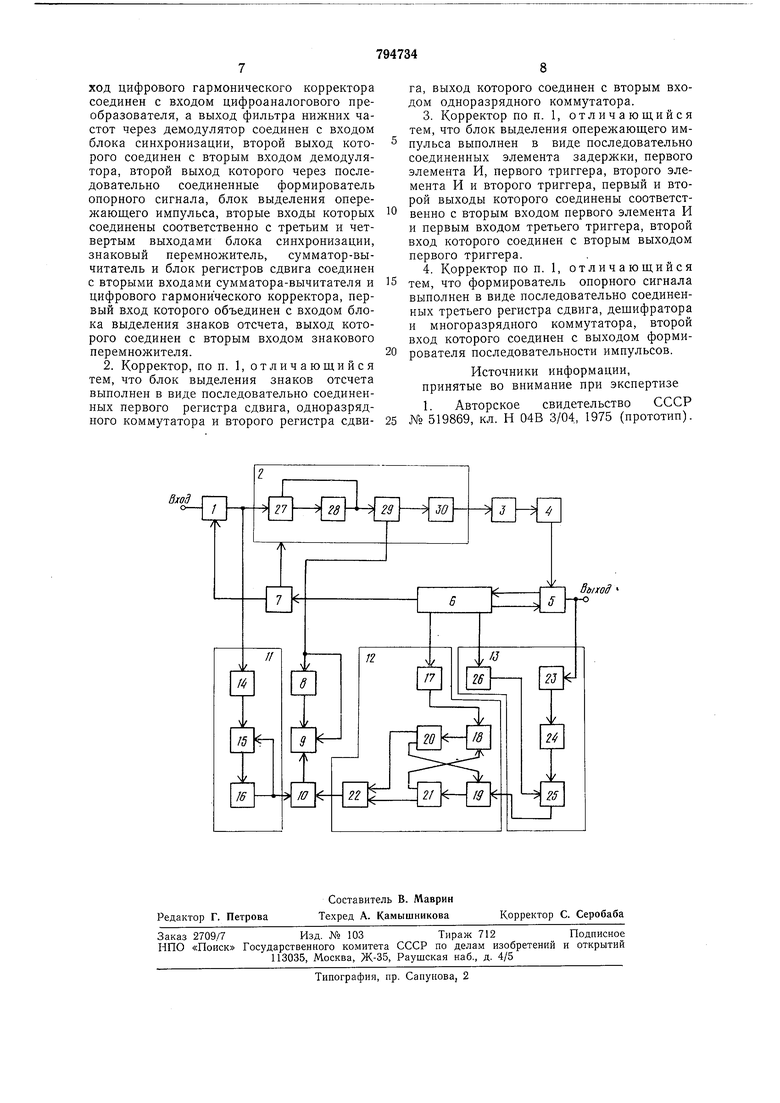

На чертеже приведена структурная электрическая схема предлагаемого устройства.

Адаптивный цифровой корректор содержит аналого-цифровой преобразователь (АЦП) 1, цифровой гармонический корректор (ЦГК) 2, цифроаналоговый преобразователь (ЦА11) 3,5 фильтр 4 нижних частот (ФНЧ), демодулятор 5, блок б синхронизации, блок 7 управления, блок 8 регистров сдвига, сумматор-вычитатель 9, знаковый перемножитель 1и, блок 11 выделения знаков отсчета, блок 12 выделения опережающего импульса, формирователь 13 опорного сигнала.

Блок 11 содержит первый регистр 14 сдвига, одноразрядный коммутатор 15, второй регистр 1б сдвига.

Блок 12 содержит элемент 17 задержки, первый и второй элементы И 18 и i9, первый 20, второй 21, третий 22 триггеры.

Формирователь 13 содержит третий регистр 23 сдвига, дешифратор 24, многоразрядный коммутатор 25 и формирователь 26 последовательности импульсов.

Устройство работает следующим образом.

На вход АЦП 1 подается ОФМ ОБП модулированное колебание, которое стробируется с частотой где /о - несущая частота при передаче нижней боковой полосы сигнала; п--число отсчетов, взятых в

интервале Т - . АЦП I преобразует амп/0

литуду стробов в двоичный десятнразрядный код. Многоразрядный электронный коммутатор 27, блок 28 регистров сдвига сигналов (БРСС), накопитель 2у и цифровой перемножитель 30 образуют ЦГК 2 нерекурсивный цифровой фильтр). Коммутатор 27 с частотой -/с подключает вход БРСС 28 к выходу АЦН I для записи в него очередного входного отсчета. Б промежутке времени между двумя отсчетными

значениями сигнала производится рециркуляция отсчетов входного сигнала, записанных в БРСС 28, с частотой рециркуляции fp л/о (Л/+1), где Л - количество отсчетов, записанных в БРСС 28. Таким образом, цифровой перемножитель 30 в интервале Т последовательно выполняет операций перемнол ения отсчетов входного сигнала на коэффициенты системной функции

цифрового гармонического корректора 2, которые поступают на второй вход перемножителя 30 с выхода блока 8,

Суммирование результатов перемножения производится накопителем 29, и через

каждые Л операций сложения получается очередной отсчет откорректированного выходного сигнала. Отсчеты откорректированного сигнала с частотой стробирования /с поступают на вход ЦАП 3, где цифровой

код преобразуется в напряжение и формируется аналоговый сигнал. С выхода ЦАП 3 через ФНЧ 4 сигнал подается на вход демодулятора 5. Такое включение демодулятора 5 позволяет применить дискретный метод синхронного детектирования, позволяющий свести к минимуму использование аналоговых элементов. Для повышения точности детектирования ОФМ ЛБП сигнала, в демодуляторе 5 используется перенос

спектра принятого сигнала в область высоких частот, несущая частота /н для переноса спектра выбирается равной 8 /оБ блоке 6 производится выделение тактовой /т и несущей частоты /н. Автоматичеекая подстройка фазы несущего и тактового колебаний производится по откорректированному сигналу.

Для обеспечения адаптивной коррекции необходимо подстраивать коэффициенты

ЦГК 2 так, чтобы их значения оставались оптимальными во время нередачн информации. Для настройки коэффициентов используется игеративный алгоритм стахостическои аппроксимации. Знак сигнала ошибки умножается на знаки неоткорректированных отсчетов сигнала в перемножителе 10. Б зависимости от результата перемножения в сумматоре - вычитателе У осуществляется суммирование или вычитание

значения шага адаптации нз коэффициентов, записанных в блоке 8. Регистром 14 производится задержка сигнала на время, необходимое для формирования сигнала и ошибки. С помощью регистра 16 и коммутатора 15 осуществляется рециркуляция знаков неоткорректнрованных отсчетов с частотой ifp /о ()При передаче информации методом ОФМ ОБП выражение для посылки сигнала может быть записано следующим образом:

и (О В, (О cos + о - «1 (OJ,

где Bi (t) - огибающая одиночной посылки;

Oi (О-изменение фазы несущего колебания.

Результирующее модулированное колебание t/7n(-0 может рассматриваться состоящим из суммы отдельных посылок и может быть записано, как

со

т(0 2 A(-iT)cosK +

+ о + в„(-гГ).

Изменение фазы несущего колебания описывается выражением

aiQ()

) arctgi : , (1)

2 aiR(t-lT)

i -oa

где fli 1-при передаче символа Gi - 1 - при передаче символа R(t)-огибающая синфазного компонента;Q(0-огибающая квадратурного

компонента.

Частотные искажения канала связи приводят к искажению информационного сигнала. Сигнал на входе приемника может быть представлен в виде суммы взаимно перекрывающихся одиночных посылок

Um(t} i 5,(-iT)COsK +

( -00

+ 0+0;„() + 6„(-/Г), (2)

где i|3m(О-изменение фазы наполняющего колебания из-за наличия искажений в канале связи. Из выражения (2) следует, что если получить опорный сигнал, характеризующий изменение фазы в соответствии с выражением (1), то можно получить знак и величину ошибки фазы принимаемого сигнала, возникающей вследствие искажений канала связи. Если отсчет фазы производить в середине посылки, то она будет определяться синфазным компонентом основной посылки н квадратурным компонентом соседних нечетных посылок.

Для того, чтобы определить значение фазы в середине посылки необходимо перенести спектр принятого сигнала в область высоких частот. Перенос спектра, как отмечалось выше, производится в демодуляторе 5.

Демодулированный сигнал последовательно записывается в регистр 23, а затем считывается на каждом такте с выхода регистра. В формирователе 26 вырабатываются последовательности импульсов, синхронные с несущей частотой / фаза которых может быть определена из выражения (I). Влияние импульсов, расположенных дальше чем на три тактовых интервала, незначительно, поэтому оно не учитывается при

формировании сигнала, и для этого случая в формирователе 26 необходимо сформировать восемь последовательностей импульсов. В зависимости от кода, записанного в регистре 23, дешифратор 24 управляет коммутатором 25, который подключает одну из последовательностей, вырабатываемых формирователем 26. Таким образом, на входе коммутатора 25 вырабатывается сигнал в

виде коротких импульсов, соответствующих моментам перехода через нулевую ось искаженного ОФМ ОПБ сигнала. Этот опорный сигнал подается на элемент И 19.

Триггеры 20 и 21 тактовыми импульсами

устанавливаются в исходное состояние, при котором на входах элементов И 18, 19, соединенных с выходами триггеров 20, 21, устанавливаются сигналы логической «1. В моменты времени, соответствующие переходу через нуль откорректированного, перенесенного в область высоких частот сигнала, блок 6 вырабатывает импульсы, которые через элемент 17 подаются на элемент И 18. Если импульс, соответствующий переходу принимаемого сигнала через нуль приходит раньше импульса опорного сигнала, то на выходе элемента И 18 появляется сигнал, устанавливающий триггер 20 в состояние, когда на выходе, соединенном

с входом триггера 22, устанавливается уровень «1, а триггер 22 с приходом тактового импульса тока устанавливается в единичное состояние. Если первым приходит импульс опорного сигнала, то на выходе

триггера 22 устанавливается уровень «О.

Таким образом, формируется знаковая

оценка взаимного расположения опорного

и временного сигналов.

Выделение ошибки среднеквадратичных

искажений из фазы принимаемого сигнала позволяет повысить помехоустойчивость устройства, увеличить скорость сходимости алгоритма при работе в шумах, при этом не требуется применения точного устройства автоматической регулировки уровня.

Формула изобретения

1. Адаптивный цифровой корректор, содержащий последовательно соединенные аналого-цифровой преобразователь и цифровой гармонический корректор, тактовые входы которых соединены соответственно с первым и вторым выходами блока управления, вход которого соединен с первым выходом блока синхронизации, а также цифроаиалоговый преобразователь, выход которого соединен с входом фильтра нижних частот, демодулятор, блок регистров сдвига, сумматор-вычитатель и знаковый перемножитель, отличающийся тем, что, с целью повышения точности коррекции, введены блок выделения знаков отсчета, блок выделения опережающего импульса и формирователь опорного сигнала, при этом выход цифрового гармонического корректора соединен с входом цифроаналогового преобразователя, а выход фильтра нижних частот через демодулятор соединен с входом блока синхронизации, второй выход которого соединен с вторым входом демодулятора, второй выход которого через носледовательно соединенные формирователь опорного сигнала, блок выделения опережающего импульса, вторые входы которых соединены соответственно с третьим и четвертым выходами блока синхронизации, знаковый перемножитель, сумматор-вычитатель и блок регистров сдвига соединен с вторыми входами сумматора-вычитателя и цифрового гармонического корректора, первый вход которого объединен с входом блока выделения знаков отсчета, выход которого соединен с вторым входом знакового перемножителя.

2. Корректор, по п. 1, отличающийся тем, что блок выделения знаков отсчета выполнен в виде последовательно соединенных первого регистра сдвига, одноразрядного коммутатора и второго регистра сдвига, выход которого соединен с вторым входом одноразрядного коммутатора.

3.Корректор по п. 1, отличающийся тем, что блок выделения опережающего импульса выполнен в виде последовательно соединенных элемента задержки, первого элемента И, первого триггера, второго элемента И и второго триггера, первый и второй выходы которого соединены соответственно с вторым входом первого элемента И и первым входом третьего триггера, второй вход которого соединен с вторым выходом первого триггера.

4.Корректор по п. 1, отличающийся тем, что формирователь опорного сигнала

выполнен в виде последовательно соединенных третьего регистра сдвига, дещифратора и многоразрядного коммутатора, второй вход которого соединен с выходом формирователя последовательности импульсов.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 519869, кл. Н 04В 3/04, 1975 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Демодулятор фазоманипулированного сигнала | 1978 |

|

SU758560A1 |

| СТАРТСТОПНАЯ СИСТЕМА СВЯЗИ | 2003 |

|

RU2252489C2 |

| ДЕМОДУЛЯТОР СИГНАЛОВ С ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ МОДУЛЯЦИЕЙ | 2014 |

|

RU2549360C1 |

| Адаптивный цифровой корректор | 1982 |

|

SU1083379A1 |

| ДЕМОДУЛЯТОР СИГНАЛОВ С ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ МОДУЛЯЦИЕЙ | 2011 |

|

RU2460225C1 |

| КОРРЕЛЯЦИОННЫЙ ПРИЕМНИК СИГНАЛОВ С ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ МОДУЛЯЦИЕЙ | 1995 |

|

RU2099893C1 |

| Устройство для приема дискретной информации | 1987 |

|

SU1501298A1 |

| ДЕМОДУЛЯТОР СИГНАЛОВ С ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ МОДУЛЯЦИЕЙ | 2011 |

|

RU2460224C1 |

| СПОСОБ ДЕМОДУЛЯЦИИ СИГНАЛОВ С ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ МОДУЛЯЦИЕЙ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2003 |

|

RU2271071C2 |

| СТАРТСТОПНАЯ СИСТЕМА СВЯЗИ | 2005 |

|

RU2308163C2 |

Авторы

Даты

1981-01-07—Публикация

1979-02-12—Подача