1

Изобретение относится к устройствам демодуляции цифровых сигналов и может быть использовано в системах связи и управления.

Известен демодулятор фазоманипулированного сигнала, содержащий генератор импульсов, первый дискретизатор, генератор опорного сигнала и последовательно соединенные сумматор, квантователь, первый перемно;: итель, ко второму входу которого подключен выход генератора опорного сигнала, накопитель, коммутатор и решающий блок 1 .

Однако помехоустойчивость такого демодулятора невелика.

Цель изобретения - повышение помехоустойчивости устройства.

Цель достигается тем, что в демодулятор фазоманипулированного сигнала, содержащий генератор импульсов, первый дискретизатор, генератор опорного сигнала и последовательно соединенные сумматор, квантователь, первый перемножитель, ко второму входу которого подключен ыход генератора опорного сигнала, накопитель, коммутатор и решающий блок, введены два элемента задержки, второй дискретизатор, второй перемножитель.

измеритель интенсивности помехи и последовательно соединенные блок выделения сигнала и блок автоматической регулировки усиления, выход которого через генератор импульсов подключен к первому входу второго дискретизатора, второй вход и выход которого соединены соответственно с выходом первого элемента задержки и

10 первым входом сумматора, ко второму входу которого подключен выход второго элемента задержки, вход которого соединен с выходом первого дискретиЗатора и первым входом второго

15 перемножителя, второй вход и выход которого соединены соответственно с первым входом генератора опорного сигнала и первым входом измерителя интенсивности помехи, второй вход

20 которого соединен со вторым входом генератора опорного сигнала, дополни ельные выходы которого г щключены к соответствующим входам измерителя интенсивности помехи, третий

25 вход и выходы которого соединены соответственно со в-горым выходом коммутатора и входами блока вьщеления сигнала, при этом вход первого элемента задержки соединен со входом первого дискретизатора, а на

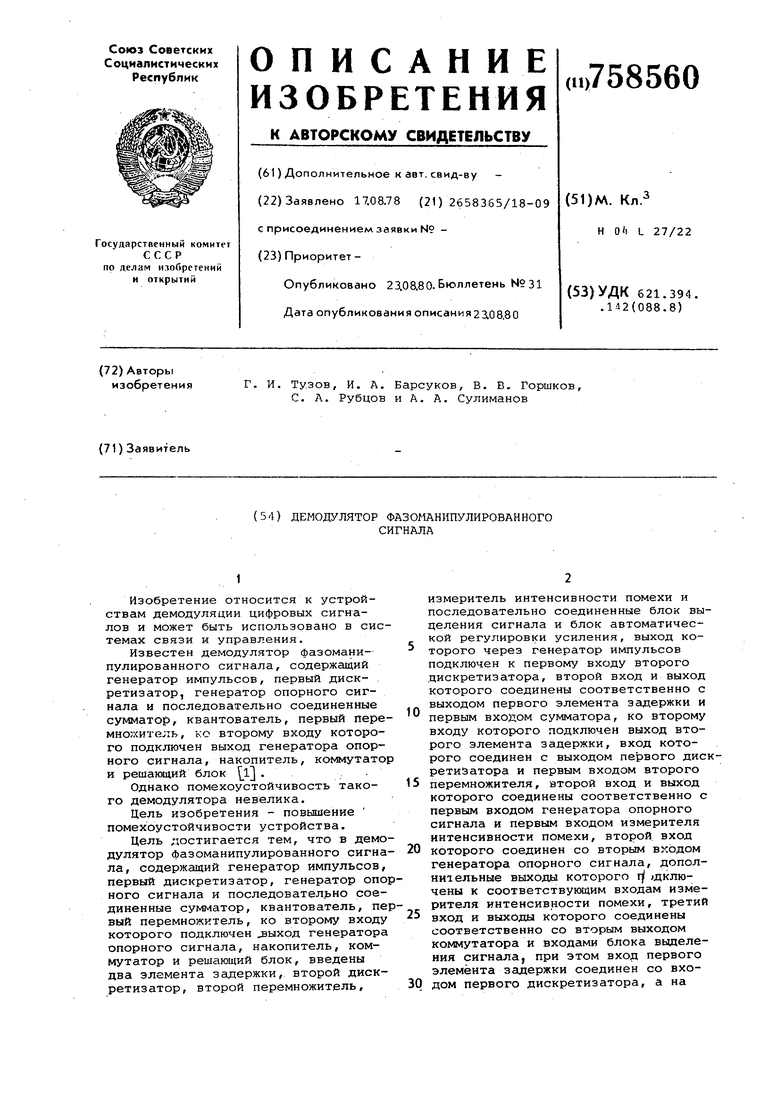

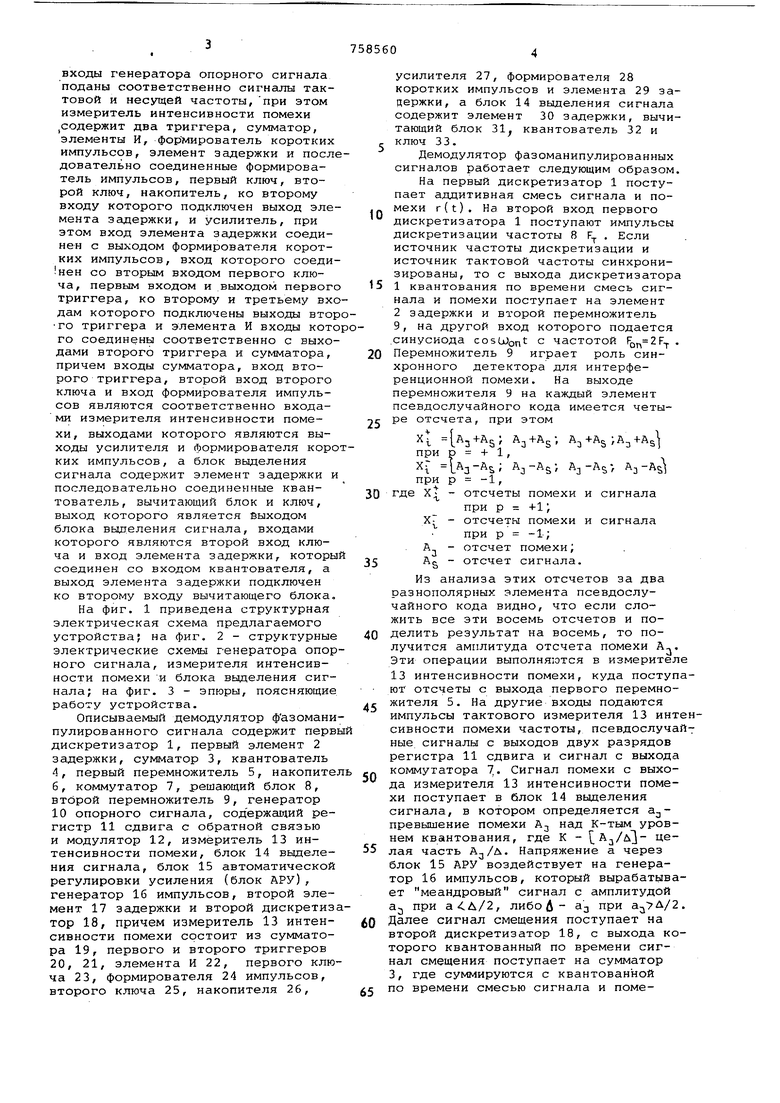

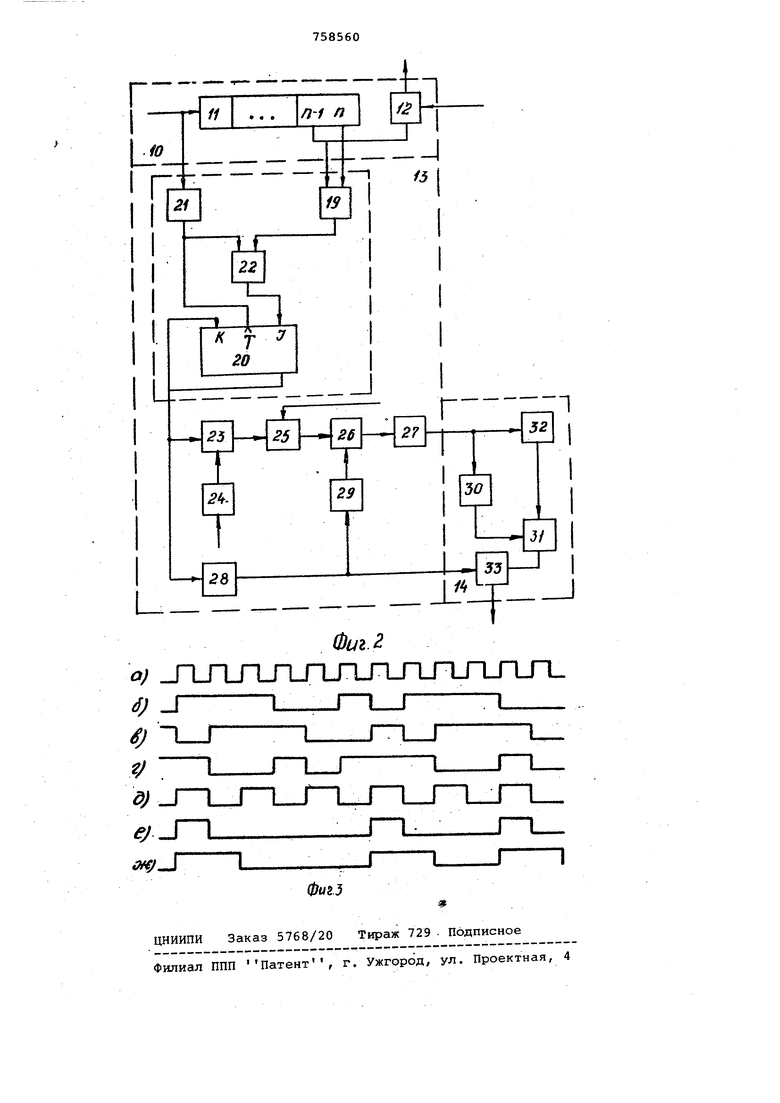

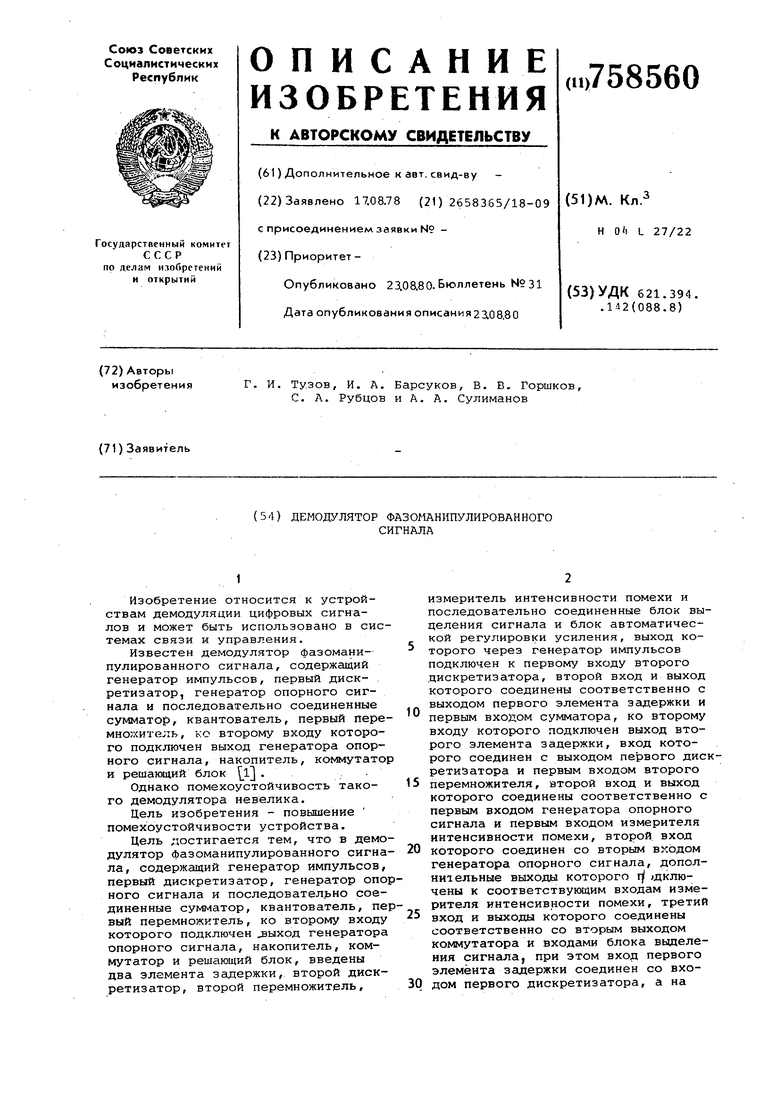

входы генератора опорного сигнала поданы соответственно сигналы тактовой и несутчей частоты, при этом измеритель интенсивности помехи .содержит два триггера, сумматор, элементы И, формирователь коротких импульсов, элемент задержки и последовательно соединенные формирователь импульсов, первый ключ, второй ключ, накопитель, ко второму входу которого подключен выход элемента задержки, и усилитель, при этом вход элемента задержки соединен с выходом формирователя коротких импульсов, вход которого соеди нен со вторым входом первого ключа, первым входом и выходом первого триггера, ко второму и третьему входам которого подключены выходы втор го триггера и элемента И входы кото го соединены соответственно с выходами второго триггера и сумматора, причем входы сумматора, вход второго триггера, второй вход второго ключа и вход формирователя импульсов являются соответственно входами измерителя интенсивности помехи, выходами которого являются выходы усилителя и формирователя короких импульсов, а блок вьщеления сигнала содержит элемент задержки и последовательно соединенные квантователь, вычитающий блок и ключ, выход которого явлается Выходом блока выделения сигнала, входами которого являются второй вход ключа и вход элемента задержки, которы соединен со входом квантователя, а выход элемента задержки подключен ко второму входу вычитающего блока. На фиг. 1 приведена структурная электрическая схема предлагаемого устройства; на фиг. 2 - структурные электрические схемы генератора опорного сигнала, измерителя интенсивности помехи и блока выделения сигнала; на фиг. 3 - эпюры, поясняющие работу устройства.

Описываемый демодулятор фазоманипулированного сигнала содержит перв дискретизатор 1, первый элемент 2 задержки, сумматор 3, квантователь 4, первый перемножитель 5, накопите 6, коммутатор 7, решающий блок 8, второй перемножитель 9, генератор 10 опорного сигнала, содержа&щй регистр 11 сдвига с обратной связью и модулятор 12, измеритель 13 интенсивности помехи, блок 14 выделения сигнала, блок 15 автоматической регулировки усиления (блок АРУ), генератор 16 импульсов, второй элемент 17 задержки и второй дискретизтор 18, причем измеритель 13 интенсивности помехи состоит из сумматора 19, первого и второго триггеров 20, 21, элемента И 22, первого ключа 23, формирователя 24 импульсов, второго ключа 25, накопителя 26,

усилителя 27, формирователя 28 коротких импульсов и элемента 29 задержки, а блок 14 вьщеления сигнала содержит элемент 30 задержки, вычитающий блок 31 квантователь 32 и ключ 33.

Демодулятор фазоманипулированных сигналов работает следующим образом

На первый дискретизатор 1 поступает аддитивная смесь сигнала и помехи r(t). На второй вход первого дискретизатора 1 поступают импульсы дискретизации частоты 8 F . Если источник частоты дискретизации и источник тактовой частоты синхронизированы, то с выхода дискретизатор

1квантования по времени смесь сиг- нала и помехи поступает на элемент

2задержки и второй перемножитель 9, на другой вход которого подается

.синусиода cosOJont с частотой Перемножитель 9 играет роль синхронного детектора для интерференционной помехи. На выходе перемножителя 9 на каждый элемент псевдослучайного кода имеется четыре отсчета, при этом

1 A +AS A-J+AS

при р + 1,

1 Ua J-AS

A-,-AS

АЗ -AS

Ч

при р где Х - отсчеты помехи и сигнала

при р +1; Х - отсчеты помехи и сигнала

при р -1; А - отсчет помехи; Ag - отсчет сигнала.

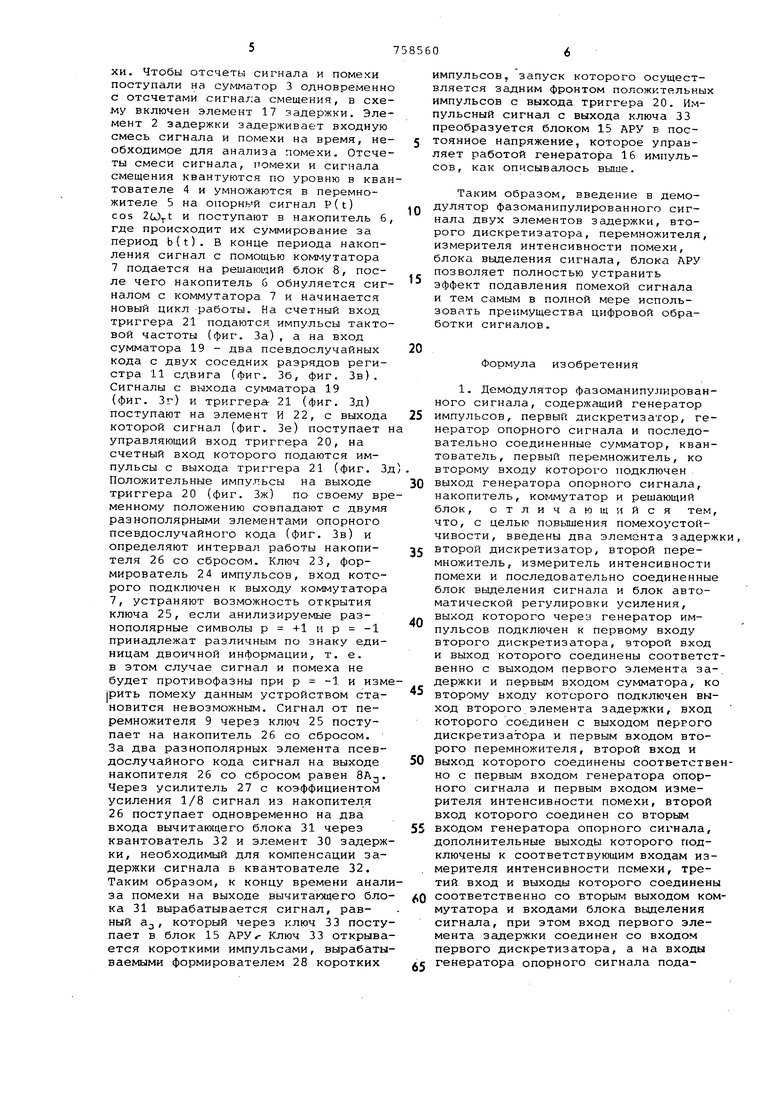

Из анализа этих отсчетов за два разнополярных элемента псевдослучайного кода видно, что если сложить все эти восемь отсчетов и поделить результат на восемь, то получится амплитуда отсчета помехи А... Эти операции выполняются в измерителе 13 интенсивности помехи, куда поступают отсчеты с выхода первого перемножителя 5. На другие входы подаются импульсы тактового измерителя 13 интесивности помехи частоты, псевдослучайные сигналы с выходов двух разрядов регистра 11 сдвига и сигнал с выхода коммутатора 7,. Сигнал помехи с выхода измерителя 13 интенсивности помехи поступает в блок 14 выделения сигнала, в котором определяется а.превышение помехи А- над К-тым уровнем квантования, где К - A-j/A - целая часть АЗ/Д. Напряжение а через блок 15 АРУ воздействует на генератор 16 импульсов, который вырабатывает меандровый сигнал с амплитудой а., при а4.Д/2, либо 6 - аз при Далее сигнал смещения поступает на второй дискретизатор 18, с выхода которого квантованный по времени сигнал смещения поступает на сумматор 3, где суммируются с квантованной по времени смесью сигнала и помехи. Чтобы отсчеты сигнала и помехи поступали на сумматор 3 одновременн с отсчетами сигнала смещения, в схе му включен элемент 17 задержки. Эле мент 2 задержки задерживает входную смесь сигнала и помехи на время, не обходимое для анализа помехи. Отсче ты смеси сигнала, ттомехи и сигнала смещения квантуются по уровню в ква тователе 4 и умножаются в перемножителе 5 на опорный сигнал P(t) cos и поступают в накопитель б где происходит их суммирование за период b(t). В конце периода накопления сигнал с помощью коммутатора 7 подается на решающий блок 8, после чего накопитель 6 обнуляется сиг налом с коммутатора 7 и начинается новый цикл работы. На счетный вход триггера 21 подаются импульсы такто вой частоты (фиг. За), а на вход сумматора 19 - два псевдослучайных кода с двух соседних разрядов регистра 11 слвига (фиг. Зб, фиг. Зв) . Сигналы с выхода сумматора 19 (фиг. Зг) и триггера- 21 (фиг. Зд) поступают на элемент И 22, с выхода которой сигнал (фиг. Зе) поступает управляющий вход триггера 20, на счетный вход которого подаются импульсы с выхода триггера 21 (фиг. З Положительные импульсы на выходе триггера 20 (фиг. Зж) по своему вр менному положению совпадают с двумя раэнополярными элементами опорного псевдослучайного кода (фиг. Зв) и определяют интервал работы накопителя 26 со сбросом. Ключ 23, формирователь 24 импульсов, вход которого подключен к выходу коммутатора 7, устраняют возможность открытия ключа 25, если анилизируемые разнополярные символы р +1 и р -1 принадлежат различным по знаку единицам двоичной информации, т. е. в этом случае сигнал и помеха не будет противофазны при р -1 и изм |рить помеху данным устройством становится невозможным. Сигнал от перемножителя 9 через ключ 25 поступает на накопитель 26 со сбросом. За два разнополярных элемента псевдослучайного кода сигнал на выходе накопителя 26 со сбросом равен SA-j Через усилитель 27 с коэффициентом усиления 1/8 сигнал из накопител я 26 поступает одновременно на два входа вычитающего блока 31 через квантователь 32 и элемент 30 задерж ки, необходимый для компенсации задержки сигнала в квантователе 32. Таким образом, к концу времени анал за помехи на выходе вычитающего бло ка 31 вырабатывается сигнал, равный а-,, который через ключ 33 посту пает в блок 15 АРУ Ключ 33 открыв ется короткими импульсами, вырабаты ваемыми формирователем 28 коротких мпульсов, запуск которого осущестляется задним фронтом положительных мпульсов с выхода триггера 20. Имульсный сигнал с выхода ключа 33 реобразуется блоком 15 АРУ в посоянное напряжение, которое управяет работой генератора 16 импульов, как описывалось выше. Таким образом, введение в демоулятор фазоманипулированного сигнала двух элементов задержки, второго дискретизатора, перемножителя, измерителя интенсивности помехи, блока выделения сигнала, блока АРУ позволяет полностью устранить эффект подавления помехой сигнала и тем самым в полной мере использовать преимущества цифровой обработки сигналов. Формула изобретения 1. Демодулятор фазоманипулированного сигнала, содержащий генератор импульсов, первый дискретизатор, генератор опорного сигнала и последовательно соединенные сумматор, квантователь , первый перемножитель, ко второму входу которого подключен выход генератора опорного сигнала, накопитель, ко.мутатор и решающий блок, отличающийся тем, что, с целью повыщения помехоустойчивости, введены два элемента задержки, второй дискретизатор, второй перемножитель, измеритель интенсивности помехи и последовательно соединенные блок выделения сигнала и блок автоматической регулировки усиления, выход которого через генератор импульсов подключен к первому входу второго дискретизатора, второй вход и выход которого соединены соответственно с выходом первого элемента за-, держки и первым входом сумматора, ко второму входу которого подключен выход второго элемента задержки, вход которого соединен с выходом пергого дискретизатора и первым входом второго перемножителя, второй вход и выход которого соединены соответственно с первым входом генератора опорного сигнала и первым входом измерителя интенсивности помехи, второй вход которого соединен со вторым входом генератора опорного сигнала, дополнительные выходы которого подключены к соответствующим входам измерителя интенсивности помехи, третий вход и выходы которого соединены соответственно со вторым выходом коммутатора и входами блока выделения сигнала, при этом вход первого элемента задержки соединен со входом первого дискретизатора, а на входы генератора опорного сигнала поданы соответственно сигналы тактовой и несущей частоты. 2. Демодулятор по п. 1, о т л 1ающийся тем, что измеритель интенсивности помехи содержит два триггера, , элемент И, формирователе) коротких импульсов, элемент задержки и последовательно соединенные формирователь импульсов первый ключ, второй ключ, накопител ко второму входу которого подключен выход элемента задержки, и усилитель, при этом вход элемента задерж ,ки соединен с выходом формирователя коротких импульсов, вход которого соединен со вторь входом первого ключа, первым входом, и выходом перв го триггера, ко второму и третьему входам которого подключены выходы второго триггера и элемента И в ды которого соединены соответственно с выходами второго триггера и сумматора, причем входы сумматора, вход второго триггера, второй вход второго ключа и вход формирователя импульсов являются соответственно входами измерителя интенсивности помехи, выходами которого являются выходы усилителя и формирователя коротких импульсов. 3. Демодулятор по п. 1, отличающийся тем, что блок выделения сигнала содержит элемент задержки и последовательно соединенные квантователь, вычитающий блок и ключ, выход которого является выходом блока вьщеления сигнала, входами которого являются второй вход ключа и вход элемента задержки, который соединен со входом квантователя, а выход элемента задержки подключен ко второму входу вычитающего блока. Источники информации, принятые во внимание при экспертизе 1. James L. Lewis. Analysis of quantization and dither effekts on spread spectrum signa 1 s . - I ЕЕE National Telecommunication conference. 1975, P. 33/10-.

г

//

п-1 п

L

I Гг

-V

-I

«

| название | год | авторы | номер документа |

|---|---|---|---|

| Демодулятор фазоманипулированного сигнала | 1980 |

|

SU919151A2 |

| Устройство тактовой синхронизации | 1979 |

|

SU932642A1 |

| Система связи | 1981 |

|

SU1094559A1 |

| СПОСОБ И УСТРОЙСТВО СИНХРОНИЗАЦИИ М-ПОСЛЕДОВАТЕЛЬНОСТИ | 1997 |

|

RU2127954C1 |

| СПОСОБ И УСТРОЙСТВО СИНХРОНИЗАЦИИ М-ПОСЛЕДОВАТЕЛЬНОСТИ С ПОВЫШЕННОЙ СЛОЖНОСТЬЮ | 1999 |

|

RU2153230C1 |

| УСТРОЙСТВО ПРИЕМА И ПЕРЕДАЧИ ФАЗОМАНИПУЛИРОВАННЫХ КОДОВЫХ СИГНАЛОВ | 2002 |

|

RU2236086C2 |

| Демодулятор сигналов относительной фазовой манипуляции | 1989 |

|

SU1727207A1 |

| Следящий приемник асинхронных шумоподобных сигналов | 1986 |

|

SU1403381A1 |

| СТАРТСТОПНАЯ СИСТЕМА СВЯЗИ | 2003 |

|

RU2252489C2 |

| СПОСОБ И УСТРОЙСТВО СИНХРОНИЗАЦИИ М-ПОСЛЕДОВАТЕЛЬНОСТИ | 2002 |

|

RU2244384C2 |

22

I

Авторы

Даты

1980-08-23—Публикация

1978-08-17—Подача