(54) ФАЗОВЫЙ РАЗЛИЧИТЕЛЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| Фазовый различитель | 1975 |

|

SU531096A1 |

| Устройство компенсации нелинейных искажений радиосигналов | 1988 |

|

SU1626395A2 |

| Фазовый дискриминатор | 1983 |

|

SU1171970A1 |

| РАДИОЛОКАЦИОННОЕ ПРИЕМНОЕ УСТРОЙСТВО | 1984 |

|

SU1841013A1 |

| Устройство для сравнения амплитуд двух низкочастотных гармонических напряжений | 1983 |

|

SU1128199A1 |

| Цифровой фазометр | 1986 |

|

SU1377766A1 |

| Способ цифрового управления многофазным инвертором | 1989 |

|

SU1683154A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ДВУХСИГНАЛЬНЫХ ХАРАКТЕРИСТИК ЧАСТОТНОЙ ИЗБИРАТЕЛЬНОСТИ РАДИОПРИЕМНИКА ПО БЛОКИРОВАНИЮ И ПЕРЕКРЕСТНЫМ ИСКАЖЕНИЯМ | 1998 |

|

RU2144265C1 |

| Устройство для контроля фазочастотных характеристик каналов связи | 1985 |

|

SU1394440A1 |

| Устройство для измерения полосы блокирования радиоприемников | 1983 |

|

SU1177922A1 |

Изобретение относится к фазоизмерительной технике и может быть использовано при создании фа.зометров с расширенным угловым диапгэзоном и систем фазовой автопоасгройки ча стоты с больиюй. полосой схватывания.

Известен фазовый различитель, содержащий фазовые детекторы 1.

Недостатком его является О1раннченньй диапазон однозначности амплнтудно- фазовой характеристики.

Известен также фазовый различитель, содержащий последовательно соединенные схему дифференцирования, логический элемент с инвертором и коммутатор, а также эааоминающее устройство с умножителем На ива, первый вход которого одновременно подключен ко входам схемы дифференцирования, сумматора и к выходу фазо- вого детектора, второй вход подключен кдогнческому элементу с инвертором, а выход через второй вход коммутатора - но входу сумматора, вькод которого через

схему сравнения соединен с третьим входом запоминающего устройства с умножителем на два 2.

Однако известный фазовый различител не позволяет значительно увеличить полосу схватывания из.-за того, что ам- плитудно-фазовая характеристика формируется из разнополярных участков амплитудно-фазовой характеристики входящего в него фазового детектора. А это приводит к тому, что прирост постоянной составляющей напряжения на .вькоде фазового различителя замедлен из-за того, . что, например, положительная полуволна напряжения на выходе фазового различителя формируется как из положительных, так и из отрицательных полуволн напряжения фазового детектора, первая из них (например, положительная полуволна) увеличивает постоянную .составляющую, а вторая (отрицательная), наоборот, уменьщает постоянную составляющую.

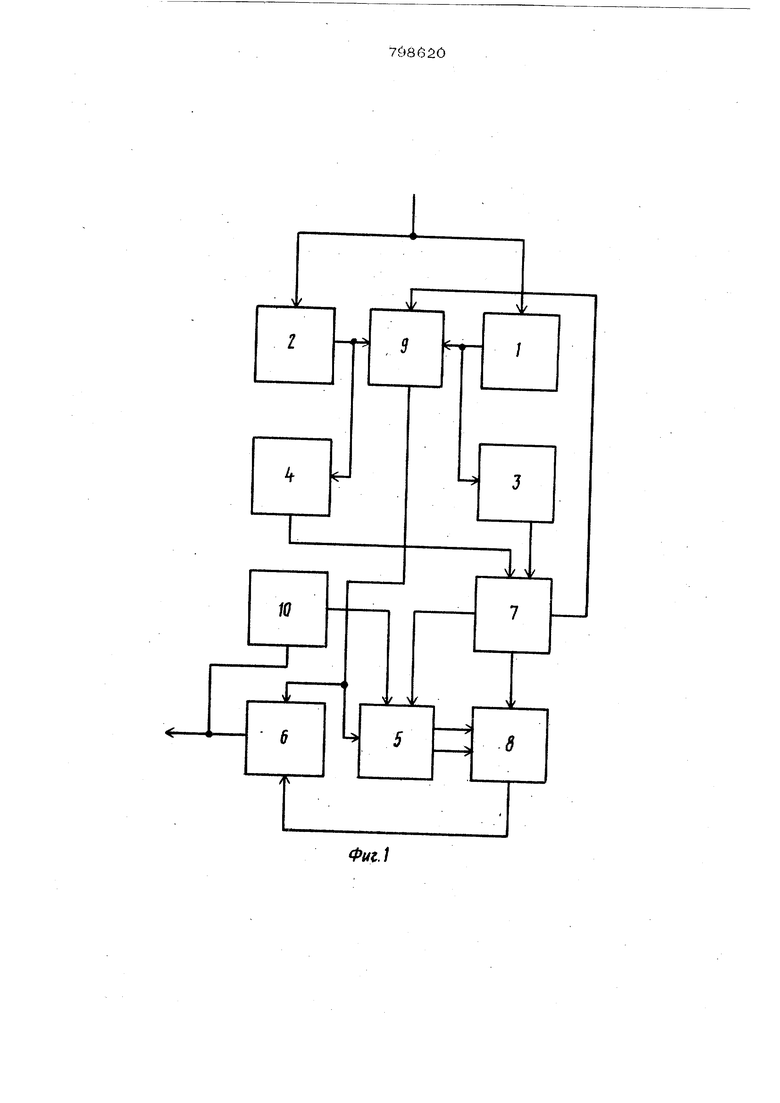

Для эффективного прироста постоянной составляющей напряжения фазового 37 . различителя -необходимо, чтобы положительная полуволна напряжения на его выходе была сформирована только иа полож;ительных полуволн напряжения фазового детектора, а отрицательная полувол на напряжения - только из отрицательны полуволн фазового детектора. Цель изобретения - увеличение полос схватывания при использовании в системах автоподстройки частоты. Указанная цель достигается за сче того, что в фазовый различнтель, содержащий фазовый детектор, которьй через блок дифференцирования соединен с логическим элементом с инвертером, первый выход которого соединен с коммутатором а второй выход - с первым входом запо минающего элемента, выходы которого соединены с коммутатором второй вход запоминающего элемента через сумматор и блок сравнения соединен со своим тре тьим входом, введены дополнительные блок дифференцирования, коммутатор и фазовый детектор,вход которого соединен со входом основного фазового детек тора, а выход через дополнительный бло дифференцирования соединен со входом логического элемента с инвертором, выход которого соединен с одним входом дополнитепьного. KOMNjyTaTopa, другие входы которого соединены с выходами фазовых детекторов, а выход соединен со вторым входом запоминающего элеме та. На фиг. 1 представлена функциональ ная схема фазового разпичитепя; на фиг. 2 графики, поясняющие его работу. Фазовый различитель состоит из фа- .зовых детекторов 1 и 2, двух блоков 3 и 4 дифференцирования, запоминающего элемента 5, сумматора 6, логического элемента 7 с инвертором, двух коммутаторов 8 и 9 и -блока Ю сравнения. Фазовые детекторы -1 и 2, должны иметь однозначные в интервале + X эм- плитудно-фазовые характеристики, сдвинутые на 1C и, в частном случае, линейные. Пусть при включении устройства разность фаз на входе первого фазового де тектора положительна / 0 Ч Tt/ и возрастает (фиг. 2а). При превыщении выходным напряжением фазового детектора 1 заданного уровня логический элемент 7 подключае запоминающий элемент 5 на выход второго коммутатора 9, ко входам которог подключены выходы базовых детек. .1 и 2. Логический элемент 7 при отсутствии управляющих импупьсов с выходов блоков дифференцирования 3 и 4, т.е. до начала работы, всегда подключает к сумматору 6 и запоминающему элементу 5 выход фазового детектора 1. При т - происходит скачок выходного напряжения фазового детектора 1 в область отрицательных значений, на выходе блока 3 появляется импупьс отрицательной полярности. Этот импупьс с помощью логического элемента 7 подключает через коммутатор 9 к первому входу сумматора 6 выход фазового детектора 2, а ко второму входу сумматора 6 через коммутатор 8 вьрсод запоминающего элемента 5, напряжение которого равно максимальному значению напряжения при Ч - Ti на выходе фазового детектора 1 (на фиг. 2в это пунктирная линия „ча интервале 1С М 2Л:}. При дальнейшем увеличении разности фаз до Ч 2 выходное напряжение различителя фазы на вькоде сумматора 6 изменяетсяот максимального значения напряжения на вьссоде фазового детектора 1 до удвоенного его значения. При Ц - 21 происходит скачок выходного напряжения фазового детектора 2, на выходе блока 4 появляется импульс отрицательной полярности, который с помощью логического элемента 7 подключает через коммутатор 9 к первому входу сумматора 6 выход фазового детектора 1, а ко второму входу сумматора 6 через коммутатор 8 выход запоминающего элемента 5, напряжение которого равно удвоенному максимальному зна-. чению напряжения первого фазового детектора при If г С . Этот же импульс подключает к выходу блока 3 инвертор, которьш находится в логическим элементе 7, подготавливая тем самым переключение полярности напряжения с выхода элемента 5 на выход сумматора 6 через коммутатор 8. Второй отрицательный импульс с блока 3, который формируется при разности фаз IP - 3 , переключает полярность напряжения запоминающего элемента 5, которое подается на. сумматор 6 через коммутатор 8 (фиг, 2в). , Второй отрицательный импульс с блока 4 (при -4 , фиг. 26) с помощью логического элемента 7 подключает через коммутатсф 9 к первому входу сумматора 6 выход фазового детектора 2, а ко второму входу сумматора б через коммутатор 8 выход запоминающего элемента 5, При Ч - третий отрицательный имаульс с блока 3 с помощью логического элемента 7 подключает через коммутатор 9 к первому входу, сумматора 6 выход |)азового детектора 1, а от второго входа сумматора 6 отключает запоминающий элемент 5. Когда выходное напряжение сумматора 6 будет равно заданном } чЗначению вблнЗи нуля (фиг. 2в) .блок 1О сравнения разряжает запоминающий элемент 5. Если же при включении фазового различителя разность фаз положительна, но лежит в пределах IC V 2.il и увеличивается, то первый отрицательный импульс появится на вькоде блока 4. Но логический элемент 7 выполнен образом, что никаких переключений в схеме не про и зойдет, а весь цикл начнется только при разности фаз на входе фазового детектора 1, когда напряжение на его выходе скачком изменит положительное напряжение на отрицательное. Если при включении устройства разность фаз отрицательна и возрастает по абсолютному значению, то на выходах блоков дифференцирования будут импульсы поттожительной полярности, и все процессы будут следовать в обратном порядке., Использование второго фазового детектора, второго блока дифференцирования и второго коммутатора позволяет сформировать положительную полуволну сигнала фазового различителя в пределах разности фаз 3lt только из положительных полуврлн напряжения фазовых детекторов, а отрицательную полуволну - из отрицательнь1х полуволн напряжения фазовых детекторов. Предлагаемый фазовый различитель позволяет значительно увеличить полосу схва- тывания в системах фазовой автоподстройки частоты. Формулаизобретения Фазовый различитель, содержащий фазовый детектор, который через блок дифференцирования соединен с логическим элементом с инвертором, первый выход (Которого соединен с коммутатором, а выход - с первым входом запомй-нающего элемента, выходы котооого соединены с коммутатором, второй вход запоминающего элемента через сумматор и блок сравнения соединен со своим третьим входом, отличающийся тем, что, с целью увеличения полосы схватьшания при ибЬользовании его в системах автоподстройки частоты, в него введены дополнительные блок дифференцирования, коммутатор и фазовый детектор, вход которого соединен со входом основного фазового детектора,.а выход через дополнительный блок дифференцирования соединен со входом логического элемента с инвертором, выход которого соединен с одним входом.дополнитепьного коммутатора, другие входы которого-соединены с выходами фазовых детекторов, а выход соединен со вторым входом запоминающего элемента. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 391495, кл. Q 01 I 25/О4, 27.09.71. 2. Авторское свидетельство СССР № 531О96, кл. Q 01 R 25/ОО, 18.О2.75 (прототип).

Pflt

Я) О

)

зг

/д

. .

1)

Tff fff

zjr ззг

srr

sir

«jr

6ir f

yf

Авторы

Даты

1981-01-23—Публикация

1979-04-06—Подача