с выходом триггера, входы которого соединены с соответствующими выходами узла синхронизации, связанного четвертым входом с первым выходом узла анализа приоритета, второй выход которого подключен ко входу разрешения обмена устройства Гз .

Недостаток устройства заключаетс в ограниченных функциональных возмоностях, вследствие чего устройство не позволяет осуществить изменение приоритета источников без изменения места включения блока сопряжения источника.

Цель изобретения - расширение функциональных возможностей устройства за счет обеспечения возможности перераспределения приоритетов источников информации без изменения места их подключения к магистрали.

Поставленная цель достигается тем, что в устройство, содержащее группу каналов источников, каждый из которых включает узел анализа приоритетов, вход и выход которого соединены соответственно с первыми выходом и входомузла синхронизации второй вход которого является соотетствующим входом запроса источника устройства, третий вход подключен к соответствующей входной шине разрешения устройства и первому входу узла задержки, а второй выход - ко второму входу узла задержки, третий вход которого является соответствующим управляющим входом устройства, в каждый канал источника введен адресный регистр, причем вход адресного регистра подключен к третьему выходу узла синхронизации , а группа выходов - к группе входов узла анализа приоритета и к группе адресных шин Vcтpoйcтвa, четветрый выход узла синхронизации соединен с соответствующей выходной шиной запроса устройства, а дервый вход - с одним из выходов группы выходов адресного регистра, выход узла Зсодержки и четвертый вход узла синхронизации подключены соответственно к первой и второй шинам узла синхронизации устройства, а также тем, что узел анализа приоритета содержит группу элементов И, группу элементов НЕ, выходной элемент И и коммутатор, причем первые входы элементов И группы подключены к соответствующим выходам коммутатора, вторые входц - к соответствукядим входам из группы входов узла, а выходы - ко входам соответствуквди элементов НЕ группы, выходы которых соединены с соответствующими входами из группы входов выходного элемента И, вход и выход которого являются соответственно входом и выходом узла, а также тем, что узел задержки содержит триггер приоритета, выход которого является первым выходом узла, триггер занятности магистрали, нулевой вход которого является четвертым входом узла, триггер запроса, единичный вход которого является вторым входом узла, а выход четвертым выходом узла, счетный триггер, нулевой выход которого является вторым выходом узла, четыре элемента И, элемент ИЛИ и два элемента НЕ, причем выход первого элемента И подключен к третьему выходу

0 узла, а первый вход - к выходу триггера занятости магистрали, первому входу элемента ИЛИ и нулевому входу триггера запроса, соединенному выходом с первым входом второго элемента И, второй вход которого подключен к нулевому выходу счетного триггера, а третий вход - к третьему входу узла, первым входом третьего и четвертого элементов И и через

Q первый элемент НЕ ко второму входу первого элемента И и входу счетного триггера, единичным выходом соединенного со вторыми входами третьего и четвертого элементов И, третий вход которого через второй элемент

5 НЕ соединен с первым входом узла и третьим входом третьего элемента И, выходом подключенного к единичному входу триггера занятости магистрали, второй вход и выход элемента ИЛИ соединен соответственно с выходом четвертого элемента И и нулевым входом триггера приоритета, а также тем, что узел задержки содержит триггер, элемент И и два элемента задержки, причем выход триггера соединен с первым входом элемента И, входы которого и входы триггера являются соответственно первым, вторым и третьим входами

Q узла, выход первого элемента задержки соединен с вторым входом элемента И и через второй элемент задержки с выходом узла, а вход - с выходом элемента И.

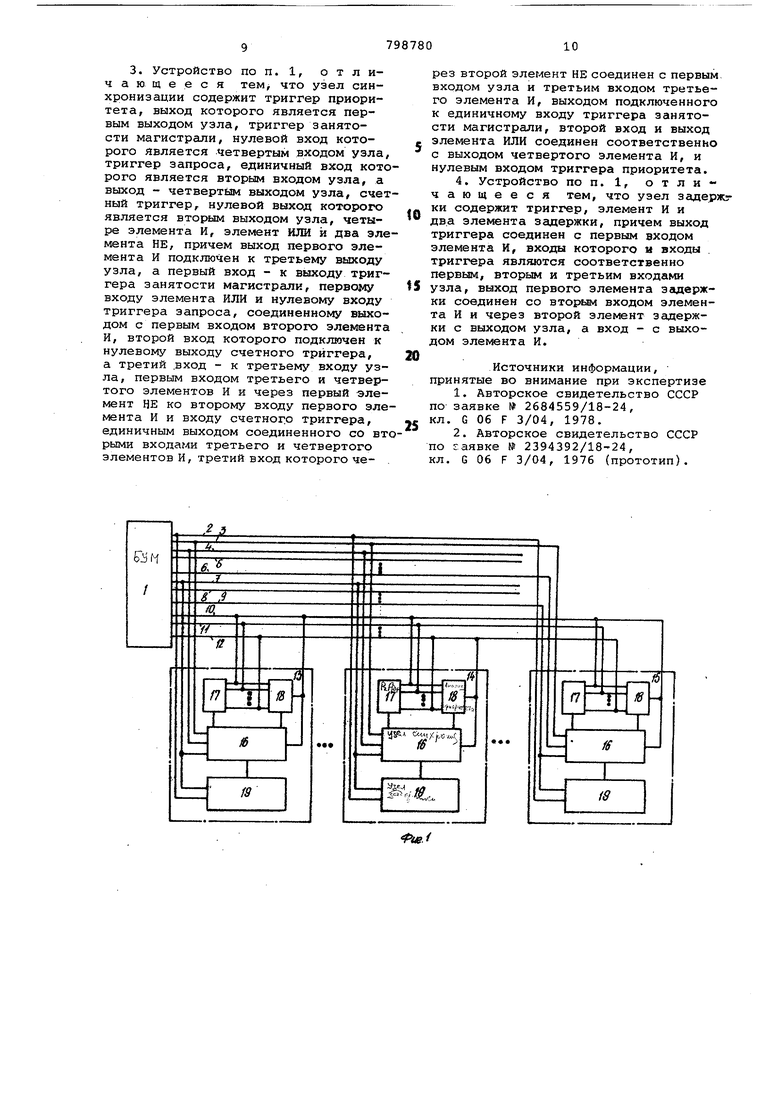

На фиг. 1 представлена блок-схема устройства; на фиг. 2 - функциональная схема каналов источников.

Устройство содержит блок 1 управления магистралью, шины 2 и 3 синхронизации устройства, шины 4, 5 и б запроса, : шины 7, 8 и & разрешения, каналы 13, 14 и 15 источников информации. В состав каждого канала 13, 14 и 15 входят узел 16 синхронизация, адресный регистр 17, узел 18 анализа приоритета и узел 19 задержки. В зависимости от уровня приоритета источники информации разделены на группы, причем число групп равно количеству шин запроса

0 4f 5 и б, а количество источников информации в одной группе не превышает количества адресных шин 10, 11 к 12 у каналов 13 и 14 источников информации, принадлежащих к одной

5 группе, четвертый выход узла 16 подключей к одной и той же шине запроса, например 4 запроса шине, а третий вход узла 16 и первый вход узла 19 подключены к шине 7 разрешения, соответствующей по уровню приоритета шине 4 запроса у каналов 15 источника информации, принадлежащего к другой группе, четвертый выход узла 16 синхронизации подключен, например, к шине 6 запроса, а третий вход узла 16 и первый вход узла 19 подключены к шине 9 разрешения, соответствую1цей по уровню приоритета шине 6 запроса. Выходы узлов 18 каналов 13 и 14 источников информации принадлежсвдих к одной группе, подключены к отдельным адресным шинам 10, 11-и 12. к одной и той же адресной шине 10 подключены выходы узлов 18 каналов 13 и 15 источников информации, принадлежащих к разным группам.

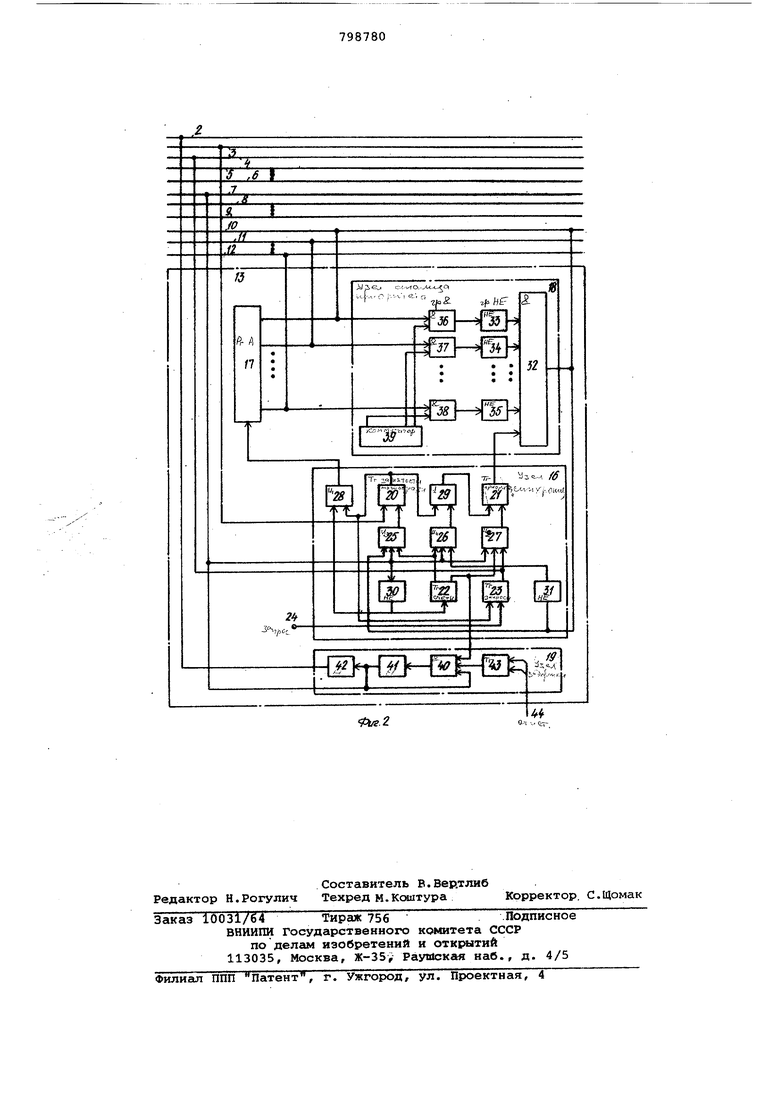

В сост.ав узла 16 синхронизации входят (фиг. 2) триггер 20 занятости магистрали, триггер 21 приоритета, счетный триггер 22, триггер 23 запроса, вход 24 запроса от источника, третий 25, четвертый 26, второй 27 и первый 28 элементы И, элемент ИЛИ 29, элементы НЕ 30 и 31.

Состав узла 18 анализа приоритета содержит (фиг. 2) элемент И 32, элементы НЕ 33, 34 и 35 группы, элемент И 36, 37 и 38 группы и коммутатор 39. В состав узла 19 задержки входят (фиг. 2) элемент И 40, элементы задержки 41 и 42, триггер 43 и вход 44 управления от источника.

Устройство работает следующим образом.

В исходном состоянии во всех блоках каналах 13, 14 и 15 триггеры 20, 21, 22 и 23 находятся в нулевом состоянии, программно управляемый источником триггер 43 также находится в нулевом.состоянии. Исключение составляют наиболее удаленные от блока 1 в каждой из -групп источников информации каналы, например канал 14, в которых программно управляемый триггер 43 находится в единичном состоянии.

При появлении у источников информации требования на подключение к общей магистрали в соответствукицих им каналах 13, 14 и 15 происходит установка триггера 23 запроса в единичное состояние и на соответствующих шинах 4, 5. и 6 запроса появится сигнал запроса. При появлении на одной или нескольких шинах 4, 5 и б сигнала запроса блок 1 начинает операцию выборки источника информации выдачей сигнала разрешения в одну из шин 7, 8 и 9 разрешения, соответствующую одной из возбужденных шин запроса, имеющей наиболее высокий уровень приоритета. Сигнал разрешения по выбранной шине разрешения, например по шине 7, поступает во все каналы 13 и 14 данной группы источников информации и через элемент И 27 устанавливает триггер 21 приоритета в единичное состояние в тех каналах, где триггер 23 находится в единичном состоянии. Кроме того, сигнал разрешения через элемент НЕ 30 подается на счетный вход счетного триггера 22 и задним фронтом устанавливает его в единичное

0 состояние. Сигнал с единичного выхода триггера 21 поступает на вход элемента И 32, сигнал приоритета на выходе которого, а следовательно и на одной из адресных шин появляется

5 только в том случае, если на другие входы элемента И32 с адресных 1Ш1н 10, 11 и 12 через .элементы И 36, 37 и 38 и элементы НЕ 33, 34 и 35 не поступает запрещающий сигнал от других источников информации данной

0 группы, имеющих более высокий приоритет . Распределение приоритетов между источниками инофрмации одной группы определяется состоянием коммутатора 39. У источника информации с

5 высшим приоритетом по сравнению с приоритетом других источников информации данной группы на один из входов всех элементов И 36, 37 и 38 с коммутатора 39 поступает нулевой по0тенциал. У источника информации с низшим приоритетом нулевой потенциал с коммутатора 39 поступает на один из входов только того элемента И 36, 37 и 38, другой вход которого

5 соединен с адресной шиной, подключенной к выходу элемента И 32. По мере распространения сигнала разрешения по шине 7 сигнал приоритета на выходе элемента И 32 сохраняется только в одном из каналов 13 и 14,

0 соответствующем источнику информации, имеющему более высокий приоритет по сравнению с приоритетом других источников информации данной группы, выставивших требование на

5 подключение к общей магистрали. Сигнал разрешения, достигая по шине 7 наиболее удаленного от блока 1 в данной группе источников информации канала 14, в котором триггер 43 на0ходится в единичном состоянии через элемент И 40 и элемент 41 задержки вновь поступает в ту же шину 7, а через элемент задержки 42 поступает в шину 2 синхронизации. Величина задержки элементов задержки 41 и 42

5 превышает время переходных процессов в каналах 13 и 14, соответственно по установке сигнала на выходе элемента И 32 и по установке сигнала на выходе адресного регистра 17.

0 Задержанный сигнал разрешения, распространяясь по шине 7 в направлении блока 1, поступает во все каналы данной группы источников информации. При этом во всех каналах 13 и

14, за исключением того у которого на выходе элемента И 32 сохранился сигнал приоритета, задержанный сигнал разрешения через элемент И 26 и элемент ИЛИ 29 устанавливает триггер 21 приоритета в нулевое состояние. Кроме того, в этих каналах, задержанный сигнал разрешения проходит через элемент НЕ 30 и задним фронтом устанавливает в нулевое состояние счетный триггер 22. В том канале 13 и 14, у которого на выходе элемента И 32 сохранился сигнал приоритета, задержанный сигнал разрешения через элемент И 25 устанавливает в единичное состояние триггер 20 занятия магистрали. Сигнал с единичного выхода триггера 20 устнавливает в нулевое состояние триггер 23 запроса и через элемент ИЛИ 29 триггер 21 приоритета. Кроме того, сигнал с единичного выхода триггера 20 через элемент И 28 поступает после окончания действия на его входе задержанного сигнала разрешения на вход управления адресного регистра 17. При этом с выхода адресного регистра 17 номер данного источника информации по адресным шинам 10, 11 и 12 поступает в блок 1 и записывается там задержанным сигналом разрешения, поступающим по шине 2 синхронизации. После приема номера данного источника информации блок 1 представляет ему право на пользование общей магистралью путем выдачи сигнала в шину 3 синхронизации, который устанавливает или подтверждает нулевое состояние триггера 20 во всех каналах 13, 14 и 15. На этом заканчивается операция выборки источника информации и блок 1 готов, начать новую операцию выборки после появления сигнала запроса на одной из шин запроса 4, 5 и 6. Отметим, что при отключении или выходе из строя наиболее удаленного От блока 1 в данной группе источников информации канала, его функции по формированию задержанного сигнала разрешения берет на себя следующий по удаленности от блока 1 канал, в котором программно изменяют состояние программно упра вляемого триггера 43 из нулевого в единичное.

Таким образом, устройство в условиях работы в вычислительных системах с магистральной структурой обмена информацией позволяет в процессе эксплуатации прц изменении комплектации или функционального назначени вычислительной системы легко изменять уровень приоритета подключенных к общей магистрали источников информации независимо от местоположения источников информации относительно друг друга и блока управления магистралью, эти изменения уровня приоритета источников информации

в пределах данной группы источнико информации достигают изменением сое тояния коммутаторов (коммутационных панелей) в каналах источников. Перевод источника информации из одной группы в другую осуществляют путем подключения его канала к соответствующим шинам запроса и шине разрешения.

Формула изобретения

1.Устройство для сопряжения источников информации с общей магистралью, содержащее группу каналов источников у каждый из которых включает узел анализа приоритетов, вход и выход которого соединены соответственно с первыми выходом и входом узла синхронизации, второй вход которого является -соответствующим входом запроса источника устройства, третий вход подключен к соответствующей входной шине разрешения устройства, и первому входу узла задержки, а второй выход - ко второму входу узла задержки, третий вход которого является соответствующим управляющим входом устройства, отличающееся тем, что,

с целью расширения функциональных возможностей устройства за счет обепечения возможности перераспределения приоритетов источников информации без изменения места их подключения к магистрали, в каждый канал источника введен адресный регистр, причем вход адресного регистра подключен к третьему выходу узла синхронизации, а группа выходов - к группе входов узла анализа приоритета и к группе адресных шин устройства, четвертый выход узла синхронизации соединен с соответствуквдей выходной шиной запроса устройства, а первый вход - с одним из выходов группы выходов адресного регистра, выход узла задержки и четвертый вход узла синхронизации подключены соответственно к первой и второй шинам узла синхронизации устройства.

2.Устройство по п. 1, отличающееся тем, что узел анализа приоритета содержит группу элементов И, группу элементов НЕ, выходной элемент И и коммутатор, причем первые входы элементов И группы подключены к соответствующим выходам коммутатора, вторые входы - к соответствующим входам из группы входов узла, а выходы - ко входам соответствующих элементов НЕ группы, выходы которых соединены с соответствунвдими входами выходного элемента И, вход и выход которого являются соответственно входом и выходом узла.

3. Устройство по п. 1, отличающееся тем, что узел синхронизации содержит триггер приоритета, выход которого является первым выходом узла, триггер занятости магистрали, нулевой вход которого Является четвертым входом узла, триггер запроса, единичный вход которого является вторым входом узла, а выход - четвертым выходом узла, счетный триггер, нулевой выход которого является вторым выходом узла, четыре элемента И, элемент ИЛИ и два элемента НЕ, причем выход первого элемента И подключен к третьему выходу узла, а первый вход - к выходу триггера занятости магистрали, первому входу элемента ИЛИ и нулевому входу триггера запроса, соединенному выходом с первым входом второго элемента И, второй вход которого подключен к нулевому выходу счетного триггера, а третий .вход - к третьему входу узла, первым входом третьего и четвертого элементов И и через первый элемент НЕ ко второму входу первого элемента И и входу счетного триггера, единичным выходом соединенного со втрыми входами третьего и четвертого элементов И, третий вход которого через второй элемент НЕ соединен с первым входом узла и третьим входом третьего элемента И, выходом подключенного к единичному входу триггера занятости магистрали, второй вход и выход элемента ИЛИ соединен соответственно с выходом четвертого элемента И, и нулевым входом триггера приоритета.

4, Устройство по п. 1, отличающееся тем, что узел згщержт ки содержит триггер, элемент И и

0 два элемента задержки, причем выход триггера соединен с первым входом элемента И, входы которого и входы триггера являются соответственно первым, вторым и третьим входами

S узла, выход первого элемента задержки соединен со вторым входом элемента И и через второй элемент задержки с выходом узла, а вход - с выходом элемента И.

0

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР по заявке № 2684559/18-24,

кл. G 06 F 3/04, 1978.

5

2.Авторское свидетельство СССР по саявке № 2394392/18-24,

кл. G 06 F 3/04, 1976 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения источников информации с общей магистралью | 1979 |

|

SU875373A2 |

| Устройство для управления приоритетным подключением абонентов к общей магистрали | 1980 |

|

SU892443A1 |

| Устройство для сопряжения двух процессоров с общей памятью | 1988 |

|

SU1569840A1 |

| Многоканальное устройство для обмена информацией | 1984 |

|

SU1359781A1 |

| Устройство приоритетного доступа к магистрали | 1990 |

|

SU1839249A1 |

| Многоканальное устройство для сопряжения абонентов с общей магистралью | 1984 |

|

SU1223237A1 |

| Устройство для сопряжения с общей маги-СТРАлью ВычиСлиТЕльНОй СиСТЕМы | 1979 |

|

SU809143A1 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1990 |

|

SU1728867A1 |

| Многоканальное устройство для подключения абонентов к общей магистрали | 1988 |

|

SU1524059A1 |

| Многоканальное устройство для приоритетного подключения источников информации к магистрали | 1988 |

|

SU1594539A1 |

Авторы

Даты

1981-01-23—Публикация

1979-02-05—Подача