Изобретение относится к вычислительной технике и может быть использовано в многомашинных или многопроцессорных вычислительных системах с магистральной структурой обмена информацией.

Известны устройства для сопряжения ЭВМ и других источников с магистралью обмена.:

Известно устройство для сопряжения цифровой вычислительной машины с общей магистралью вычислительной системы, содержащее блок синхронизации, входы-выходы которого соединены с управляющими шинами магистрали, регистр информации, группа информационных входов и управляющий вход которого соединены соответственно с первой группой входов и первым выходом блока управления, блок анализа

состояний магистрали, группа входов которого подключена к соответствующим управляющим шинам магистрали, группу приемников, группу передатчиков, входы группы приемников и выходы группы передатчиков подключены к информационным шинам магистрали, выходы группы приемников соединены с группой входов регистра информации, группа выходов которого является группой информационных выходов устройства, вторая группа входов, второй выход и первый вход блока управления являются соответственно группой адресных входов устройства, выходом управляющих признаков и входом опроса устройства, а третий выход соединён с первым входом блока синхронизации, первые вход и выход блока анализа состояния магистрали соедиго

00

00

о

йены с соответствующими приоритетными шинами магистрали, а второй вход соединен с входом запроса устройства, а также содержащее счетчик слов, счетчик текущего адреса, причем группы входов счетчика слов и счетчика текущего адреса соединены с выходами группы приемников, группы выходов - соответственно с группами информационных и адресных выходов устройства, первые управляющие входы - с четвертым выходом блока управления, а вторые управляющие входы - с входом опроса устройства, выход счетчика слов подключен к второму входу блока управления и к третьему входу блока анализа состояния магистрали, четвертый вход и второй выход которого являются соответственно входом ответа и выходом допуска подпрограммы устройства, второй вход блока синхронизации является входом управляющего признака устройства, блок анализа состояния магистрали, содержащий четыре триггера, два элемента И, элемент НЕ, приемник и передатчик, блок управления содержит схему сравнения, четыре триггера, два элемента И, узел коммутации, группы приемников и передатчиков, блок синхронизации содержит группу приемников, передатчиков, генератор, распределитель импульсов, триггер, элементы И, ИЛИ.

Устройство не позволяет подключать ЦВМ к управляющим и информационным шинам общей магистрали и создавать многомашинную вычислительную систему. Синхронизация ЦВМ вычислительной системы обеспечивается специальным блоком синхронизации. При одновременном запросе со стороны двух и более ЦВМ конфликтные ситуации разрешаются блоками анализа состояния магистрали. Приоритеты на подключение к магистрали определяются местоположением ЦВМ в многомашинном комплексе. При занятии магистрали ЦВМ переходит на управляющую программу подготовки устройств для обмена данными, которая осуществляется двумя операциями вывода двух управляющих слов, сопровождающихся сигналами синхронизации. После подготовки канала обмена ЦВМ - датчик инициирует обмен данных в магистрали, при этом передача каждого слова осуществляется в течение одного рабочего цикла ЭВМ (ЦВМ-датчик выдает два управляющих слова и выполняет команду возврата).

Построение многомашинной вычислительной системы с помощью дан н ых устройств требует большой группы управляющих и информационных шин, что снижает помехоустойчивость системы и затрудняет организацию многомашинного обмена между ЭВМ. Кроме того, многомашинная система, построенная при использовании данного устройства, предполагает наличие одного устройства, формирующего сетку тактовых

импульсов, и специального устройства для формирования специального строба синхронизации при выборе наиболее приоритетного устройства. При выходе из строя одного из этих устройств вся многомашин0 ная система оказывается неработоспособной. Отсутствие данных узлов в каждом устройстве обуславливает низкую надежность функционирования многомашинной системы.

5 Известно устройство для сопряжения, содержащее первый блок дешифрации адреса, входы которого соединены с адресными и управляющими входами устройства, регистр адреса, регистр данных, регистр ко0 манд, блок управления, управляющие входы которых соединены с выходами блока дешифрации адреса, а информационные входы - с информационными входами-выходами устройства, блок прерываний, входы которого

5 соединены с выходами блока управления, выходы регистра команд соединены с вторыми входами регистра данных и регистра состояний, с вторым входом-выходом блока уп- равления и с первым входом блока

0 прерываний, выход регистра данных соединен с вторыми информационными входами- выходами устройства, выход регистра адреса соединен с адресным входом-выходом устройства, третий выход блока управ5 ления соединен с вторым управляющим входом-выходом устройства, э также содержащее блок захвата магистрали, буферный регистр, второй блок дешифрации адреса, регистр прерываний, элемент ИЛИ, причем

0 первый вход-выход буферного регистра данных соединен с первым информационным входом-выходом устройства, первый вход - с выходом регистра команд, второй вход-с выходом блока дешифрации адреса,

5 входы блока захвата магистрали соединены с выходами первого блока дешифрации адреса, регистра команд, с входом разрешения доступа, с входом блока управления, а выходы соединены с выходом запроса до0 ступа к магистрали, с входом буферного регистра данных, входы второго блока дешифрации адреса соединены с адресным и управляющим входами-выходами устройства, а выходы с входами блока и регистра

5 прерываний. Данное устройство используется для сопряжения различных вычислительных средств, имеющих интерфейсы Общая шина и Магистраль и включенных по иерархической структуре. По инициативе процессора осуществляется обращение

к устройству и введение в него необходимой информации для организации обмена с другим устройством. После этого устройство осуществляет захват магистрали и производит необходимый обмен по интерфейсу Магистраль.

Недостатком данного устройства является отсутствие возможности выполнения арбитража захвата магистрали в случае формирования запросов на подключение к магистрали сразу в нескольких абонентах, подключенных к магистрали. Это требует наличия специального узла в системе, осуществляющего арбитраж подключения устройств к магистрали обмена, что усложняет систему в целом. Кроме того, для реализации данного устройства и его составных частей требуются значительные аппаратные затраты и значительное число линий связи, что также.усложняет систему в целом.

Известно устройство для сопряжения ЭВМ с магистралью обмена/содержащее дешифратор адреса, блок прерывания, регистр команд, регистр состояния, регистр данных источника, регистр адреса, блок захвата магистрали, два приемопередатчика, приемник, два передатчика, регистр адреса приемника, регистр данных приемника, элемент сравнения, три триггера, два элемента И, два элемента НЕ, группу элементов И, причем первый, второй информационные выходы, информационный вход и группа информационных входов первого приемопередатчика являются выходами, входом и группой входов устройства для подключения соответственно к входу требования прерывания, синхровходу, выходу разрешения прерывания и к группе управляющих входов ЭВМ, группа информационных входов приемника образует группу входов устройства для подключения к группе адресных выходов ЭВМ, группа информационных входов-выходов второго приемопередатчика образует группу входов-выходов устройства для подключения к группе информационных входов-выходов ЭВМ, группа информационных выходов регистра данных источника и группа информационных входов регистра данных приемника образуют группы выходов и входов устройства для подключения к информационной шине магистрали обмена, группа информационных выходов регистра адреса приемника и первая группа информационных входов элемента сравнения образуют группы выходов и входов устройства для подключения к адресной шине магистрали обмена, информационный выход первого передатчика и вход первого элемента НЕ являются выходом и входом устройства для подключения

к шине захвата источника магистрали обмена, информационный выход второго передатчика и первый вход первого элемента И являются выходом и входом устройства для

подключения к шине захвата приемника магистрали обмена, синхровход первого триггера, соединенный с входом записи регистра данных приемника, и выход второго элемента И являются входом и выходом устройства для

0 подключения к шине синхронизации источника магистрали обмена, единичный выход первого триггера, соединенный с первым информационным входом регистра состояния, и синхровход второго триггера, соеди5 ненный с входом второго элемента НЕ, являются выходом устройства для подключения к шине синхронизации приемника магистрали обмена, при. этом группа информационных выходов приемника сое0 динена с группой информационных входов дешифратора адреса, группа управляющих входов и первый выход которого соединены соответственно с группой информационных выходов и с первым информационным вхо5 дом первого приемопередатчика, второй информационный вход и информационный выход которого соединены соответственно с выходом требования прерывания и с входом разрешения прерывания блока преры0 вания, выход ответного сигнала которого соединен с информационным входом дешифратора адреса, второй выход которого соединен с управляющим входом второго приемопередатчика, группа информацион5 ных выходов которого соединена с группами информационных входов регистра команд, регистра адреса приемника и регистра источника, группа информационных выходов регистра данных приемника соеди0 нена с группой информационных выходов регистра состояния, с группой информационных входов второго приемопередатчика и с группой выходов вектора прерывания блока прерывания, группа разрешающих вхо5 дов которого соединена с группой информационных выходов регистра команд, вход записи которого соединен с третьим выходом дешифратора адреса, четвертый выход которого соединен с входом

0 чтения регистра состояния, второй информационный вход которого соединен с выходом первого элемента И, второй вход которого соединен с третьим информационным входом регистра состояния, с входом

5 чтения регистра адреса приемника, с информационным входом второго триггера, с входом чтения регистра данных источника, с информационным входом первого передатчика, с единичным, выходом третьего триггера и с первым входом запроса прерывания блока прерывания, второй вход запроса прерывания которого соединен с четвертым информационным входом регистра состояния, с информационным входом первого триггера, с информационным входом второго передатчика, с входом разрешения записи регистра данных приемника и с выходом элемента сравнения, вторая группа информационных входов которого соединена с группой младших разрядов первых вхо- дов элементов И группы и с группой информационных выходов регистра адреса, информационный вход которого соединен с первым информационным выходом регистра команд, второй информационный выход которого соединен с вторыми входами элементов И группы и с входом записи регистра адреса, информационный выход которого соединен со старшим разрядом первых входов элементов И групп, третьи входы кото- рых соединены с выходом первого элемента НЕ и с разрешающим входом блока захвата магистрали, вторая группа информационных входов которого соединена с выходами элементов И группы, разрешающий и такто- вый выходы блока захвата магистрали соединены соответственно с информационным входом и синхровходом третьего триггера, вход чтения регистра данных приемника соединен с нулевым входом первого триггера и с пятым выходом дешифратора адреса, шестой выход которого соединен с входом записи регистра данных источника и с нулевым входом второго триггера, нулевой выход которого соединен с пятым информационным входом регистра состояния и с первым входом второго элемента И, второй вход которого соединен с выходом второго элемента НЕ, седьмой выход дешифратора адреса соединен с входом записи регистра адреса прием- ника.

Устройство позволяет осуществлять обмен информацией между любыми ЭВМ, входящими в состав многомашинной вычислительной системы, массивами любой пере- менной длины. Для организации обмена устройства, имеющие запрос на подключение, осуществляют арбитраж приоритетов на подключение и выявление абонента с максимальным приоритетом. Обмен информацией между ЭВМ и устройством сопряжения осуществляется по инициативе ЭВМ в программном режиме.

Недостатком известного устройства является низкое быстродействие, обусловлен- ное ограниченными возможностями программного режима обмена между устройствами сопряжения и ЭВМ, требующего для каждой единицы передаваемых данных выполнять значительное число команд по

обеспечению буферизации данных, преобразования форматов, подсчета количества переданных сообщений, формирования адресов памяти и так далее и не позволяющего выполнять программную обработку массива при высокой скорости обмена данными и при высокой интенсивности потоков сообщений (в реальном масштабе времени) в вычислительной системе.

Кроме того, приоритетность подключения в известном устройстве определяется фиксированным кодом адреса устройства относительно магистрали обмена, что может привести к значительным задержкам подключения устройств с низким кодом адреса при высокой интенсивности подключения устройств с более высоким приоритетом.

Цель изобретения - повышение быстродействия и сокращение времени подключения абонентов с низким кодом приоритета.

В устройство для сопряжения ЭВМ с общей магистралью, содержащее дешифратор адреса, блок прерывания, регистр команд, регистр состояний, регистр данных источника, регистр данных приемника, регистр адреса, три триггера, первую группу элементов И, элемент сравнения, элемент развязки, два элемента И, два элемента НЕ, блок захвата магистрали, узлы приемопередатчиков адреса, данных и управляющих сигналов, входами-выходами подключенные к линиям общей шины ЭВМ, выходы приемопередатчиков управляющих сигналов и адреса соединены с входами дешифратора адреса, первый выход которого соединен с входом записи регистра команд, первый выход которого соединен с входом записи регистра адреса и с вторыми входами группы элементов И, первая группа входов которой соединена с выходами регистра адреса, старший разряд информационного входа которого соединен с вторым выходом регистра команд, управляющий выход дешифратора адреса соединен с управляющими входами приемопередатчиков данных, выходы которых соединены с информационными входами регистра команд, регистра данных источника, выходы которого соединены с линиями данных магистрали обмена, к которой подключены информационные входы регистра данных приемника, группа входов и выходов блока захвата магистрали и первая группа входов элемента сравнения, вторая группа входов которого соединена с выходами регистра адреса, входы приемопередатчиков данных соединены с кодовыми выходами блока прерывания, с выходами регистра данных приемника, с выходами регистра состояния, первый вход

которого соединен с первым входом блока прерывания, с управляющим входом регистра данных источника, с первым входом первого элемента И, с выходом третьего триггера, который через элемент развязки соединен с линией источника магистрали обмена, к которой подключен первый элемент НЕ, выход которого соединен с управляющим входом блока захвата магистрали и с третьими входами группы элементов И, выходы которых соединены с информационными входами блока захвата магистрали, информационный выход и выход строб-сигнала которого соединены соответственно с одноименными входами третьего триггера, второй выход дешифратора адреса соединен с управляющим входом регистра состояния, выход первого триггера соединен с четвертым входом регистра состояния и с первым входом второго элемента И, второй вход которого соединен с выходом второго элемента НЕ. вход которого соединен с входом сброса первого триггера и подключен к линии строб-сигнала приемника магистрали обмена, к которой подключен выход второго триггера и пятый вход регистра состояния, третий вход которого соединен с выходом первого элемента И, второй вход которого соединен с линией приемника магистрали обмена, пятый и шестой выходы регистра команд соединены с входами управления прерыванием блока прерывания, выход запроса и вход подтверждения блока прерывания подключен к приемопередатчикам управляющих сигналов, а выход ответного сигйала блока прерывания соединен с первым дополнительным входом дешифратора адреса, введены дополнительнотретий-ше- стой элементы И, два элемента И-НЕ, два элемента ИЛИ, элемент ИЛИ-НЕ, вторая группа элементов И, блок прямого доступа в память, дешифратор кода сообщения, счетчик слов, счетчик адреса, счетчик циклов обмена и четвертый триггер, вход установки в единицу которого соединен с выходом первого элемента И-НЕ, первый вход которого соединен с выходом элемента совпадения, выход четвертого триггера соединен с первым входом третьего элемента И, с информационным входом второго триг- гера, с первым входом первого элемента ИЛИ, с вторым входом регистра состояния, с вторым входом блока прерывания и с вторым входом блока прямого доступа, управ- ляющий вход которого соединен с седьмым выходом регистра команд, восьмой выход которого соединен с вторым входом третьего элемента И, выход которого соединен с линией признака приемника магистрали обмена, третий и четвертый выходы регистра

команд соединены с первыми входами второй группы элементов И, вторые входы которой соединены с первым входом блока прямого доступа в память, с первым входом второго элемента И-НЕ, с информационным входом первого триггера, с вторым входом первого элемента ИЛИ и с выходом третьего триггера, выходы второй группы элементов соединены с линиями управления магистрали обмена, к которым подключены входы дешифратора кода сообщения, первый выход которого соединен с вторым входом первого элемента И-НЕ, второй выход дешифратора соединен с первым входом пятого элемента И, второй вход которого соединен с выходом первого элемента ИЛИ, третий выход дешифратора соединен с третьим входом блока прямого доступа в память, с вторым входом второго элемента И-НЕ, с входом сброса четвертого триггера и с первым входом четвертого элемента И, второй вход которого соединен с линией строб-сигнала источника магистрали обмена, выход четвертого элемента И соединен со счетным входом второго триггера, с входом записи регистра данных при- емника, управляющий вход которого соединен с входом сброса второго триггера и с выходом элемента ИЛИ-НЕ, первый вход которого соединен с первым выходом блока прямого доступа в память и с вторым дополнительным входом дешифратора адреса, второй вход элемента ИЛИ-НЕ соединен с четвертым выходом дешифратора адреса, третий выход которого соединен с вторым входом второго элемента ИЛИ, первый вход которого соединен с вторым выходом блока прямого доступа в память, выход второго элемента ИЛИ соединен с входом записи регистра данных источника и с третьим входом второго элемента И-НЕ, выход которого соединён с входом установки в единицу первого триггера, инверсный выход которого соединен с четвертым входом блока прямого доступа в память, пятый вход которого соединен с выходом второго триггера, первый вход шестого элемента И соединен с входом первого элемента НЕ, второй вход шестого элемента И соединен с первым выходом регистра команд, выход шестого элемента И соединен со счетным входом счетчика циклов обмена, выходы которого соединены с второй группой входов элементов И первой группы, вход сброса счетчика циклов обмена соединен с инверсным выходом третьего триггера, вход сброса которого соединен с девятым выходом регистра команд, выход переполнения счетчика слов соединен с четвертым входом блока прерывания, третий вход которого

соединен с шестым входом блока прямого доступа в память и с третьим входом регистра состояния, шестой вход которого соединен с входом сброса первого триггера, информационные, выходы счетчиков слов соединены с входами приемопередатчиков данных, вход записи счетчика слов соединен с выходом пятого элемента И, управляющий вход счетчика слов соединен с пятым выходом дешифратора адреса, шестой выход которого соединен с входом записи счетчика адреса, информационные входы которого соединены с выходами приемопередатчиков данных, выходы счетчика адреса соединены с входами приемопередатчиков адреса, вход управления которых соединен с третьим выходом блока прямого доступа в память, с входом вычитания счетчика слов, со счетным входом и с управляющим входом счетчика адреса, входы и выходы сигналов захвата общей шины блока прямого доступа в память подключены к входам и выходам приемопередатчиков управляющих сигналов общей шины.

Отличие предлагаемого устройства от известных является возможность организации обмена массивами между любыми ЭВМ в многомашинной вычислительной системе без участия процессоров этих ЭВМ, что приводит к повышению скорости обмена сообщениями между устройствами, так как при этом значительно упрощаются функции процессора за счет сокращения ряда команд, обеспечивающих буферизацию данных, преобразование форматов, подсчет количества переданных данных, формирование адресов памяти и т.д.

Кроме того, устройство позволяет регулировать очередность подключения к магистрали обмена за счет анализа и введения в код приоритета на подключение к магистрали обмена кода количества занятий магистрали обмена другими абонентами в течение времени ожидания подключения данного устройства к магистрали обмена и тем самым упорядочить подключение абонентов с низким кодом адреса (приоритета) относительно магистрали обмена.

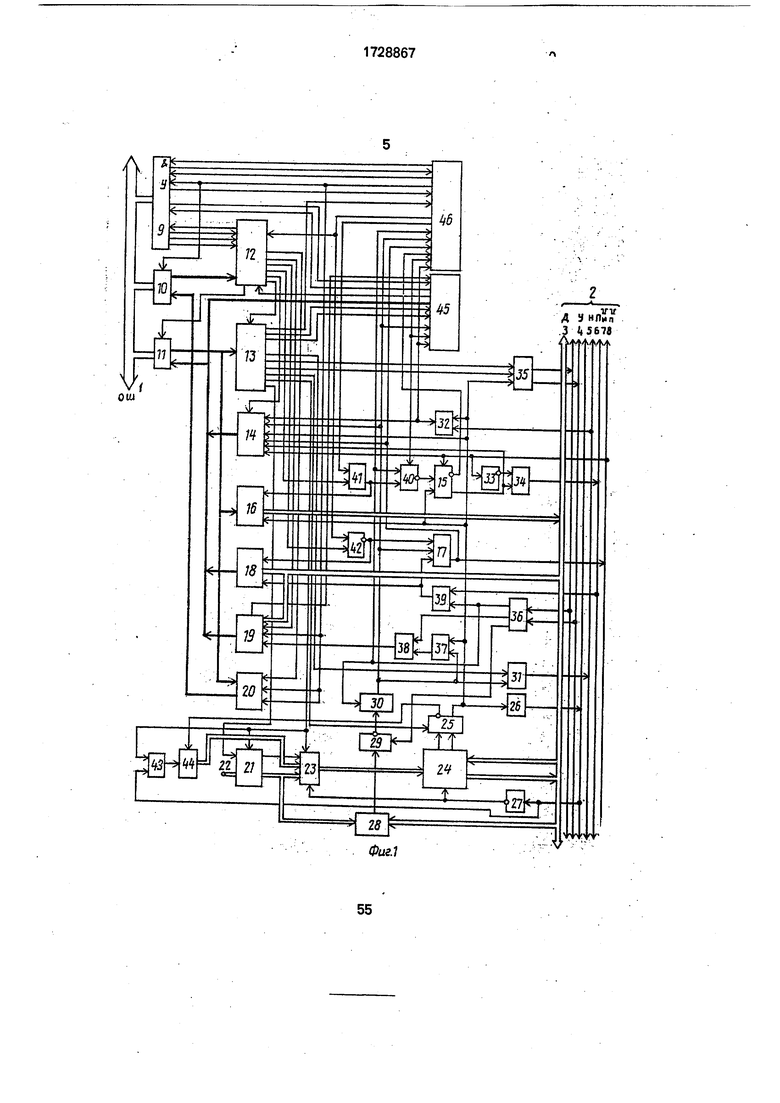

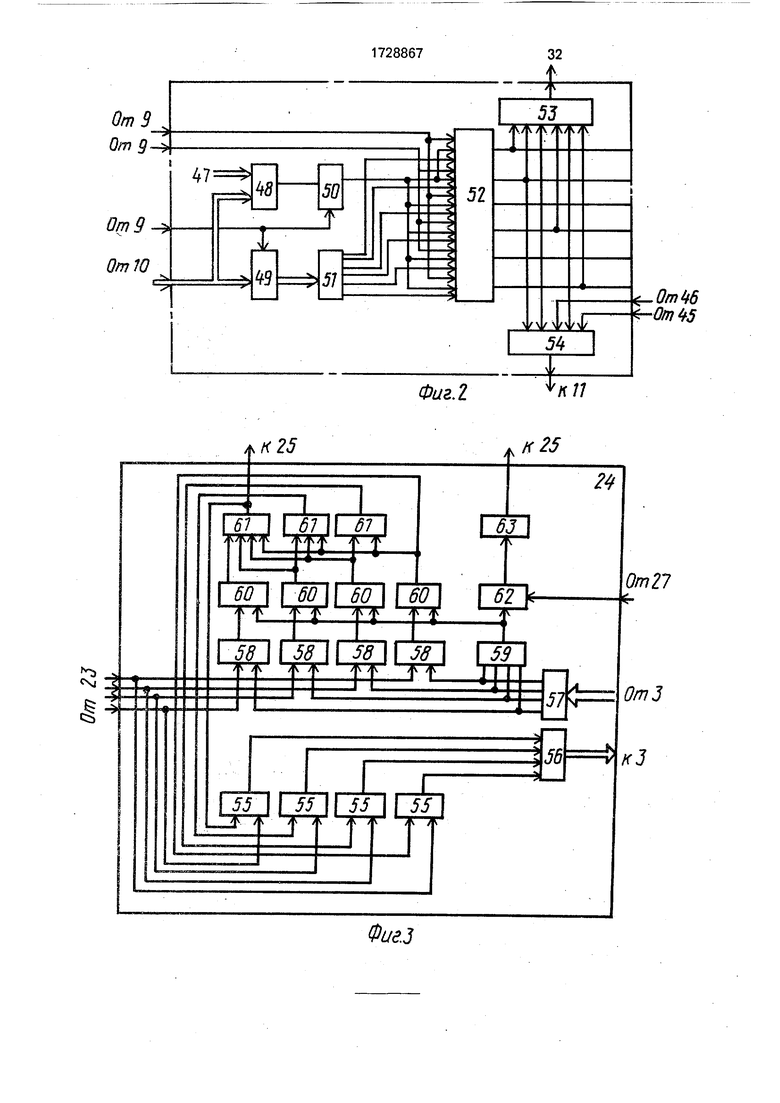

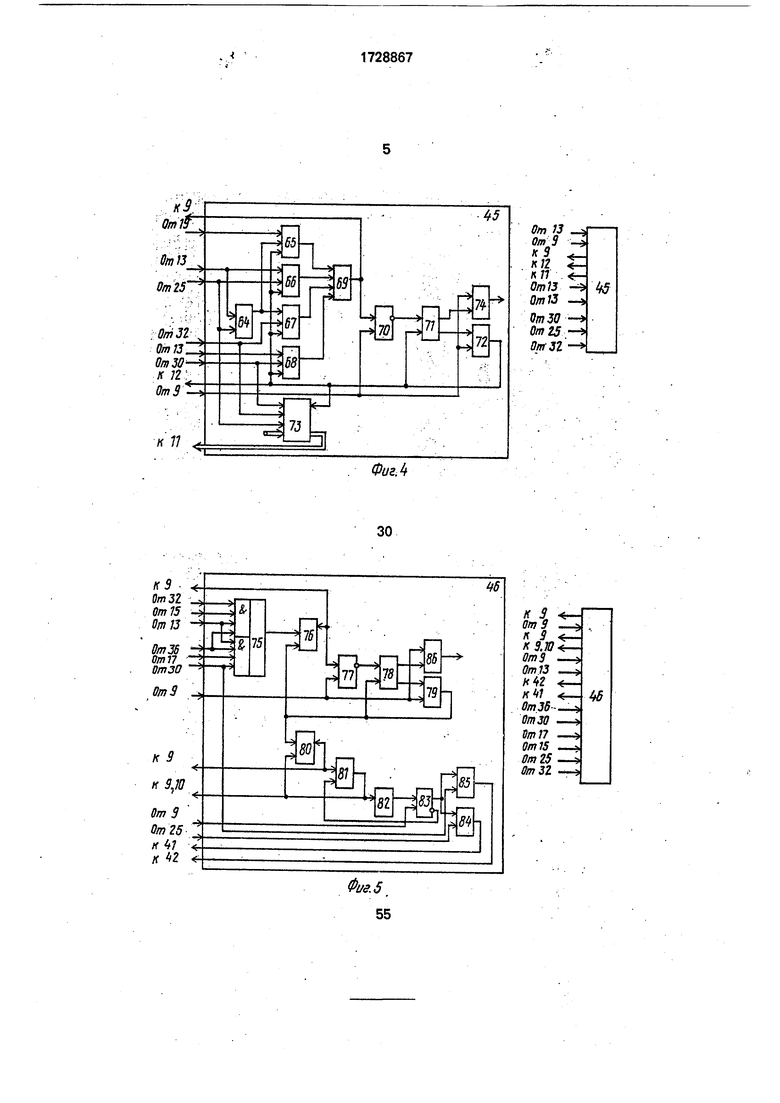

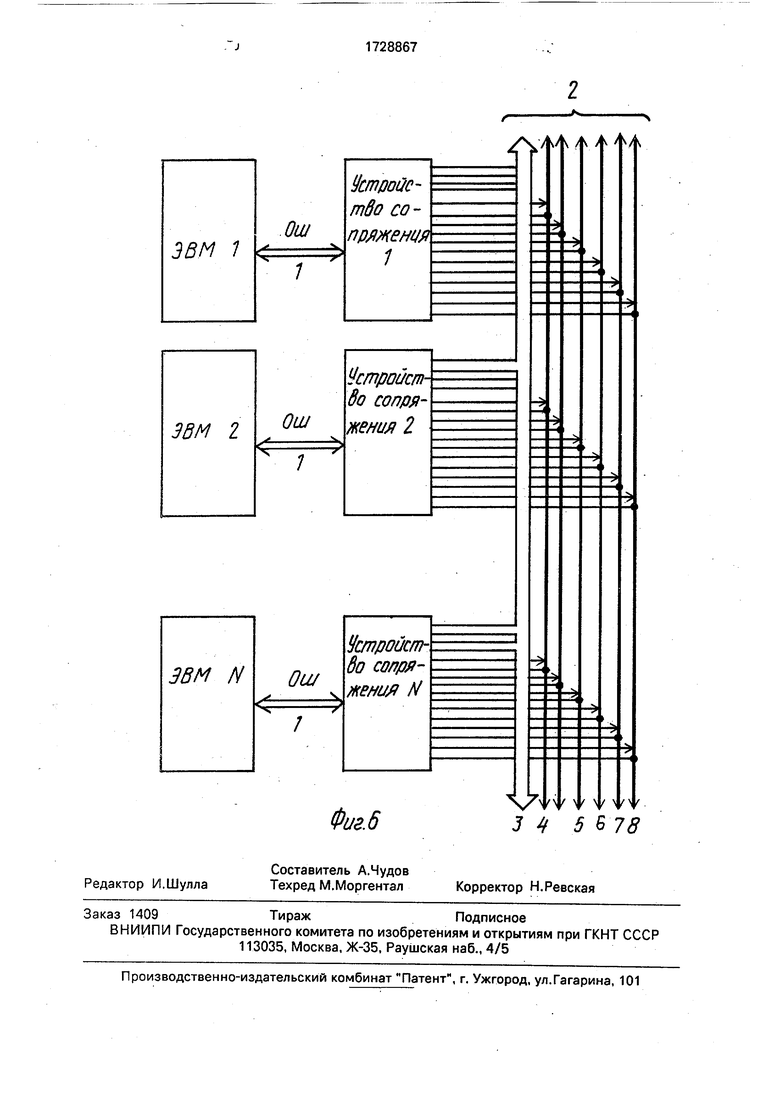

На фиг.1 приведена структурная схема предлагаемого устройства; на фиг.2 -структурная схема дешифратора адреса; на фиг.З - структурная схема блока захвата магистрали; на фиг.4 - структурная схема блока прерывания; на фиг.5 - структурная схема блока прямого доступа в память; на фиг.6 - схема использования устройства для сопряжения при создании многомашинных вычислительных систем.

На фиг.1 показаны общая шина 1 ЭВМ, магистраль 2 обмена, содержащая линии 3

данных, линий 4 управляющих сигналов, линию 5 признака источника, линию 6 признака приемника, линию 7 строб-сигнала источника, линию 8 строб-сигнала приемника.

Устройство для сопряжения ЭВМ с магистралью обмена содержит узел приемопередатчиков 9 управляющих сигналов, узел приемопередатчиков 10 адреса, узел при0 емопередатчиков 11 данных, дешифратор 12 адреса, регистр 13 команд, регистр 14 состояния, второй триггер 15, регистр 16 данных источника, первый триггер 17, регистр 18 данных приемника, счетчик 19 слов,

5 счетчик 20 адреса, регистр 21 адреса, кодовые входы 22, первую группу элементов И 23, блок 24 захвата магистрали, первый триггер 25, элемент 26 развязки, первый элемент НЕ 27, элемент 28 сравнения, пер0 вый элемент И-Н Е 29, четвертый триггер 30, третий элемент И 31, первый элемент И 32, второй элемент НЕ 33, второй элемент И 34, вторую группу элементов И 35, дешифратор 36, первый элемент ИЛИ 37. пятый элемент

5 И 38, четвертый элемент И 39, второй элемент И-НЕ 40, второй элемент ИЛИ 41, элемент ИЛИ-НЕ 42, шестой элемент И 43, счетчик 44 циклов, блок 45 прерывания, блок 46 прямого доступа в память.

0 Дешифратор 12 адреса содержит кодовые входы 47, элемент 48 совпадения, регистр 49, триггер 50, дешифратор 51, группу элементов И 52, первый 53 и второй 54 элементы ИЛИ.

5 Блок 24 захвата магистрали обмена содержит первую группу элементов И 55, группу передатчиков 56, группу приемников 57, группу элементов 58 эквивалентность, элемент ИЛ И-НЕ 59, группу элементов ИЛИ 60,

0 вторую группу элементов И 61, элемент И 62, одновибратор 63.

Блок 45 прерывания содержит элемент И 64, первый 65, второй 66, третий 67 и четвертый 68 триггеры, первый элемент

5 ИЛ И 69, элемент И-НЕ 70, пятый триггер 71, второй элемент ИЛИ 72, регистр 73 вектора прерывания, третий элемент ИЛИ 74.

Блок 46 прямого доступа в память содержит элемент И-ИЛИ-НЕ 75, первый

0 триггер 76, элемент И-НЕ 77, второй триггер 78, первый элемент ИЛИ 79, третий 80 и четвертый 81 триггеры, элемент 82 задержки, пятый триггер 83, первый элемент И 84, второй элемент И 85, второй элемент ИЛИ 86.

5 Линии данных общей шины 1 ЭВМ соединены с входами-выходами приемопередатчиков 11 данных, выходы которых соединены с информационными входами регистра 13 команд, регистра 16 данных ис- точника, счетчика 20 адреса, выходы которого соединены с входами приемопередатчиков 10 адреса, входы-выходы которых соединены с линиями адреса общей шины 1 ЭВМ, выходы приемопередатчиков 10 адреса соединены с входами дешифратора 12 адреса, входы и выходы управляющих сигналов которого соединены через приемопередатчики 9 управляющих сигналов с соответствующими линиями управляющих сигналов общей шины 1 ЭВМ.

Первый выход дешифратора 12 адреса соединен с входом записи регистра 13 команд, второй выход дешифратора 12 адреса соединен с управляющим входом регистра 14 состояния, третий выход дешифратора 12 адреса соединен с вторым входом элемента ИЛИ 41, первый вход которого соединен с вторым выходом блока 46 прямого доступа в память, первый выход которого соединен с первым входом элемента ИЛ И-НЕ 42, второй вход которого соединен с четвертым выходом дешифратора 12 адреса, пятый выход которого соединен с управляющим входом счетчика 19 слов, шестой выход дешифратора 12 адреса соединен с входом записи счетчика 20 адреса, управляющий и счетный входы которого соединены с входом вычитания счетчика 19 слов, с управляющим входом приемопередатчиков 10 адреса и с третьим выходом блока 46 прямого доступа в память. Выходы регистра 16 данных источника соединены с линиями 3 данных магистрали 2, к которой подключены входы-выходы блока 24 захвата магистрали, первая группа входов элемента 28 совпадения, информационные входы счетчика слов 19 и регистра 18 данных приемника, выходы которых объединены с кодовыми выходами блока 45 прерывания и соединены с входами приемопередатчиков 11 данных.

Первый выход регистра 13 команд соединен с вторыми входами группы элементов И 23, с входом записи регистра 21 адреса и с вторым входом шестого элемента И 43, выход которого соединен со счетным входом счетчика 44, выходы которого, а также выходы регистра 21 адреса соединены с первой группой входов группы элементов И 23, выходы которых соединены с информационными входами блока 24 захвата магистрали, информационный выход и выход строб-сигнала которого соединены с одноименными входами триггера 25, инверсный выход которого соединен с входом сброса счетчика 44. Кодовые входы 22 устройства соединены с информационными входами регистра 21 адреса, старший разряд которого соединен с вторым выходом регистра 13 команд, третий и четвертый выходы которого соединены с первыми входами группы элементов И 35, выходы которых соединены с линиями 4 управляющих сигналов магистрали 2, к которым подключены входы дешифратора 36, первый выход которого соединен с вторым входом элемента И-НЕ 29, первый вход которого соединен с выходом элемента 28 совпадения, выход элемента И-НЕ 29 соединен с входом установки в

0 единицу триггера 30, вход сброса которого соединен с первым входом элемента И 39, с. вторым входом элемента И-НЕ 40, с третьим входом блока 46 прямого доступа в память и с третьим выходом дешифратора 36,

5 второй выход которого соединен с первым входом элемента И 38, второй вход которого соединен с выходом элемента ИЛИ 37, выход элемента И 38 соединен с входом записи счетчика 19 слов, выход переполнения

0 которого соединен с четвертым входом блока 45 прерывания. Выход триггера 25 соединен с вторым входом элемента ИЛИ .37, с информационным входом триггера 15, с управляющим входом

5 регистра 16, с первым входом элемента И-НЕ 40, с первыми входами регистра 14 состояния, блока 45 прерывания, блока 46 прямого доступа в память, с первым входом элемента И 32, с вторыми входами группы

0 элементов И 35 и через элемент 26 развязки соединен с линией 5 источника магистрали 2, которая соединена с первым входом элемента И 43 и с входом элемента НЕ 27, выход которого соединен с управляющим

5 входом блока 24 захвата магистрали и с третьими входами группы элементов И 23. Выход триггера 30 соединен с информационным входом триггера 17, с вторым входом регистра 14 состояния, с вторыми входами

0 блока 45 прерывания и блока 46 прямого доступа в память и с первым входом элемента И 31, второй вх-од которого соединен с восьмым входом регистра 13 команд, девятый выход которого соединен с входом

5 сброса триггера 25.

Выход элемента И 31 соединен с линией 6 приемника магистрали 2, которая подключена к второму входу элемента И 32, выход которого соединен с шестым входом блока

0 46 прямого доступа в память, с четвертым входом блока 45 прерывания и с третьим входом регистра 14 состояния, четвертый вход которого соединен с выходом триггера 15 и с вторым входом элемента И 34, первый

5 вход которого соединен с выходом элемента НЕ 33, выход элемента И 34 соединен с линией 7 строб-сигнала магистрали 2, которая соединена с вторым входом элемента И 39, выход которого соединен со счетным входом триггера 17 и с входом записи регистра 18, управляющий вход которого соединен с выходом элемента ИЛИ-НЕ 42 и с входом сброса триггера 17, выход которого соединен с пятым входом регистра 14 состояния, с пятым входом блока 46 прямого до- ступа в память и подключен к линии 8 строб-сигнала магистрали 2, которая соединена с входом элемента НЕ 33, с шестым входом регистра 14 состояния и с входом сброса триггера 15, вход установки в едини- цу которого соединен с выходом элемента И-НЕ 40, третий вход которого соединен с входом записи регистра 16 и с выходом элемента ИЛ И 41, Выход запроса прерывания, вход подтверждения прерывания блока 45 прерывания, а также входы-выходы сигналов занятия магистрали блока 46 прямого доступа в память соединены через приемопередатчики 9 управляющих сигналов к линиям общей шины 1 ЭВМ, седьмой выход регистра 13 команд соединен с входом управления блока 46 прямого доступа в память, выход ответного сигнала блока 45 прерывания соединен с первым дополнительным входом дешифратора 12 адреса.

В дешифраторе 12 адреса первая группа входов элемента 48 совпадения соединена с кодовыми входами 47 адреса, вторая группа входов элемента 48 совпадения и информационные входы регистра 49 соеди- нены с информационными входами дешифратора 12 адреса, выход элемента 48 совпадения соединен с информационным входом триггера 50, счетный вход которого соединен с входом записи регистра 49 и с управляющим входом дешифратора 12 адреса, выходы регистра 49 соединены с входами дешифратора 51, выходы которого соединены с первой группой входов группы элементов И 52, вторые входы которой сое- динены с выходом триггера 50, третьи входы группы элементов И 52 соединены с входами управления дешифратора 12 адреса, выходы группы элементов И 52 соединены с первым - шестым выходом дешифратора 12 адреса и с входами элементов ИЛИ 53 и 54, выходы которых соединены с выходами сигналов управления дешифратора 12 адреса, первый и второй дополнительные входы дешифратора 12 адреса соединены с входами элемента ИЛИ 54.

В блоке 24 захвата магистрали его информационные входы подключены к первым входам элементов 58 эквивалентность и элементов И 55, выходы которых через передатчики 56 соединены с линиями 3 данных, которые.подключены через приемники 57 к вторым входам элементов 58 эквивалентность и входам элемента ИЛИ-НЕ 60,

выход которого соединен с первым входом элемента И 62 и первыми входами элементов ИЛИ 60, вторые входы которых соединены с выходами элементов 58 эквивалентность, выходы элементов ИЛИ 60 соединены с входами элементов И 67, выходы которых, а также выход старшего элемента ИЛИ 60 соединены с вторыми входами элементов И 55. Управляющий вход блока 24 соединен с вторым.входом элемента И 62, выход которого соединен с входом одновибратора 63, выход которого соединен с выходом строб-сигнала блока 24, информационный выход которого соединен с выходом младшего элемента И группы 61.

В блоке 45 прерывания первый вход соединен со счетным входом триггера 66, первым входом регистра 73 и первым входом элемента И 64, второй вход которого соединен с первым входом управления прерыванием блока 45 и информационным входом триггера 66, выход элемента И 64 соединен с информационными входами триггеров 65 и 67, счетный вход триггера 65 соединен с четвертым входом блока 45, выход триггера 65 соединен с первым входом элемента ИЛИ 69, второй вход которого соединен с выходом триггера 66, третий вход элемента ИЛИ 69 - с выходом триггера 67, счетный вход которого соединен с третьим входом блока 45 и вторым входом регистра 73, третий вход которого соединен с вторым входом блока 45 и счетным входом триггера 68, информационный вход которого соединен с вторым входом разрешения прерывания блока 45, выход триггера 68 соединен с четвертым входом элемента ИЛИ 69, выход которого соединен с выходом запроса блока 45 и первым входом элемента И-НЕ 70, выход которого соединен с входом установки в единицу триггера 71, прямой и инверс- ный выходы которого соединены соответственно с первыми входами элементов ИЛИ 72 и 74, вторые входы которых соединены с вторым входом элемента И-Н Е 70 и входом подтверждения блока 45, выход элемента ИЛИ 72 соединен со счетным входом триггера 71, входом сброса триггеров 65-69, выходом ответного сигнала блока 45 и управляющим входом регистра 73, выходы которого соединены с кодовыми выходами блока 45. В блоке 46 прямого доступа в память ЭВМ второй, третий, пятый входы и вход управления соединены с входами элемента И-ИЛИ-НЕ 75, третий, четвертый, шестой входы и вход управления соединены с другими входами элемента И-ИЛИ-НЕ 75, выход которого соединен со счетным входом триггера 76, выход которого соединен с выходом требования прямого доступа блока

46 и с первым входом элемента И-НЕ 77, выход которого соединен с входом установки в единицу триггера 78, прямой и инверсный выходы которого соединены соответственно с первыми входами элементов ИЛИ 79 и 86, вторые входы которых соединены с вторым входом элемента И-НЕ 77 и входом подтверждения прямого доступа блока 46, выход элемента ИЛИ 79 соединен со счетным входом триггера ;78, входом сброса триггера 76 и входом установки в единицу триггера 80, выход которого соединен с выходом подтверждения блока 46 и входом установки в единицу триггера 81, выход которого соединен третьим выходом блока 46, счетным входом триггера 80 и через элемент 82 задержки с входом установки в единицу триггера 83, инверсный выход которого соединен со счетным входом триггера 81, выход триггера 83 соединен с первыми входами элементов И 84 и 85, вторые входы которых соединены соответственно с первым и вторым входами блока 46, выходы элементов И 84 и 85 соединены соответственно с вторым и первым выходами блока 46, вход ответа общей шины которого соединен с входом сброса триггера 83.

Устройство работает следующим образом.

В начальный момент производится установка триггеров 15, 17, 25 и 30, регистра 13 в нулевое состояние, на входы регистра 21 подается код приоритета устройства на подключение к магистрали обмена. В магистрали 3 данных устанавливается исходное состояние, на выходе элемента ИЛИ-НЕ 59 - единичный сигнал, на выходах элементов ИЛИ 60, И 61 - единичный сигнал, который подается на входы элементов И 55 (цепи начальной установки не показаны).

Устройство для сопряжения является внешним устройством для ЭВМ и представляет шесть программно-доступных регистров: регистр 13 команд ЭВМ, регистр 14 состояния устройства, регистр 16 данных источника, регистр 18 данных приемника, счетчик 19 слов, счетчик 20 адреса.

Регистр 13 команд является девятиразрядным и содержит первый разряд - признак запроса на подключение устройства к магистрали обмена; второй разряд - признак передачи срочного сообщения; третий, четвертый разряды - признаки передаваемого сообщения. При коде 10 в третьем и четвертом разрядах регистра команд в регистр 16 данных записывается код адреса приемного устройства, при коде 01 - код длины массива передаваемого сообщения, при коде 11 в регистр 16 записываются слова (байты) передаваемого массива; пятый,

шестой разряды - разрешение прерывания соответственно источника и приемника информации; седьмой разряд - разрешение режима прямого доступа в память ЭВМ;

восьмой разряд - признак готовности приемной ЭВМ к приему сообщения из магистрали; девятый разряд - признак сброса триггера источника сообщения.

Обращение к регистрам со стороны

0 ЭВМ осуществляется путем установки на адресных шинах общей шины адреса одного из регистров и селекции установленного адреса дешифратором 12 адреса. На первых входах 47 элемента 48 сравнения установ5 лен групповой адрес регистров, представляющий код старших разрядов адресов регистров. В момент установки на общей шине адреса регистра на входе элемента 48 сравнения формируется единичный сигнал,

0 который записывается в триггер 50 единичным сигналом, стробирующим адрес. Этим же сигналом код младших разрядов адреса записывается в регистр 49 и поступает на входы дешифратора 51 кодов, который име5 ет шесть выходов и формирует единичный сигнал только на выходе, соответствующем регистру, к которому осуществляется обращение. На выходе элементов И 52 единичный сигнал формируется к моменту

0 установки на общей шине сигналов, строби- рующих данные, на выходе элемента ИЛИ 53 формируется ответный сигнал устройства при обращении ЭВМ к регистру устройства. Единичным сигналом с выхода

5 элемента ИЛИ 54, формируемым при чтении регистров, осуществляется подключение общей шины к выходам регистров 14, 18м 19, нулевым сигналом осуществляется подключение общей шины через приемники к

0 входам регистров 13, 16 и 20.

Процесс обмена сообщениями в режиме прямого доступа в память производится по инициативе ЭВМ - источника сообщения. Для организации обмена устройство 5 источник сообщения производит захват магистрали только в случае отсутствия обмена по магистрали, становится источником сообщения, производит передачу адреса приемного устройства, принимает сигнал о

0 готовности приемной ЭВМ к обмену, принимает от Э ВМ код длины передаваемого массива и начальный адрес ячейки памяти, из которой производится чтение массива, и получает канал ЭВМ (общую шину 1) для

5 вывода массива данных из памяти ЭВМ.

В устройстве - приемнике сообщения производится анализ адреса приемного устройства, формирование признаков устройства - приемника, признака готовности ЭВМ к приему массива данных, запись кода

длины принимаемого сообщения, начального адреса ячейки памяти, в которую производится запись принятого массива и занятие общей шины ЭВМ приемника.

Для захвата магистрали обмена ЭВМ - источник обращается к регистру 13 команд и устанавливает в первом разряде регистра сигнал Запрос и единичный сигнал во втором разряде регистра 13, если сообщение является срочным. Сигнал Запрос посту- пает на вход записи регистра 21 и вторые входы элементов И 23. Если общая магистраль 1 обмена свободна, то на шине 5 источника имеет место нулевой потенциал, на третьих входах элементов И 23 - единичный потенциал, поэтому в случае свободной магистрали 1 обмена в момент установки сигнала Запрос с выходов регистра 21 на входы блока 24 захвата магистрали через элементы И 23 начинает поступать код при- оритета данного .устройства на подключение к магистрали обмена и код (нулевой в случае начала работы) с выходов счетчика 44.

Рассмотрим работу блока 24 захвата ма- гистрали в случае одновременного поступления сигнала Запрос сразу в нескольких устройствах сопряжения, подключенных к магистрали.

В момент формирования сигнала За- прос с выходов регистра 20 код приоритета, бит срочности (если сообщение срочное) и код с выходов счетчика 44 через элементы И 23, группу элементов И 55 и передатчики 56 поступают в магистраль 3, где устанав- ливается результирующий потенциал монтажного или во всех устройствах, подключенных к общей магистрали 1 обмена, на выходе элемента ИЛИ-НЕ 59 формируется нулевой потенциал. Данный элемент ИЛИ- НЕ 59, а также элементы ИЛИ 60 предназначены для исключения прохождения сигналов с выходов элементов 58 эквивалентность на входы элементов И 61 на время переходных процессов, возникающих из-за различия пути прохождения сигналов на первые и вторые входы элементов 58 эквивалентность. С помощью элементов 58 эквивалентность осуществляется сравнение в каждом разряде потенциала бита приорите- та данного устройства и результирующего потенциала, который имеет место в общей магистрали обмена. В старших разрядах осуществляется сравнение бит срочности. Если потенциалы старших бит совпадают, то на выходе элемента 58 эквивалентность формируется единичный потенциал, который поступает на входы элементов И 55 и разрешает дальнейшую выдачу в магистраль 3 бит приоритета из данного устройства.

Если потенциалы бит в старшем разряде не совпадают, то на выходе элемента 58 эквивалентность старшего разряда формируется нулевой потенциал. Это означает, что в общей магистрали обмена одновременно подключается аналогичное устройство с более высоким приоритетом, чем данное. В этом случае на вход элементов И 61 с выхода старшего элемента 58 эквивалентность поступает нулевой сигнал, который с помощью элементов И 55 блокирует выдачу кода приоритета из данного устройства. Если в устройстве потенциалы старших бит совпали, то осуществляется сравнение потенциалов бит следующих младших разрядов. Если в.каком-то разряде потенциалы бит не совпадают, то на выходе элемента 58 эквивалентность в данном разряде формируется нулевой сигнал, который подается на входы элементов И 61 данного и младших разрядов и отключает выходы регистра 21 младших разрядов от магистрали обмена с помощью элементов И 55 младших разрядов.

После сравнения кодов приоритета во всех разрядах только в одном устройстве на выходе младшего элемента И 61 остается единичный сигнал, который поступает на информационный вход триггера 25. На син- хровход данного триггера поступает сигнал с выхода одновибратора 63, который запускается в случае свободной магистрали обмена (на магистрали 5 - нулевой сигнал) после формирования отрицательного перепада на выходе элемента ИЛИ-НЕ 59, и формирует импульс, длительность которого больше времени срабатывания элементов И 55, 61, эквивалентность 58, необходимого для определения устройства с максимальным приоритетом. Задним фронтом импульса с выхода одновибратора 63 единичный сигнал с информационного входа, соединенного с выходом элемента И .61, записывается в триггер 25. Единичный сигнал с выхода триггера 25 характеризует данное устройство как источник и переводит в активное состояние выходы регистра 16, а также через передатчик 26 поступает на шину 5, откуда через элемент НЕ 27 во всех устройствах, подключенных к магистрали обмена, поступает на вход элемента И 23, отключает выходы блока 24 захвата магистрали от магистрали 3 и блокирует в дальнейшем работу блока 24 захвата магистрали.

Кроме того, в устройстве - источнике сообщения единичный сигнал с выхода триггера 25 поступает в первый разряд регистра состояния и блок прерывания, где в случае разрешения прерывания источника (единичный сигнал в пятом разряде регистpa команд) производится установка в единичное состояние триггера 66, формирующего в общую шину ЭВМ сигнал требования прерывания, в ответ на который ЭВМ формирует сигнал разрешения прерывания. Данный сигнал через элемент И-НЕ 70 осуществляет установку в единичное состояние триггера 71, сброс триггера 66 и переводит в активное состояние выходы регистра 73 вектора прерывания.

После чтения вектора прерывания источника ЭВМ переходит на подпрограмму источника: обращается к счетчику 20 адреса и записывает начальный адрес ячейки памяти ЭВМ, из которой необходимо осуществ- лять вывод информации, в регистр 16 данных источника записывается адрес приемного устройства, в которое необходимо передавать сообщение, в третий, четвертый разряды регистра 13 команд записывается код 10, характеризующий наличие в регистре 16 данных и магистрали 3 кода адреса приемного устройства.

Во всех устройствах, подключенных к магистрали, в элементе 28 сравнения произ- водится сравнение кода адреса приемного устройства, находящегося в магистрали 3, и кода собственного адреса с выходов регистра 21. При совпадении этих кодов на выходе схемы 28 сравнения формируется единич- ный сигнал, который поступает на первый вход элемента И-НЕ 29, на второй вход ко- торого поступает единичный сигнал с первого выхода дешифратора 36, характеризующий в магистрали наличие кода адреса приемного устройства, и устанавливает триггер 30 в единичное достояние.

В устройстве - приемнике сообщения ЭВМ всегда разрешает прерывание начала приема путем установки единичного сигна- ла в шестом разряде регистра 13 команд. В момент формирования единичного сигнала на выходе триггера 30 положительным перепадом осуществляется я установка триггера 68 в единичное состояние. При этом производится выдача в общую шину сигнала требования прерывания, прием сигнала подтверждения прерывания, обнуление триггера 68 и выдача вектора прерывания приемного устройства.

После анализа данного вектора прерывания ЭВМ переходит на подпрограмму приема: осуществляет анализ второго разряда регистра 14 состояния, запись в счет- чик20 адреса кода начальной ячейки памяти ЭВМ, в которую записывается принимаемый массив, затем ЭВМ устанавливает единичный сигнал в седьмом и восьмом разрядах регистра 13 команд, характеризующий готовность ЭВМ к приему массива

данных, при этом приемное устройство на выходе элемента И 31 формирует единичный сигнал, который поступает в линию 5. В устройстве - источнике при этом формируется единичный сигнал на выходе элемента И 32, который поступает в блок прерываний и устанавливает в единичное состояние триггер 67. Блок прерывания после выполнения процедуры прерывания устанавливает на общую шину вектор прерывания, характеризующий готовность приемного устройства к началу обмена. После анализа принятого вектора прерывания ЭВМ - источник записывает в регистр 16 данных код длины передаваемого массива, который поступает в магистраль 3, а в регистр 13 команд в шестом и седьмом разрядах записывает код 01, характеризующий наличие в линии кода длины массива. Данный код поступает на информационные входы счетчика 19 слов и в устройстве - источнике и приемнике записывается в данный счетчик сигналом с выхода элемента И 38. После этого ЭВМ - источник обращается к регистру 13 команд и устанавливает в третьем, четвертом и седьмом разрядах единичные сигналы, которые с третьих и четвертых разрядов поступают через элементы И 35 в магистраль 4 и приводят к формированию единичного сигнала на третьем входе дешифратора 36,

После этого начинается обмен информацией в режиме прямого доступа в память ЭВМ. В устройстве - источнике в момент формирования единичного сигнала на третьем выходе дешифратора 36 (на инверсном выходе триггера 15 имеет место единичный сигнал) при разрешенном режиме ПДП производится установка в единичное состояние триггера 76, формирующего сигнал требования прямого доступа. ЭВМ, получив данный сигнал, формирует ответный сигнал подтверждение прямого доступа, который устанавливает в единичное состояние триггер 78, в нулевое состояние триггер 76, в единичное состояние триггер 80, который информирует все устройства, подключенные к общей шине ЭВМ, о занятии общей шины 1. Единичным сигналом с выхода триггера 80 производится установка в единичное состояние триггера 81. Данный сигнал переводит в активное состояние выходы регистра 20 и переключает приемопередатчик 10 на передачу в ОШ кода адреса и управляющих сигналов, необходимых для организации обмена. В устройстве - источнике в ОШ устанавливается адрес ячейки памяти, из которой производится считывание слова данных. Сигналом с выхода элемента И 86 производится запись считанного

слова данных в регистр 16 и установка в единичное состояние триггера 15. Данные с выходов регистра 16, переведенные в активное состояние в устройстве - источнике, единичным сигналом с выхода триггера 25, передаются в магистраль 3 и далее на входы регистра 18 в приемном устройстве. Строб- сигнал данных поступает с выхода триггера 15 через элемент И 33 в магистраль 7, далее в приемном устройстве производит запись данных с магистрали в регистр 18 и устанавливает триггер 17 в единичное состояние. Единичный сигнал с выхода триггера 17 поступает в магистраль 8 и производит в устройстве - источнике установку триггера 15 в нулевое состояние. Единичный сигнал с инверсного выхода триггера 15 поступает в блок прямого доступа, где производится следующий цикл захвата ОШ в запись в регистр 16 следующего слова данных из ячейки памяти, определяемой кодом адреса в регистре.

В приемном устройстве единичный сигнал с выхода триггера 17 поступает в блок прямого доступа и производит установку триггера 76 в единичное состояние. Выполнение процедуры занятия ОШ осуществляется так же, как и в устройстве - источнике. При получении ответного сигнала подтверждения прямого доступа производится сброс триггера 76, установка в единичное состояние триггеров 81 и 83, занятие ОШ, перевод в активное состояние выходов регистра 20, переключение приемопередатчиков 10 на выдачу в ОШ адреса ячейки памяти ЭВМ, в которую производится запись данных из регистра 18, выходы которого переводятся в активное состояние сигналом с выхода элемента ИЛИ 42. Этим же сигналом (задним фронтом) производится сброс триггера 17 в нулевое состояние, задним фронтом сигнала с выхода элемента И 85 - изменение адреса следующей ячейки памяти в счетчике 20 и уменьшение на единицу содержимого счетчика 19.

Если в устройстве - источнике в регистре 16 записано следующее, слово данных, то в момент окончания чтения содержимого регистра 18 и сброса триггера 17 в устройстве - источнике на выходе элемента И 34 формируется очередной строб-сигнал и запись очередного слова данных в регистр 18, и процессы захвата ОШ и передачи устройством принятого слова данных в приемную ЭВМ продолжаются.

В процессе обмена массивами данных в устройстве - источнике и устройстве - приемнике производится изменение содержимого счетчика 19 слов и изменения кода адреса ячейки памяти, формируемого счетчиком 20 адреса. В момент передачи последнего слова данных в устройстве - источнике при обнулении содержимого счетчика 19 на дополнительном выходе счетчика 19

формируется сигнал, который поступает в блок 45 прерывания, устанавливает в единичное состояние триггер 65. Блок прерывания выполняет процедуру прерывания и устанавливает в общую шину ЭВМ вектор

0 прерывания, характеризующий окончание вывода устройством массива данных. В этом случае ЭВМ анализирует четвертые и шестые разряды регистра 14 состояний и в случае свободных регистра 16 в устройстве

5 - источнике и регистра 18 в устройстве - приемнике производит формирование единичного сигнала в девятом разряде регистра 13 команд, который производит сброс триггера 25. В этом случае устройство - ис0 точник прекращает захват магистрали 2 обмена, освобождает линию 5 и формирует нулевой код в линии 4. В устройстве - приемнике производится формирование нулевого кода на третьем выходе дешифратора

5 36, сброс триггера 30 и освобождения линии 6 магистрали 2 обмена.

На этом процесс обмена между устройствами - источником и приемником заканчивается, начинается новый процесс

0 захвата магистрали обмена другими устройствами, имеющими запрос на подключение. В тех устройствах, в которых имеется запрос на подключение, но не занявших магистраль за счет низкого приоритета на под5 ключение, с помощью счетчика 44 в течение наличия запроса на подключение (единичный сигнал на первом выходе регистра 13 команд) производится подсчет количества раз занятия магистрали 2 другими устройст0 вами (количество единичных сигналов на ли- нии 5 источника) и увеличение кода приоритета за счет подачи кода с выхода счетчика 44 в более старшие разряды, чем код с выхода регистра 21.

5 Кроме того, устройство позволяет выполнять обмен массивами любой заранее неизвестной длины. В этом случае в устройстве - источнике в момент передачи кода длины массива передается максимальный

0 код, который затем записывается в счетчик 19, а процесс окончания обменом контролируется ЭВМ и производится по инициативе ЭВМ - источника путем формирования единичного сигнала в девятом разряде регист5 ра 13 команд.

Формула изобретения Устройство для сопряжения ЭВМ с общей магистралью, содержащее дешифратор адреса, блок прерывания, регистр команд, регистр состояний, регистр данных источника, регистр данных приемника, регистр адреса, три триггера, первую группу элементов И, элемент сравнения, элемент развязки, два элемента И, два элемента НЕ, блок захвата магистрали, узлы приемопередатчиков адреса, данных и управляющих сигналов, входы-выходы которых являются входами-выходами устройства для подключения к линиям общей шины ЭВМ, первая группа выходов узла приемопередатчиков управляющих сигналов и группа выходов узла приемопередатчиков адреса соединены соответственно с первой и второй группами входов дешифратора адреса, первый выход которого соединен с входом записи регистра команд, первый выход которого соединен с входом записи регистра адреса и с вторыми входами элементов И первой группы, первые входы которых соединены с группой выходов регистра адреса, старший разряд информационного входа которого соединен с вторым выходом регистра команд, управляющий выход дешифратора адреса соединен с управляющим входом узла приемопередатчиков данных, группа выходов которого соединена с группами информационных входов регистра команд и регистра данных источника, группа выходов которого соединена через линию Данные магистрали обмена с группой информационных входов регистра данных приемника, первой группой информационных входов и группой выходов блока захвата магистрали и первой группой входов элемента сравнения, вторая группа входов которого соединена с группой выходов регистра адреса, группа входов узла приемопередатчиков данных соединена с кодовыми выходами блока прерывания, с выходами регистра данных приемника и с выходами регистра состояния, первый информационный вход которого соединен с первым синхронизирующим входом блока прерывания, с управляющим входом регистра данных источника, с первым входом первого элемента И, с прямым выходом первого триггера и входом элемента развязки, выход которого через линию Признак источника магистрали обмена подключен к входу первого элемента НЕ, выходом соединенного с управляющим входом блока захвата магистрали и с третьими входами элементов И первой группы, выходы которых соединены с второй группой информационных входов блока захвата магистрали, информационный выход и выход строб-сигнала которого соединены соответственно с информационным и синхронизирующим входами первого триггера, второй выход дешифратора адреса соединен с управляющим входом регистра состояния, прямой выход второго триггера - с вторым информационным входом регистра состояния и с первым входом второго элемента И, второй вход которого соединен с

выходом второго элемента НЕ, вход которого соединен с входом сброса второго триггера и подключен через линию Строб-сигнал приемника магистрали обмена к выходу третьего триггера и третьему информационному

0 входу регистра состояния, четвертый информационный вход которого соединен с выходом первого элемента И, третий и четвертый выходы регистра команд - соответственно с первым и вторым входами управления пре5 рыванием блока прерывания, выход запроса и вход подтверждения блока прерывания подключены соответственно к первым информационным входу и выходу узла приемопередатчиков управляющих сигналов,

0 выход ответа блока прерывания соединен с первым дополнительным входом дешифратора адреса, отличающееся тем, что, с целью повышения быстродействия устройства и сокращения времени подключе5 ния абонентов с низким кодом приоритета, в устройство введены четыре элемента И, два элемента И-НЕ, два элемента ИЛИ, элемент ИЛИ-НЕ, вторая группа элементов И, блок прямого доступа в память, дешифратор

0 кода сообщения, счетчик слов, счетчик адреса, счетчик циклов обмена и четвертый триггер, причем вход установки в 1 четвертого триггера соединен с выходом первого элемента И-НЕ, первый вход которого соеди5 нен с выходом элемента сравнения, выход четвертого триггера - с первым входом третьего элемента И, с информационным входом третьего триггера, с первым входом первого элемента ИЛИ, с пятым информа0 ционным входом регистра состояния и с вторым синхронизирующим входом блока прерывания, первый и второй информационные и управляющий входы блока прямого доступа в память соединены соответствен5 но с прямыми выходами первого и четвертого триггеров и пятым выходом регистра команд, шестой выход которого соединен с вторым входом третьего элемента И, выход которого соединен через линию Признак

0 приемника магистрали обмена с вторым входом первого элемента И, седьмой и восьмой выходы регистра команд - с первыми входами элементов И второй группы, вторые входы которых соединены с первым

5 входом второго элемента И-НЕ, с информационным входом второго триггера, с вторым входом первого элемента ИЛИ и с прямым выходом первого триггера, выходы элементов И второй группы соединены соответственно через линии Управление

магистрали обмена с группой входов дешифратора кода сообщения, первый выход которого соединен с вторым входом первого элемента И-НЕ, второй и третий выходы дешифратора кода сообщения - соответст- венно с первыми входами пятого и четвертого элементов И, второй вход пятого элемента И - с выходом первого элемента ИЛИ, третий выход дешифратора кода сообщения - с третьим информационным вхо- дом блока прямого доступа в память, с вторым входом второго элемента И-НЕ и с входом сброса четвертого триггера, второй вход четвертого элемента И соединен через линию Строб-сигнал источника магистра- ли обмена с выходом второго элемента И, выход четвертого элемента И - со счетным входом третьего триггера и с входом записи регистра данных приемника, управляющий вход которого соединен с входом сброса третьего триггера и с выходом элемента ИЛИ-НЕ, первый вход которого соединен с первым выходом блока прямого доступа в память и с вторым дополнительным входом дешифратора адреса, третий и четвертый выходы которого соединены соответственно с первым входом второго элемента ИЛИ и вторым входом элемента ИЛИ-НЕ, второй вход второго элемента ИЛИ соединен с вторым выходом блока прямого доступа в па- мять, выход второго элемента. ИЛИ - с входом записи регистра данных источника и с третьим входом второго элемента И-НЕ, выход которого соединен с входом установки в 1 второго триггера, инверсный выход которого соединен с четвертым информационным входом блока прямого доступа в память, пятый информационный вход которого соединен с выходом третьего триггера, первый вход шестого элемента И - через линию Признак источника общей магистрали - с выходом элемента развязки, второй вход шестого элемента И - с первым выходом регистра команд, выход шестого элемента И - со счетным входом счетчика циклов обмена, группа выходов которого соединена с четвертыми входами элементов И первой группы, пятые входы которых подключены к выходу регистра адреса, вход сброса счетчика циклов обмена соединен с инверсным выходом первого триггера, вход сброса которого соединен с девятым выходом регистра команд, выход переполнения счетчика слов - с четвертым синхронизирующим входом блока прерывания, третий синхронизирующий вход которого соединен с шестым информационным входом блока прямого доступа в память и выходом первого элемента И, шестой информационный вход регистра состояния - с выходом третьего триггера, группа информационных выходов счетчика слов -струйной информационных входов узла приемопередатчиков данных, вход записи счетчика слов - с выходом пятого элемента И, управляющий вход счетчика слов - с пятым выходом дешифратора адреса, шестой выход которого соединен с входом записи счетчика адреса, группа информационных входов которого соединена с группой выходов узла приемопередатчиков данных, группа выходов счетчика адреса.- с группой информационных входов узла приемопередатчиков адреса, вход управления информационных входов узла приемопередатчиков адреса, вход управления которого соединен с третьим выходом блока прямого доступ.а в память, с входом вычитания счетчика слов, со счетным и управляющим входами счетчика адреса, с третьего по г; : гый выходы и входы подтверждения у, отзета блока прямого доступа в память подключены соответственно к второй группе входов и второму и третьему выходам узла приемопередатчиков управляющих сигналов, вторым информационным входом соединенного с седьмым выходом дешифратора адреса, группа информационных входов счетчика слов соединена через линии Данные магистрали обмена с группой выходов регистра данных источника.

ОI и О

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ с общей магистралью | 1987 |

|

SU1434448A1 |

| Устройство для сопряжения магистрали ЭВМ с магистралью внешних устройств | 1984 |

|

SU1246105A1 |

| Устройство для сопряжения двух микроЭВМ с общим внешним устройством | 1985 |

|

SU1345206A1 |

| Устройство для сопряжения ЭВМ с датчиками | 1987 |

|

SU1427375A1 |

| Устройство для сопряжения накопителя на магнитной ленте с вычислительной машиной | 1985 |

|

SU1242971A1 |

| Устройство для сопряжения вычислительной машины с магистралью обмена | 1986 |

|

SU1381519A1 |

| Устройство для сопряжения ЭВМ с синхронными каналами передачи данных | 1986 |

|

SU1347083A1 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| Устройство сопряжения двух магистралей | 1988 |

|

SU1675894A1 |

| Устройство обмена информацией между ЭВМ и абонентами | 1990 |

|

SU1835545A1 |

Изобретение относится к вычислительной технике и может быть использовано в многомашинных или многопроцессорных вычислительных системах с магистральной структурой обмена информацией. Цель изобретения - повышение быстродействия и сокращение времени подключения устройств к магистрали обмена. Цель достигается тем, что в устройство, содержащее дешифратор адреса, блок прерывания, регистр команд, регистр состояний, регистр данных источника, регистр данных приемника, регистр адреса, три триггера, первую группу элементов И, элемент сравнения, элемент развязки, два элемента И, два элемента НЕ, блок захвата магистрали, узлы приемопередатчиков адреса, данных и управляющих сигналов, введены четыре элемента И, два элемента И-НЕ, два элемента ИЛИ, элемент ИЛИ-НЕ, вторая группа элементов И, блок прямого доступа в память, дешифратор кода сообщения, счетчик слов, счетчик адреса, счетчик циклов обмена и четвертый триггер. 6 ил, (Л С

ге

6 Щ

Z.988Zil

/VI

м

i

| Устройство для сопряжения | 1982 |

|

SU1051526A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1987 |

|

SU1434448A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-04-23—Публикация

1990-06-15—Подача