i (Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обращения двух процессоров к общему блоку памяти | 1990 |

|

SU1784986A1 |

| Устройство сопряжения между процессором верхнего уровня и группой процессоров нижнего уровня иерархической мультипроцессорной системы | 1990 |

|

SU1789988A1 |

| Устройство для сопряжения процессора с многоблочной памятью | 1986 |

|

SU1319039A1 |

| Устройство для сопряжения процессора с многоблочной памятью | 1988 |

|

SU1571599A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1405063A2 |

| Устройство для сопряжения | 1978 |

|

SU813400A2 |

| Устройство для сопряжения процессора с памятью | 1983 |

|

SU1149272A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Процессор | 1984 |

|

SU1200294A1 |

| Устройство для сопряжения процессора с многоблочной памятью | 1988 |

|

SU1557568A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении многопроцессорных систем с асинхронным обращением нескольких процессоров к общей памяти. Целью изобретения является повышение надежности за счет обеспечения разделения во времени запросов от двух процессоров к общей памяти. Устройство содержит два дешифратора адреса, два дешифратора сегмента, два регистра номера массива, два коммутатора, четыре приемопередатчика, шифратор, узел синхронизации, четыре триггера, шесть элементов И, два элемента И-НЕ, четыре элемента НЕ, элемент ИЛИ. 4 ил.

Изобретение относится к вычислительной технике и может быть использовано при построении многопроцессорных систем с асинхронным обращением нескольких процессоров к общей памяти.

Цель изобретения - повышение надежности за счет обеспечения разделения во времени запросов от двух процессоров к общей памяти.

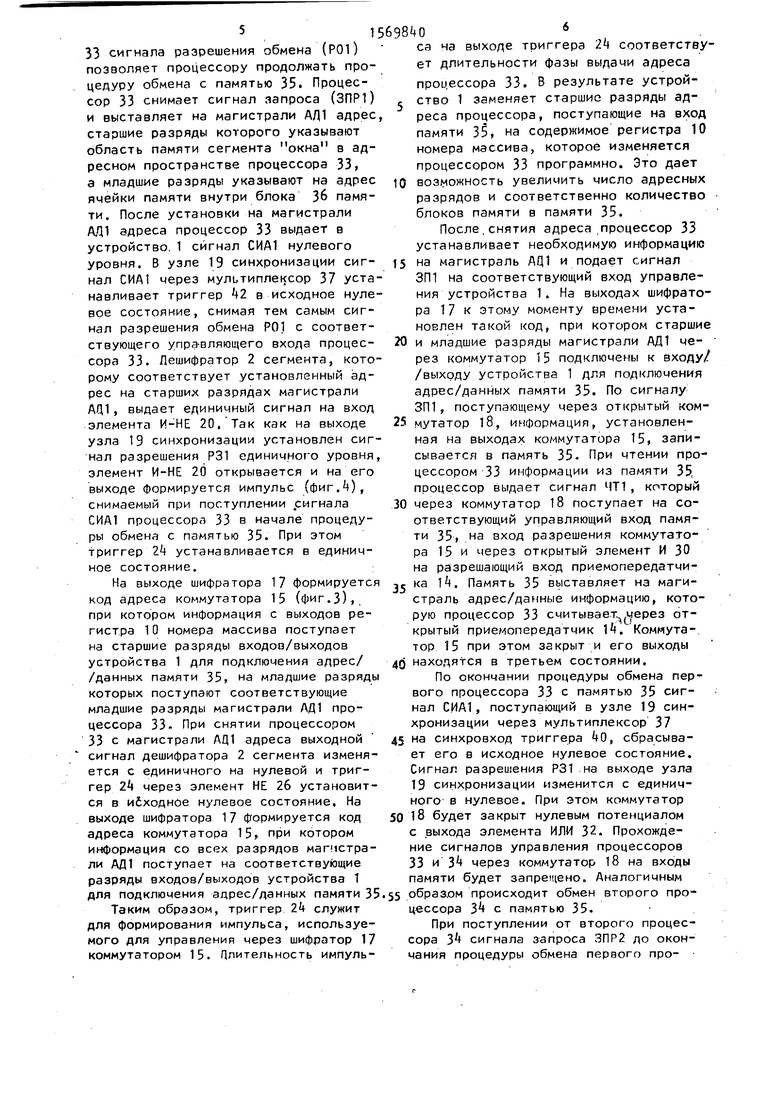

На фиг. 1 приведена структурная схема устройства; на фиг. 2 - узел синхронизации; на фиг. 3 - схема первого коммутатора и шифратора; на фиг. Ц - временная диаграмма работы устройства совместно с процессорами. Устройство 1 содержит (фиг.1) дешифраторы, 2 и 3 сегмента, дешифраторы U и 5 адреса, триггеры 6 и 7, элементы И 8 P. 9t регистры 10 и 11 номера массива, приемопередатчики 12-И,

коммутатор 15, приемопередатчик И, шифратор 17, коммутатор 18, узел 19 синхронизации, элементы И-НЕ 20 и 21, элементы И 22 и 23, триггеры и 25, элементы НЕ 26-29, элементы И 30 и 31, элемент ИЛИ 32. Кроме того, на фиг. 1 обозначены процессоры 33 и 3 и общая память 35, состоящая из ряда блоков 36 памяти.

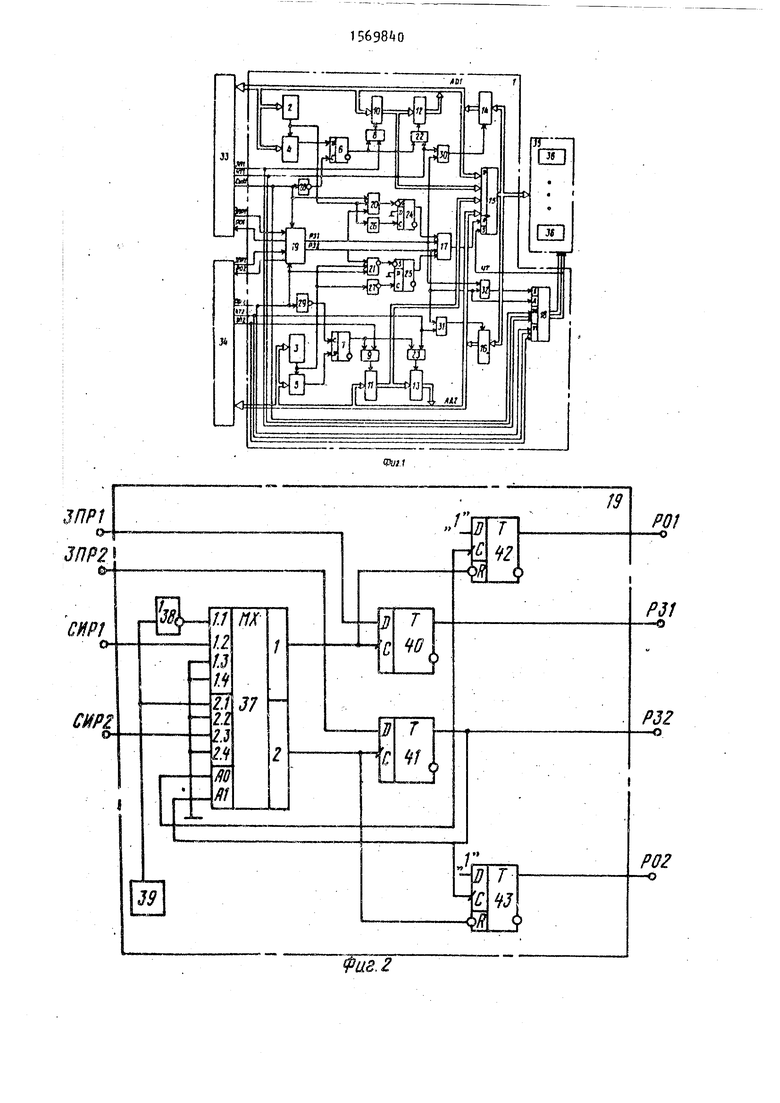

Узел 19 синхронизации содержит (фиг.2) мультиплексор 37, элемент НЕ 38, генератор 39 импульсов, триггеры 0-1+3.

Коммутатор 15 (фиг.З) состоит из мультиплексоров М и 5, которые имеют три состояния выхода.

Шифратор 17 содержит (фиг.З) элементы И 6 и ИЛИ kl.

В области адресного пространства каждого из процессоров выделяется зона (окно), при обращении к котоел

о со

00

рой он имеет доступ к многоблочной памяти 35. Все адресные пространства памяти 35 разбито на сегменты, размер которых соответствует размеру адресного пространства окна (размер окна в каждом конкретном случае может быть различным). Каждому сегменту соответствуют равные по объему блоки 36 памяти входы/пыходы которых за- параллелены и образуют входы/выходы многоблочной памяти 35. Номер блока 36 памяти, к которому осуществляется обращение, фиксируется соответственно в регистрах 10 и 11 номера массива .

В исходном состоянии триггеры и 25 устройства 1, а также триггеры 40 и И узла 19 синхронизации находятся в нулевом состоянии. При этом на адресных входах мультиплексора 37 установлен код 00, разрешая тем самым прохождение прямой и ипперсной частоты генератора 39 на установочные входы триггеров 42 и 3. Таким образом, триггеры 2 и U3 находятся также о нулевом состоянии. Приемопередатчики и 16 закрыты и их выходы находятся в третьем состоянии. Так как триггеры 40 и 1 узла 19 синхронизации находятся в нулевом состоянии, нулевме уровни на ее выходах разрешения (Р31, Р32) через элемент ИЛИ 32 запрещают прохождение сигналов управления процессоров 33 и 3 иерез коммутатор 18 в память 35.

Перед началом обмена процессоров с памятью каждому из процессоров необходимо установить в соответствующем регистре 10(11) номера массива номер требуемого блока 36 памяти. Для этого процессор, например процессор 33, выставляет на магистраль адрес/данные (АЦ1) адрес регистра 10 номера массива. Дешифратор 4 адреса дешифрирует адрес, установленный на его входах, и выдает на выходе единичный сигнал. После этого процессор выдает сигнал Синхронизация адреса (СИА1), который через элемент НЕ 28 устанавливает триггер 6 в единичное состояние. Затем процессор 33 снимае с магистрали AfJ1 адрес и устанавливает на ней данные, которые фиксируются в регистре 10 номера массива при поступлении на его вход записи через открытый элемент И 8 управляющего сигнала Запись (ЗП1) процессора 33 Если в устройство поступает управпя

0

5

0

5

30

35

40

45

50

55

ющий сигнал процессора 33 Чтение (ЧТ1), единичный сигнал с выхода элемента И 22 поступает на разрешающий вход приемопередатчика 12, разрешая тем самым прохождение информации, записанной в регистре 10 номера массива, на магистраль АД1 процессора 33.

При снятии процессором 33 с магистрали АД1 адреса на выходе дешифратора 4 устанавливается нулевой потенциал, поэтому в следующем цикле работы процессора 33 с магистралью АД1 сигнал СИА1 через элемент НЕ 28 устанавливает триггер 6 в нулевое состояние.

Аналогичным образом осуществляется обращение второго процессора 3 к регистру 11 номера массива. При этом доступ процессоров к регистрам номера массива возможен в произвольные моменты времени независимо друг от друга. После установки номеров блокоп памяти на регистрах 11 и 12 номера массива устройства 1 процессоры 33 и 3 могут обратиться к любой из ячеек, заданных блоков 36 памяти .

Обращение процессоров к ячейкам памяти 35 осуществляется следующим образом. При поступлении сигнала запроса (ЗПР) на обмен с памятью, например, от первого процессора 33 импульс частоты с первого выхода мультиплексора 37 в узле 19 синхронизации устанавливает триггер 40 в единичное состояние. Установкой единичного потенциала на выходе Р31 узла 19 синхронизации устройство 1 обеспечивает монопольное использование памяти 35 первым процессором 33 При этом на вход разрешения коммутатора 18 с выхода элемента ИЛИ 32 поступает единичный потенциал, а на его адресный вход - нулевой потенциал с выхода Р32 узла 19 синхронизации. Коммутатор 18 разрешает прохождение сигналов управления первого процессора 33 в память 35. При изменении потенциала выхода триггера 0 с нулевого на единичный, триггер k2 устанавливается в единичное состояние, а на адресных входах мультиплексора 37 устанавливается код 01. Тем .самым разрешается прохождение сигнала синхронизации адреса СИА1 на синхровход триггера , а на синхровход триггера 1 1 - нулевого уровня с шины Земля, Появление на входе процессора

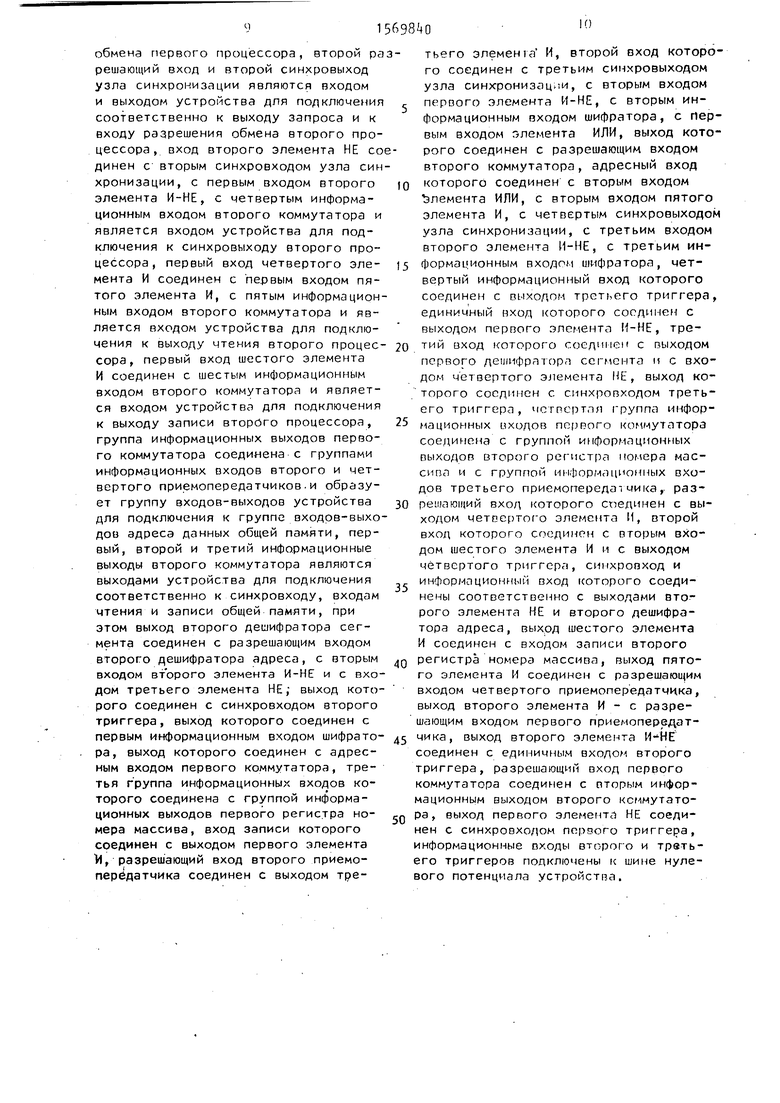

33 сигнала разрешения обмена (Р01) позволяет процессору продолжать процедуру обмена с памятью 35. Процессор 33 снимает сигнал запроса (ЗПР1) и выставляет на магистрали АД1 адрес, старшие разряды которого указывают область памяти сегмента окна в адресном пространстве процессора 33, а младшие разряды указывают на адрес ячейки памяти внутри блока 36 памяти. После установки на магистрали АД1 адреса процессор 33 выдает в устройство 1 сигнал СИА1 нулевого уровня. В узле 19 синхронизации сигнал СИА1 через мультиплексор 37 устанавливает триггер 42 в исходное нулевое состояние, снимая тем самым сигнал разрешения обмена Р01 с соответствующего управляющего входа процессора 33. Дешифратор 2 сегмента, которому соответствует установленный адрес на старших разрядах магистрали АД1, выдает единичный сигнал на вход элемента И-НГ. 20. Так как на выходе узла 19 синхронизации установлен сигнал разрешения Р31 единичного уровня, элемент И-НЕ 20 открывается и на его выходе формируется импульс (фиг.4), снимаемый при поступлении сигнала СИА1 процессора 33 я начале процедуры обмена с памятью 35. При этом триггер устанавливается в единичное состояние.

На выходе шифратора 17 формируется код адреса коммутатора 15 (фиг.З), при котором информация с выходов регистра 10 номера массива поступает на старшие разряды входов/выходов устройства 1 для подключения адрес/ /данных памяти 35, на младшие разряды которых поступают соответствующие младшие разряды магистрали АД1 процессора 33. При снятии процессором 33 с магистрали ЛЦ1 адреса выходной сигнал дешифратора 2 сегмента изменяется с единичного на нулевой и триггер через элемент НЕ 26 установится в ибходное нулевое состояние. На выходе шифратора 17 формируется код адреса коммутатора 15, при котором информация со всех разрядов магистрали АД1 поступает на соответствующие разряды входов/выходов устройства 1

10

15

20

25

са на выходе триггера соответств ет длительности фазы выдачи адреса процессора 33. В результате устройство 1 заменяет старшие разряды адреса процессора, поступающие на вхо памяти 35, на содержимое регистра 1 номера массива, которое изменяется процессором 33 программно. Это дает возможность увеличить число адресны разрядов и соответственно количеств блоков памяти в памяти 35.

После снятия адреса процессор 33 устанавливает необходимую информацию на магистраль АД1 и подает сигнал ЗП1 на соответствующий вход управле ния устройства 1. На выходах шифрато ра 1 7 к этому моменту времени установлен такой код, при котором старши и младшие разряды магистрали АД1 через коммутатор 15 подключены к входу /выходу устройства 1 для подключения адрес/данных памяти 35. По сигналу ЗП1, поступающему через открытый ком мутатор 18, информация, установленная на выходах коммутатора 15, записывается в память 35. При чтении про цессором 33 информации из памяти 35 процессор выдает сигнал ЧТ1, который 30 через коммутатор 18 поступает на соответствующий управляющий вход памяти 35, на вход разрешения коммутатора 15 и через открытый элемент И 30 на разрешающий вход приемопередатчика И. Память 35 выставляет нэ магистраль адрес/данные информацию, которую процессор 33 считывает- через открытый приемопередатчик . Коммутатор 15 при этом закрыт и его выходы 40 находятся в третьем состоянии.

По окончании процедуры обмена первого процессора 33 с памятью 35 сигнал СИА1, поступающий в узле 19 синхронизации через мультиплексор 37 45 на синхровход триггера 40, сбрасывает его в исходное нулевое состояние. Сигнал разрешения Р31 на выходе узла 19 синхронизации изменится с единичного в нулевое. При этом коммутатор 50 18 будет закрыт нулевым потенциалом с выхода элемента ИЛИ 32. Прохождение сигналов управления процессоров 33 и 3 через коммутатор 18 на входы

35

памяти будет запрещено. Аналогичным для подключения адрес/данных памяти 35.55 образом происходит обмен второго проТаким образом, триггер служит цессора 3 с памятью 35. для формирования импульса, испольэуе- При поступлении от второго процес- мого для управления через шифратор 17 сора 3 сигнала запроса ЗПР2 до окон- коммутатором 15. Длительность импуль- чания процедуры обмена первого про

, ,

10

15

20

25

са на выходе триггера соответствует длительности фазы выдачи адреса процессора 33. В результате устройство 1 заменяет старшие разряды адреса процессора, поступающие на вход памяти 35, на содержимое регистра 10 номера массива, которое изменяется процессором 33 программно. Это дает возможность увеличить число адресных разрядов и соответственно количество блоков памяти в памяти 35.

После снятия адреса процессор 33 устанавливает необходимую информацию на магистраль АД1 и подает сигнал ЗП1 на соответствующий вход управления устройства 1. На выходах шифратора 1 7 к этому моменту времени установлен такой код, при котором старшие и младшие разряды магистрали АД1 через коммутатор 15 подключены к входу/ /выходу устройства 1 для подключения адрес/данных памяти 35. По сигналу ЗП1, поступающему через открытый коммутатор 18, информация, установленная на выходах коммутатора 15, записывается в память 35. При чтении процессором 33 информации из памяти 35 процессор выдает сигнал ЧТ1, который 30 через коммутатор 18 поступает на соответствующий управляющий вход памяти 35, на вход разрешения коммутатора 15 и через открытый элемент И 30 на разрешающий вход приемопередатчика И. Память 35 выставляет нэ магистраль адрес/данные информацию, которую процессор 33 считывает- через открытый приемопередатчик . Коммутатор 15 при этом закрыт и его выходы 40 находятся в третьем состоянии.

По окончании процедуры обмена первого процессора 33 с памятью 35 сигнал СИА1, поступающий в узле 19 синхронизации через мультиплексор 37 45 на синхровход триггера 40, сбрасывает его в исходное нулевое состояние. Сигнал разрешения Р31 на выходе узла 19 синхронизации изменится с единичного в нулевое. При этом коммутатор 50 18 будет закрыт нулевым потенциалом с выхода элемента ИЛИ 32. Прохождение сигналов управления процессоров 33 и 3 через коммутатор 18 на входы

35

715

цессора 33 с памятью 35 сигнал разрешения Р32 на выходе узла 19 синхронизации не будет сформирован и дальнейшая- работа процессора 3 будет приостановлена. После возврата триггера 40 (фиг. 2) в исходное нулевое состояние первый импульс частоты генератора импульсов 39, скоммутирован- ный мультиплексоромЗ на синхровход триггера М, перебросит его в единичное состояние, разрешая процессору доступ к памяти 35. При получении процессором 3 сигнала разрешения об- .мена Р02 он начинает аналогично первому процессору выполнять процедуру обмена с памятью 35.

Так как генератор импульсов 39 в узле 19 синхронизации подключен к первому входу первой группы входов мультиплексора 37 через элемент НЕ 38, импульсы частоты поступают на синхровходы триггеров «0 и 1 со сдвигом на полпериода. Это позволяет исключить возможность одновременного подключения процессооов 33 и 3 к общей памяти 35. При совпадении во времени запросов ЗПР1 , ЗПР2 двух процессоров устройство 1 сопряжения обеспечивает их последовательное обращение к памяти 35 на время одного цикла записи или чтения. Таким образом, асинхронно поступающие от первого 33 и второго 3 процессоров запросы на обращение к памяти будут обслуживаться последовательно, по очередности поступления без назначения приоритета одному из процессоров.

Формула изобретения

Устройство для сопряжения двух процессоров с общей памятью, содержащее четыре приемопередатчика, первый дешифратор сегмента, первый дешифратор адреса, первый коммутатор, первый триггер, два элемента И, первый регистр номера массива, причем группа информационных входов первого дешифратора сегмента соединена с группой информационных входов первого дешифратора адреса, с группой информационных входов первого регистра номера массива, с первой группой информационных входов первого коммутатора,-с группами информационных выходов первого и второго приемопередатчиков и образует группу входов-выходов устройства для подключения к группе вхоR

О

5

0

25

30

35

40

45

SO

55

дов-выхоцов адреса данных первого процессора, при этом выход первого дешифратора сегмента соединен с разрешающим входом первого дешифратора адреса , выход которого соединен с информационным входом первого триггера, выход которого соединен с первыми входами первого и второго элементов И, группа информационных выходов первого регистра номера массива соединена с группой информационных входов первого приемопередатчика, отличающееся тем, что, с целью повышения надежности за счет обеспечения разделения во времени запросов от двух процессоров к общей памяти,в устройство введены узел синхронизации, шифратор, второй коммутатор, второй дешифратор сегмента, второй дешифратор адреса, второй регистр номера массива, три триггера, четыре элемента И, два элемента И-НЕ, элемент ИЛИ, четыре элемента НЕ, причем группа информационных входов второго дешифратора сегмента соединена с группой информационных входов второго дешифратора адреса, с группой информационных входов второго регистра номера массива, с второй группой информационных входов первого коммутатора, с группами информационных выходов третьего и четвертого приемопередатчиков и образует группу входов-выходов устройства для подключения к группе входов-выходов адреса данных второго процессора, второй вход первого элемента И соединен с первым информационным входом второго коммутатора и является входом устройства для подключения к выходу записи первого процессора, второй вход второго элемента И соединен с первым входом третьего элемента И, с вторым информационным входом второго коммутатора и является входом устройства для подключения к выходу чтения первого процессора, вход первого элемента НЕ соединен с первым входом первого элемента И-НЕ, с первым синхровходом узла синхронизации, с третьим информационным входом второго коммутатора и является входом устройства для подключения к синхровыходу первого про- .цессора, первый разрешающий вход и первый синхровыход узла синхронизации являются входом и выходом устройства для подключения соответственно к выходу запроса и к входу разрешения

1115 Wo

бмена первого процессора, второй разтг у п фо вы ро вт ко Ъл эл уз вт фо ве со ед вы ти пе до то ег ма со пы си до ре хо вх до че ин не ро то И ре го вхо вых шаю чик сое три ком мац ра, нен инф его вог

решающий вход и второй синхровыход узла синхронизации являются входом и выходом устройства для подключения соответственно к выходу запроса и к входу разрешения обмена второго процессора, вход второго элемента НЕ содинен с вторым синхровходом узла синхронизации, с первым входом второго элемента И-НЕ, с четвертым информационным входом второго коммутатора и является входом устройства для подключения к синхровыходу второго процессора, первый вход четвертого элемента И соединен с первым входом пятого элемента И, с пятым информационным входом второго коммутатора и является входом устройства для подключения к выходу чтения второго процессора, первый вход шестого элемента И соединен с шестом информационным входом второго коммутатора и является входом устройства для подключения к выходу записи второго процессора, группа информационных выходов первого коммутатора соединена с группами информационных входов второго и четвертого приемопередатчиков и образует группу входов-выходов устройства для подключения к группе входов-выхо доо адреса данных общей памяти, первый, второй и третий информационные выходы второго коммутатора являются выходами устройства для подключения соответственно к синхровходу, входам чтения и записи общей памяти, при этом выход второго дешифратора сегмента соединен с разрешающим входом второго дешифратора адреса, с вторым входом вт орого элемента И-НЕ и с входом третьего элемента НЕ, выход которого соединен с синхровходом второго триггера, выход которого соединен с первым информационным входом шифрато- ра, выход которого соединен с адресным входом первого коммутатора, третья группа информационных входов которого соединена с группой информационных выходов первого регистра номера массива, вход записи которого соединен с выходом первого элемента V), разрешающий вход второго приемопередатчика соединен с выходом тре

Ш

10

15

20

25

30

35

0

0

тьто элемент И, второй сход которого соединен с третьим симхровыходом узла синхронизации, с вторым входом первого элемента И-НЕ, с вторым информационным входом шифратора, с первым входом элемента ИЛИ, выход которого соединен с разрешающим входом второго коммутатора, адресный вход которого соединен с вторым входом Ълрмента ИЛИ, с вторым входом пятого элемента И, с четвертым синхровыходом узла синхронизации, с третьим входом второго элемента И-НЕ, с третьим информационным входгм шифратора, четвертый информационный вход которого соединен с выходом третьего триггера, единичный нход которого соединен с выходом первого элемента И-НЕ, третий оход которого госдпигн с пыходом первого дешифратора се1мсмтл и с входом четвертого элемента HL, выход которого соединен с сннхропходом третьего триггера, чотертая группа информационных Е ХОДОВ пс-ррпго коммутатора соединена с группой информационных пыходоп второго регистра номера мас- сиил и с группой информационных входов третьего пригмогтерсда-, чика , разрешающий вход которого спединен с выходом четрертого элемента И, второй вход которого соединен с вторым входом шестого элемента И и с выходом четвертого триггера, симхрогзход и информационный вход которого соединены соответственно с выходами второго элемента НЕ и второго дешифратора адреса, выход шестого элемента И соединен с входом записи второго регистра номера массива, выход пятого элемента И соединен с разрешающим входом четвертого приемопередатчика, выход второго элемента И - с разрешающим входом первого приемопередатчика, выход второго элемента И-НЕ соединен с единичным входом, второго триггера, разрешающий вход первого коммутатора соединен с вторым информационным выходом второго коммутатора, выход первого элемента НЕ соединен с синхровходом первого триггера, информационные входы второ( о и третьего триггеров подключены к шине нулевого потенциала устройства.

52

cvj г Г - j -c- irs

14

fl

Oj

NO

-u:

№

-ч

N.

i

C-4

«

-t- Ca NQ

53

§

V a

§

О

vo оэ

Ј- О

§ юД

йСч4

Nj

0$

| Устройство управления обращением к памяти | 1984 |

|

SU1171801A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-06-07—Публикация

1988-08-15—Подача