Изобретение относится к области вычислительной техники и предназначено для построения специализированных вычислительных устройств, решаютих системы линейных алгебраических и дифференциальных уравнений. Известно устройство для решения систем линейных алгебраических уравнений, содержащее .сдвиговые регистры одноразрядные сумматоры-вычитатели, объединенные в п столбцов по п после довательно соединенных сумматоров-вы читателей в каждом,причем выходы соответствующих сдвиговых регистров соединены с входами одноразрядных сумматоров-вычитателей, а управляющи входы соединены с управляющей шиной. Управлякицие входы одноразрядных сумматоров-вычитателей соединены с входами соответствующих реверсивных счетчиков. Сумма приращений неизвест ных, умноженных на соответствующие коэффициенты, накапливается в реверсивных счетчиках, начальное значение которых устанавливается равным нулю l. Недостатком этого устройства ялвяется то, что устройство работает с приращениями неизвестного, в этом случае число итераций, необходимое для определения точного решения системы линейных алгебраических уравнений, может быть велико, что увеличивает время решения поставленной задачи. Наиболее близким техническим решением к предлагаемому является устройство для решения систем линейных алгебраических уравнений, содержащее одноразрядные сумматоры-вычитатели и сдвиговые регистры, управляющие входы которых соединены с управляющей шиной, а выходы с первыми входами соответствующих одноразрядных сумматоров-вычитателей, которые объединены в п столбцов по (п+1) последовательно соединенных одноразрядных сумматоров-вычитателей в каждом, управляющие зходы одноразрядных сумматоров-вычитателей каждой строки соединены с входами соответствующих реверсивных счетчиков 2. Недостатком этого устройства является то, что устройстро не дае.:т возможности решать системы линейных дифференциальных уравнений) накладываются ограничения на вид линейных алгебраических уравнений (знак компоненты вектора решения должен совпадать со знаком соответствующей компоненты вектора свободных членов).

Целью изобретения является расширение класса решаемых задач.

Поставленная цель достигается тем, что в устройство, содержащее суммато эы-вычитатели и сдвиговые регистры, управляющие входы которых соединены с управляющим входом устройства, а выходы - подключены к первым входам соответствуквдих сумматоров-вычитателей, объединенных в п столбцов по (п+1) последовательно соединенных сумматоров-вычитателей в каждом, в каждый столбец введены регистр частичных сумм, регистр результата, блок фиксации окончания решения, блок сравнения, (п+2)-й и (п+3)-й суммаTopui-вычитатели, элемент 2И-ИЛИ,причем выход (п+1)-го сумматора-вычитателя каждого столбцу соединен с первым входом соответствующего элемента 2И-ИЛИ, выход которого соединен с первым входом (п+2)-го сумматора-вычитателя своего столбца, выход которого соединен с входом соответствующего регистра результата, выход младшего разряда которого соединен со вторым входом соответствующего (п+2)го сумматора-вычитателя, с входом блока сравнения и с первым входом (п+3)-гр сумматора-вычитателя своего столбца, второй вход которого соединен с выходом (п+2)-го сумматоравычитателя, а выход - с входом соответствующего блока фиксации окончания решения, выход младшего разряда регистра частичных сумм соединен со вторЕлм входом первого сумматора-вычитателя соответствующего столбца, второй вход элемента 2И-ИЛИ подключен к выходу п-го сумматора-вычитателя соответствующего столбца,третий вход элемента 2И-ИЛИ, -управляющие .входы (п+2 ) -го и (п+3) -го сумматоров-вычитателей, регистра результата, регистра частичных сумм, блока фиксации окончания решения и его выход соединены с управляющим входом устройства, управляющие сумматоров-вычитателей первых И строк соединены с выходами соответствующих блоков сравнения.

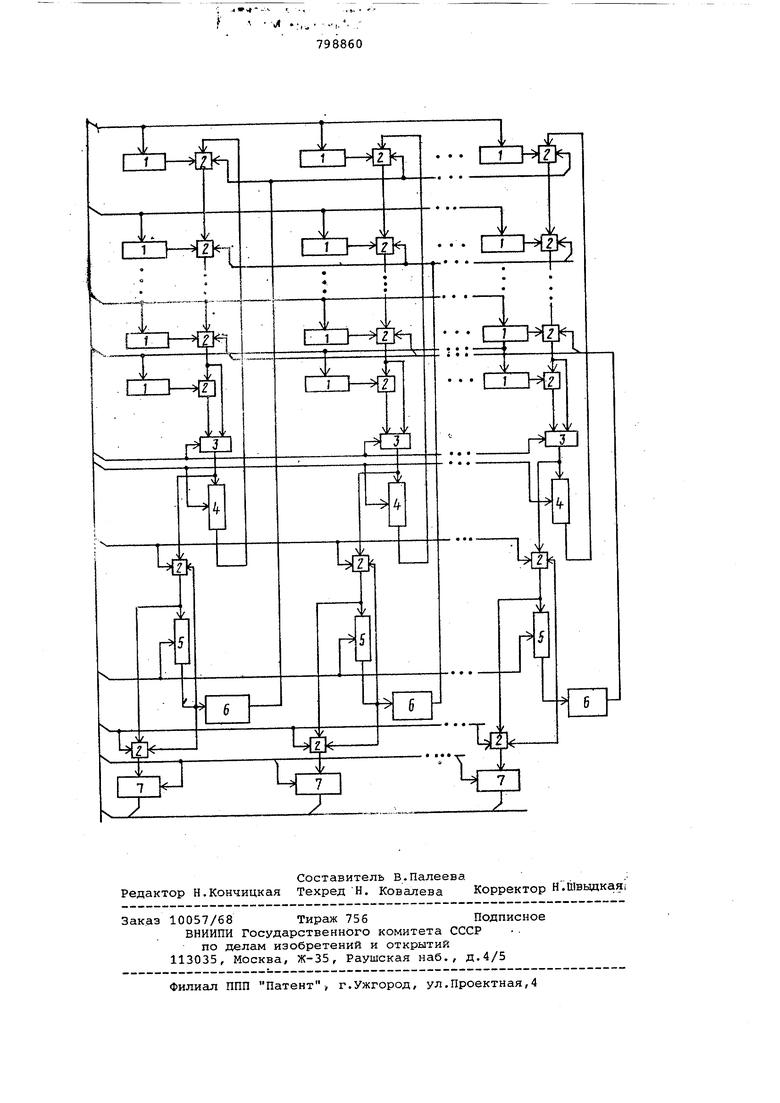

На чертеже изображена блок-схема устройства. Устройство состоит из сдвиговых регистров 1, сумматороввычитателей 2, элементов 2И-ИЛИ 3, регистров 4 частичных сумм, регистров 5 результата, блоков б сравнения, блоков 7 фиксации окончания решения.

БЛОК 4 сравнения предназначен для управлениярежимом работы соответствующей строки одноразрядных сумматоров-вычитателей 2 во время вьтолнения умножения на текущую р-ю цифру регистра результата.

Блок 7 фиксации окончания решения предназначен для анализа модуля разности между значениями переменных на р-ой и (р-1)-ой :итерацииг и выработки сигнала на окончание решения

системы линейных адгебраических уравнений.

Работа устройства при решении систем линейных -дифференциальных уравнений следующая. Коды коэффициентов.

,j при соответствующих переменных системы линейных дифференциальных уравнений заносятся в сдвиговые регистры 1. В (п +1) -ые сдвиговые регистры 1 заносятся соответствующие коды свободных членой Ь:- Регистры 4 частичных сумм обнуляются, в регистры 5 результата заносятся соответствующие коды начальных условий переменных. В блоке б в результате анализа младшей цифры регистра 5 результата вырабатывается и запоминается управляющее воздействие, определяющее режим работы одноразрядных сумматоров-вычитателей 2, которое поступает на управляющие входы одноразрядных сумматоров-вычитателей 2 соответствующей строки. Код из регистра 4 частичных сумм, начиная с младших разрядов, поступает на второй вход первого одноразрядного сумматора-вычитателя 2. Этот код, просуммировавшись с соответствующими коэффициентами, поступившими со сдвиговых регистров 1, через второй элемент И элемента 2И-ИЛИ 3 записывается в регистр 4 частичных сумм. Содержимое сдвиговых регистров 1, в процессе суммирования, начиная с младших разрядов, подается на соответствующие одноразрядные сумматоры-вычитатели 2 и перезаписывается в сдвиговые регистры 1. После окончания суммирования содержимое регистров 5 результата сдвигается на 1 разряд в сторону младших разрядов и перезаписывает младший разряд в знаковый разряд соответствующего регистра 5 результата. При умножении коэффициентов на знаковый разряд регистра 5 результата из (п+1)-го сдвигового регистра 1 к полученному произведению прибавляется код свободного члена Ъ и через первый элемент И элемента 2И-ИЛИ 3 подается на первый вход (п+2)-го одноразрядного сумматоравычихателя 2, на второй вход которого с задержкой, определяемой величиной шага .итерации . подается код регистра 5 результата, начиная с младших разрядов, а с выхода {п+2)го одноразрядного сумматора-вы:читателя 2 записывается в соответствующий регистр. 5 результата. После каждой итерацииI регистры частичных сумм 4 -Обнуляются. При решении систем линейных алгебраических уравнений в последнем умножении код из регистра 5 результата, начиная с младших разрядов, поступает на первый вход (п+3)-гр одноразрадного сумматоравычитателя 2, который работает в режиме вычитания, на второй вход которого поступает код нового значе;ния переменной с выхода (п+2)-го одноразрядного сумматора-вычитателя 2 Выход (п+3)-го одноразрядного сум-матора-вычитателя 2 соединен с блока 7 фиксации окончания решения. При определении момента.установившегося значения переменных процесс решения прекращается. Устройство отличается повышенными функциональными возможностями, связанными с тем, что на одном и том же оборудовании можно решать как системы линейных алгебраических, так и дифференциальных уравнений. Кроме того, по сравнению с известным расши ряется класс алгебраических уравнени решение которых возможно. Устройство позволяет решать систе мы линейных алгебраических уравнений с положительно определенной матрицей Формула изобретения Устройство для решения систем линейных алгебраических и дифференциал ных уравнений, содержащее сумматорывычитатели и сдвиговые регистры,, управляющие входы которых соединены с управляющим входом устройства, а выходы - подключены к первым входам соответствующих сумматоров-вычитате лей, объединенных в п столбцов по (п+1) последовательно соединенных сумматоров-вычйтателей в каждом, отличающееся тем, что, с целью расширения класса решаемых задач, в каждый столбец введены регистр частичных сумм, регистр результата, блок фиксации окончания решения, блок сравнения, (п+2)-й и (п+3)-й сумматоры-вычитатели/ элемент 2И-ИЛИ, причем выход (п+1)-го сумматора-вычитателя каждого столбца соединен с первым входом соответствующего элемента 2И-ИЛИ, выход которого соединен с первым входом (п+2)го сумматора-вычитателя своего столбца, выход которого соединен с входом соответствующего регистра результата, выход младшего разряда которого соединен со вторым входом соответствующего (п+2)-го сумматора-вычитателя, с входом блока сравнения и с первым входом (п+3)-го сумматора-вычитателя своего столбца, второй вход которого соединен с выходом {п+2)-го сумматора-вычитателя, а выход - с входом соответствующего блока фиксации окончания решения, выход младшего разряда-регистра частичных сумм соединё-н со вторым входом первого сумматора-вычитателя соответствующего столбца, второй вход элемента 2И-ИЛИ подключен к выходу п-го сумматора-вычитателя соответствующего столбца, третий вход элемента 2И-ИЛИ управляющие входы (п+2)-го и (п+3)го сумматоров-вычйтателей, регистра результата, регистра частичных сумм, блока фиксации окончания решения и его выход соединены с управляющим входом устройства, управляющие входы сумматоров-вычйтателей первых п строк соединены с выходами соответствующих блоков сравнения. Источники информации, принятые во внимание при экспертизе 1.Майоров Ф.В. Электронные цифровые интегрирующие машины, Машиностроение, М., 1962, с.86, фиг.59. 2.Авторское свидетельство СССР № 543943, кл.С 06 F 15/32, 1977 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для решения систем ли-НЕйНыХ АлгЕбРАичЕСКиХ уРАВНЕНий | 1978 |

|

SU811275A1 |

| Устройство для решения систем линейных алгебраических уравнений | 1975 |

|

SU543943A1 |

| Устройство для решения систем ли-НЕйНыХ АлгЕбРАичЕСКиХ уРАВНЕНий | 1978 |

|

SU811274A1 |

| Устройство для решения системлиНЕйНыХ уРАВНЕНий | 1978 |

|

SU798862A1 |

| Многоканальное устройство дляРЕшЕНия СиСТЕМ лиНЕйНыХ АлгЕбРАичЕС-КиХ уРАВНЕНий | 1978 |

|

SU807318A1 |

| Устройство для решения систем линейных алгебраических уравнений | 1980 |

|

SU940167A1 |

| Устройство для решения системлиНЕйНыХ АлгЕбРАичЕСКиХ уРАВНЕНий | 1978 |

|

SU805336A1 |

| Преобразователь кодов | 1973 |

|

SU526884A1 |

| МАТРИЧНЫЙ СПЕЦПРОЦЕССОР | 1994 |

|

RU2079879C1 |

| Узловой элемент цифровой сетки для решения краевых задач | 1984 |

|

SU1246111A1 |

Авторы

Даты

1981-01-23—Публикация

1978-05-03—Подача