(54) ПРЕОБРАЗОВАТЕЛЬ КОДОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для алгебраического сложения чисел | 1983 |

|

SU1136148A1 |

| Универсальное суммирующее устройство | 1990 |

|

SU1786484A1 |

| Преобразователь правильной двоичной дроби в двоично-десятичную дробь и целых двоично-десятичных чисел в двоичные | 1978 |

|

SU734669A1 |

| Устройство для решения систем ли-НЕйНыХ АлгЕбРАичЕСКиХ уРАВНЕНий | 1978 |

|

SU811275A1 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР-ВЫЧИТАТЕЛЬ НА НЕЙРОНАХ СО СКВОЗНЫМ ПЕРЕНОСОМ | 2012 |

|

RU2523942C2 |

| АРИФМЕТИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2004 |

|

RU2292580C2 |

| Преобразователь двоичного кода в р-ичный позиционный код | 1983 |

|

SU1163479A1 |

| ДЕЛИТЕЛЬ НА НЕЙРОНАХ | 2003 |

|

RU2249846C1 |

| Устройство для определения фазы спектральных составляющих | 1985 |

|

SU1247890A2 |

| Устройство для решения системлиНЕйНыХ АлгЕбРАичЕСКиХ и диф-фЕРЕНциАльНыХ уРАВНЕНий | 1978 |

|

SU798860A1 |

Изобретение относится к области вычислительной техники и автоматики и предназначено для преобразования кодов в -коды с другим ocHOBainieM системы счисления.

Известны устройства для лреобразозания кодов чисел из системы счисления с од:-п М основанием в систему счисления с другим основанием.

Одно из нзаестны.х устройств содержит счетчллм, работающие в требуемых системах счисления, олсх управления и ряд логических элементов.

Одна,ко этот преобразователь имеет низкое быстродействие.

Другое известное усрройство обладает высо.ким быстродействием, однако требует значительных аппаратурных затрат и ограниченные функциональные возможности.

Наиболее близким техническим решением к данному изобретению является преобразователь кодо.в, содержанл,ий элемепты И, регистр преобразуемого числа, выходы ixoroporo соединены с информационными входами первого блока элементов И, управляющий вход которого соединен с первьгм выходом блока упра1вления, второй выход которого соединен с первым сдвиговым входом регистра преобразуемого числа, выходы двух старших разрядов которого соединены с информационнымн входалп блока алгебраического суммнрова}1ия.

Недостатком нзвестного преобразователя является то. что с его П0:мощью возможе} перевод чисел только из системы с меньшим основавием в систему с большим основанием.

Целью изоб.ретелия является расширение класса решаемых задач, а именно (Выполненне перевода кодоз целых чисел с одним произвольным основанием в ,КОЛЫ с любым другим основанием.

Поставленпая цель достигается тем, что в преобразователь введены второй и третий блоки элементов И, регистр результата, многоразрядный .вычитатель, одноразрядный н одноразрядный вычитатель, при этом перВая группа входов многоразрядного вьпп тателя соедннена с выходамп регистра результата и входа мн второго блока элементов II, а выходы нодключены к информациоиным входам третьего блока элементов И, выходы которого соеднне1ны с первой группой входов регистра результата, вторая группа входов которого соединена с выходами первого блока элементов И, вход старшего разряда регистра результата соединен с выходом его младшего разряда, а сдвиговый вход соединен со вторым СДВИГОВЫЕ входом регистра преобразуемого числа и третьим выходом блока управления, первый и четвертый выход .которого coezuiHeiHbi с управляющим входом пторого и третьего элементов И соответственно, пятый и ш.естой выходы блока управления подключены к управляющим входам блока алгебраичеакого суммирования, первый и второй выходы которого подключены к.первым входам соответственно первото и второго элсментов И, вторые входы которых соединены с седьмым выходом блока управления, (восьмой выход .Которого соединен с первыми входами третьего и четвертого элементов И, вторые входы которых соединены соответственно с выходЯМИ одноразрядного сумматора и одноразрядного вычитателя, девятый выход блока управления соединен с входом младшего разряда регистра результата, выход младщего разряда регистра .преобразуемого числа соединен с входа;мн блока управления и одноразрядного вычитателя, выход последующего разряда регистра преобразуемого числа соединен с входом одноразрядного сумматора, входы старшего и предыдущего разрядов регистра преобразуемого числа соединены соответственно с выходами нервого и второго элементов И, а входы младщего и лоследующего разрядов регистра лреобразуемого числа соедшюны соответственно с выходами четвертого и третьего элементов И.

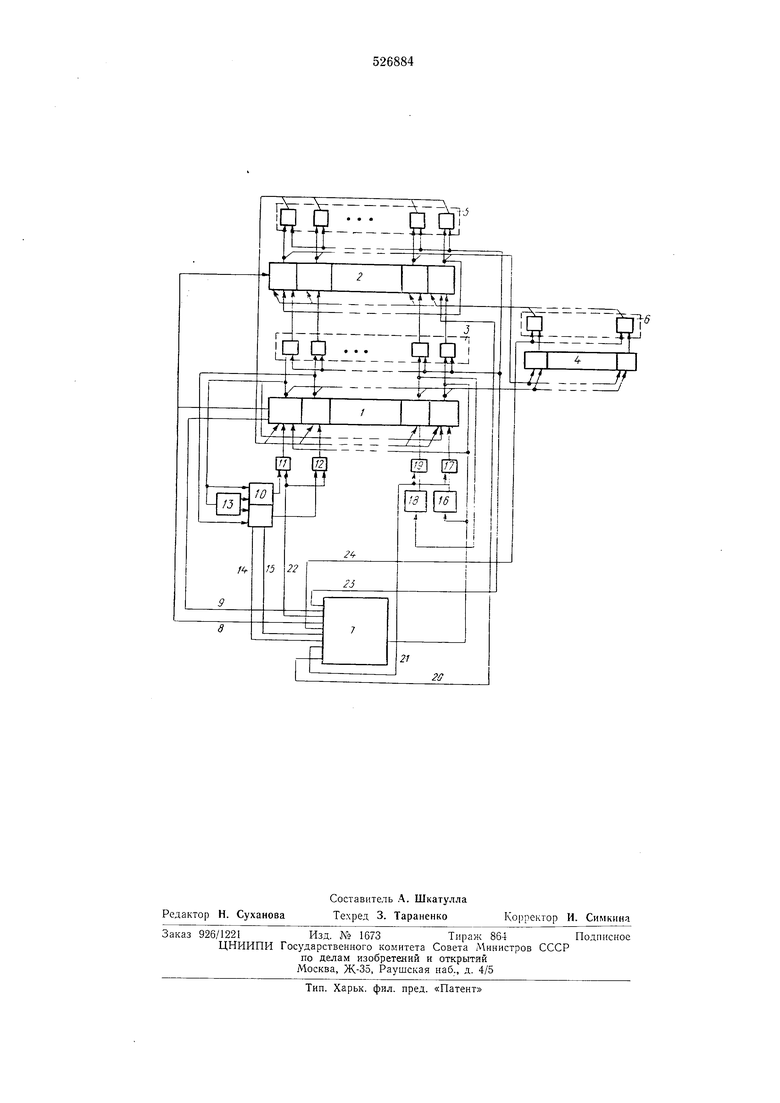

На чертеже представлена блок-схема предлагаемого преобразователя.

Преобразователь содержит сдвиговый регистр / преобразуемого числа и регистр 2 результата. Выходы регистра / через блок 3 элементов И подсоединены к входам одноименных разрядов регистра 2 и к входам многоразрядного вычислителя 4. Выходы регистра 2 через блок 5 элементов И подсоединены ,к входа.м одноименных разрядов регистра / и к входа.м уменьшаемого многоразрядного вычнтателя 4, выходы которого через блок 6 элбм.ентов И соединены с входами регистра 2. Регистры / и 2 связан с блоком 7 управления щнной 8, а регистр / кроме того - щиной 9. Выходы двух старщих разрядов регистра / подсоединены к (входам двухразрядного блока 10 алгебраического суммирования, выходы которого связаны через элементы И 11 и 12 с входами двух старших разрядов регистра /. К другим входам блока 10 алгебраического суммирования через умножитель 13 ;на константу подключен выход старщего разряда регистра 1. Блок 10 алгебраического суммирования соединен та1кже с блоком 7 управления щиной 14 сложения и щиной 15 вычитания. Выходы двух младщих разрядов регистра / связаны ico своими входами, причем первый разряд - через одноразрядный вычитатель .16 и элемент И 17, второй разряд - через одноразрядный сумматор 18 и элемент И /9. Вход .младшего разряда регистра 2 соединен шиной 20 с блоком 7 управления, который кроме того соединен шинами 21-24 с элементами И 17 и 19 и элементами И // и 12 соответственно.

Преобразователь кодов работает в двух режимах.

Перевод чисел в код с большим основанием.

Перед началом работы преобразуемое число занисывается в сдвиговый регистр /, блок 10 алгебраического суммирования по щине 14 настраивается на выч итания. Процесс преобразования осуществляется следующим образом.

Содержимое старщего разряда сдвигового регистра / с помощью умножителя 13 умножается на константу, равную S-R (R - основание исходной системы счисления, 5 - основание системы искомого шредставления), и вычитается в бло.ке 10 из содержимого двух старших разрядов регистра /. По сигналу на щине 22 результат записывается в старшие

разряды. После этого по сигналу на щине 9 полученный промежуточный результат сдвнгается на один разряд влево.

Эта проиедура повторяется k-1 раз, где k - число разрядов регистра /, и заверщается еще одним сдвигом влево. Каждый последующий цикл содержит на одну процедуру ме1гьше и на один сдвиг влево больше. Всего производятся k-1 ЦИ1КЛОВ, после чего полученное число переписывается в регистр 2.

Пример 1. Перевести число (Х) 1634 в код с основанием 10.

S-R 3

1634

X

3

3 133Г

с ДБ. 3341 3

Первый цикл

9 2441

сдв.

4412

X 3

12 ва сдв. 32Y2

У 1232 3

з;

Второй цикл

0932

сдв.

9320

X 3

27

и сдв. 6620 0662

Ответ: (X)io 662

Третий цикл опущен, так ка-к старший раз65 ряд равен нулю. Перевод чисел в код с меньшим основанием. Перед началом работы блок 9 настраивается -на выполнение операции сложения. Перевод осуществляется в три этапа. На первом этапе производится дополнительное преобразование исходного числа. При этом анализируется содержимое младшего разряда регистра /. Если число U S, то из него вычитается число S с помош,ью вычитателя 16, а к соседнему слева разряду прибавляется единица с памощью сумматора 18. Одновременно с этим Производится за-пись числа (R-S) в младший разряд регистра 2 по шине 20. Затем с помошью сигнала яа шине 8 ироизводится правый сдвиг на одни разряд в регистрах / и 2. Если число , то сразу производится правый сдвиг. Указанная П|роцедура повторяется k раз, а затем производится дополнительный (правый сдвиг, в результате этого в регистре 2 формируется коррекция. Второй этап заключается в том, что число, записанное в регистре 1, преобразуется так, как это олисано в примере 1, ic тем лишь отличием, что в блоке 10 числа суммируются, а 1не вычитаются. На третьем этапе по сигпалу на шине 23 число из регистра / переписывается в регистр 2, а корре-кция - из регистра 2 в регистр /, где она /преобразуется так же, waiK это описано Выше. Преобразованная коррекция вычитается из содержимого регистра 2 на вычитателе 4. Полученное число по сигналу па шине 23 фиксируется в регистре 2 -з качестве искомого результата. 2. Перевести число (X)i2 10. 11.10 в ,код с основанием 10.

сдв.

сдв.

два сдв.

сдз. 0274 Второй цикл

2740 2

+ :;Tтри сдз. 140 031 ретий цикл опущен (см. пример 1).

зычитатель

1896 03 И

1о82 Ответ: 1582 (Х),о регистр 1 2 И Первый цикл 3801 8013 16 9613 1396 о 2 J596 Второй щгхл 59бТ 2 1(Г 2Третий цикл 2 Г896 3этап регистр 1 ,, 0222 2 О 0222 X 2220 Пеазый t 2620 X 6202 74022 X. б274 ,Х - - -

Предлагаемое изобретелие позволяет расширить класс решаемых задач, а именно, позволяет осуществлять перевод чисел не только из системы с мепьшим основанием в систему с большим основанием, но и наоборот.

Формула изобретения

Преобразователь -кодов, содержаш,нй элементы И, регистр преобразуемого числа, выходы которого соединены с информационными входами нервого бло.ка элементов И, управляющий .вход которого соединен с первым выходом бло.ка управления, второй выход которого -соединен с первым сдвиговым входом регистра преобразуе1мого числа, выходы двух старших разрядов которого соединены с пнфорМационными входами блока алгебраического сусммирования, отличающийся тем, что, с целью расширения класса решаемых задач, в него введены второй п третий блоки элементов И, регистр результата, многоразрядный вычитатель, одноразрядный сумматор и одноразрядный вычитатель, лри этом первая группа входов многоразрядного вычитателя соединена с выходами регистра результата и входами второго блока элементов PI, а выходы подключены ,к информационным входам третьего блака элементов И, выходы .которого соединены с первой группой входов регнстра результата, вторая группа входов которого соединена с выходами первого блока элеме-нтов И, вход старшего разряда регнстра результата соединен с выходом его младшего разряда, а сдвиговый вход соединен со вторым сдвиговым входом регистра преобразуемого числа и третьим выходом блока управления, первый и четвертый выход которого соединены с управляющим входом второго и третьего элементов И соответственно, пятый и шестой выходы блока управления подключены к упра1вляющи1М входа м блока алгебраического суммирования, первый и второй выходы которого подключены к первым входам соответственно первого и второго элементов И. вторые входы (которых соединены с седьмым выходом блока управления, восьмой выход которого соединен с первыми входами третьего и четвертого элем-антов И, вторые входы которых соедине}1ы соответственно с выходами одноразрядного сумматора и одноразрядного вычитателя, девятый выход блока управления соединен с входом младшего разряда регистра результата, выход -младшего разряда регистра преобразуемого числа соединен с входами блока управления и одноразрядного вычитателя, выход последующего разряда регистра преобразуемого числа соединен с входом одноразрядного сумматора, входы старшего и предыдущего разрядов регистра преобразуемого числа соединены соответственно с выхода.ми первого и второго элементов И, а входы младшего и последующего разрядов регистра преобразуе-мого числа соединены соответственно с выходами четвертого и третьего элементов И.

Авторы

Даты

1976-08-30—Публикация

1973-09-14—Подача