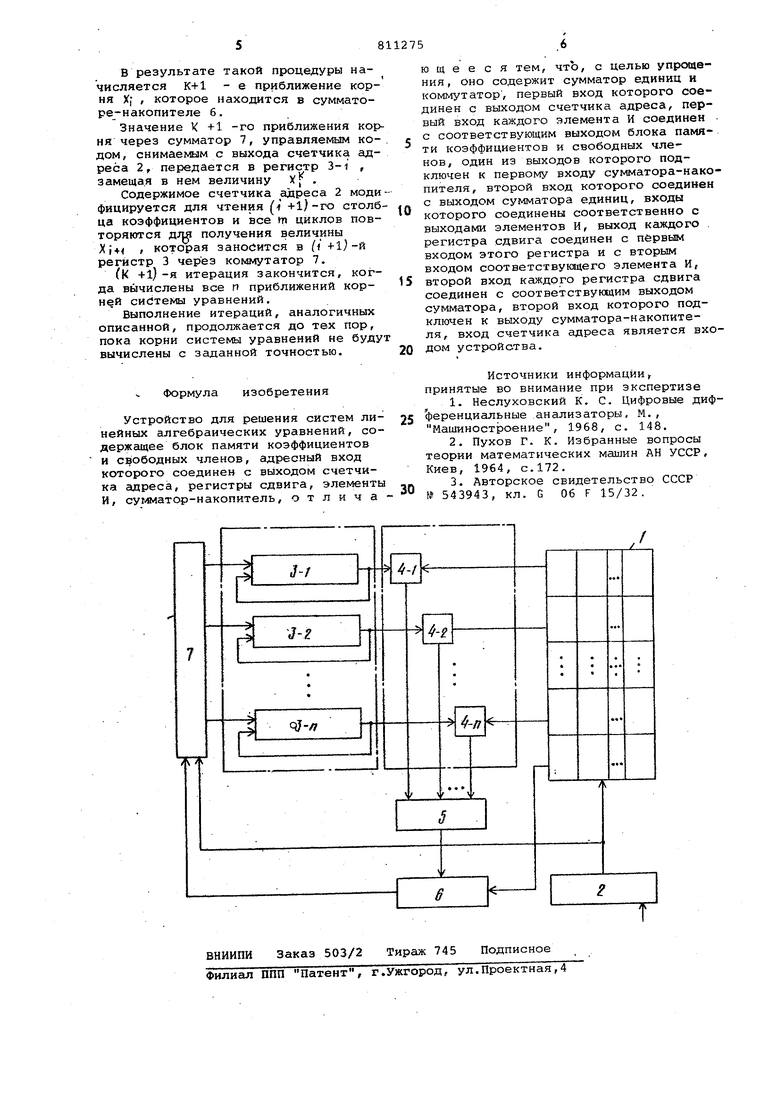

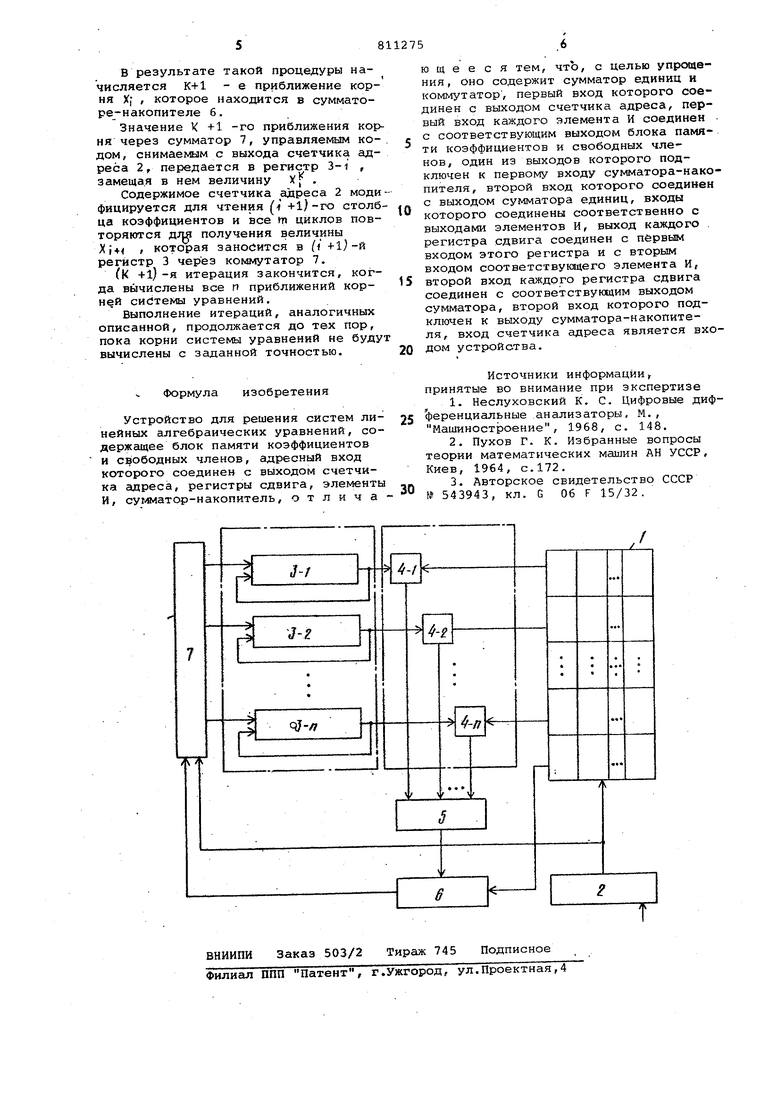

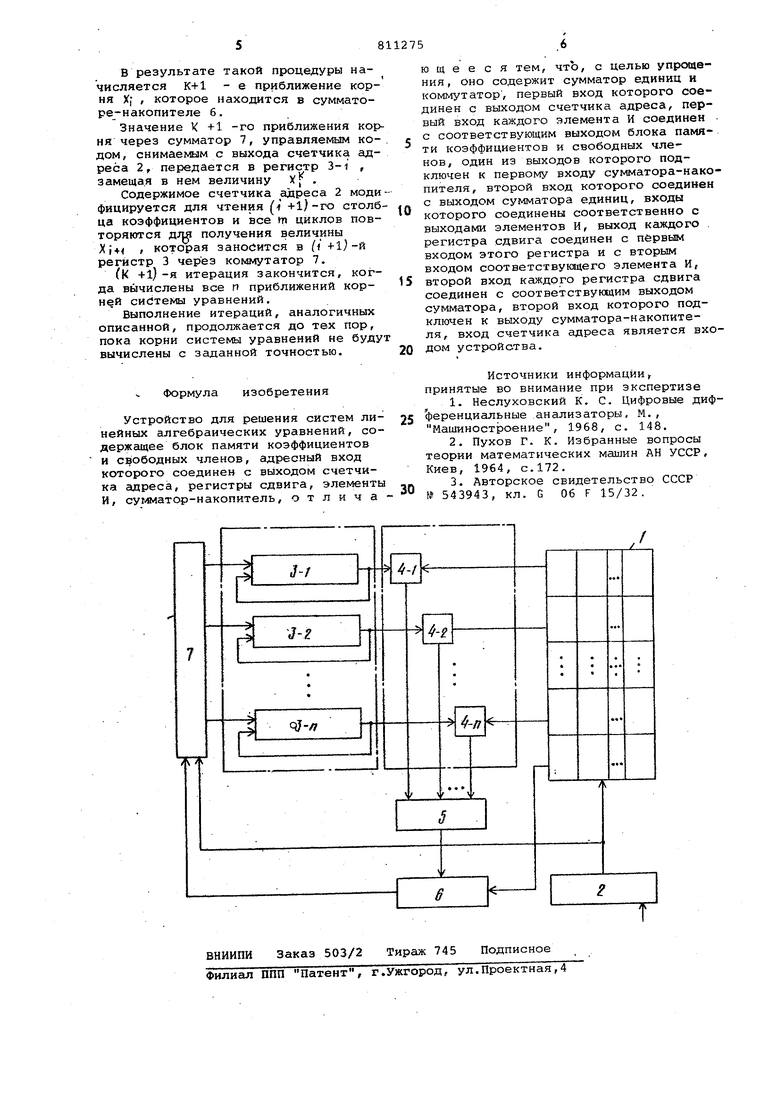

Изобретение относится к вычислительной технике и может быть исполь зовано при разработке специализированньах вычислительных машин и прО цессоров для решения систем линейны алгебраических уравнений. Известно устройство для решения систем линейных алгебраических урав нений tl} содержащее интеграторы к эффициентов, интегратор свободного члена ,и интеграторы неизвестных, пр чем выходы интеграторов коэффициент каждого столбца соединены.со входа интеграторов свободного члена того же столбца, выходы которых подключе ны ко входам интеграторов неизвестных того же столбца и ко входам интеграторов коэффициентов соответствующих строк. Недостатком этого устройства является большое количество используемо.го оборудования, а также запазда1ВЭ1ние в обработке приращений и трудность решения систем уравнеНИИ вйсоких порядков, а также сравнительно малое быстродействие. Известно также устройство для решения систем алгебраических уравнений 2, содержащее несколько групп регистров памяти коэффицентов, к выходам которых подключены первые входы соответствукмдих блоков умножения кода коэффидентов на знак приращения переменной, регистры накопления величин невязок, выходы которых подсоединены к соответствующим входс1м блока уравновешивания, и цифровые интеграторы накопления переменных,вхо1У каждого из которых соединены са вторыми входами блоков умножения соответствующей группы и с соответствующими выходами блока уравновешивания . Недостатком этого устройства является большой объем требуемого оборудования даже для систем уравне.ний невысокого порядка, причем сложность устройства увеличивается по мере увеличения порядка решаемой системи. Из известных устройств наиболее близким по технической сущности к изобретению является устройство для решения систем линейных алгебраических уравнений И, содержащее одноразрядные сумматоры-вычитателн, сдвиговые регистЕйл,.реверсивные счетчики, блоки анализа, элементы И/ИЛИ. Управлякнцие входы сдвиговых регистрой соединены с управляющей шиной, а выходы - с первыми входами соответствующих одноразрядных сумматоров-вычитателей, объединенных в U столбцов по (h +1) последовательно соединенных одноразрядных сумматоров-вычитателей в каждом. Управляющие входы одноразрядных сумматоров-вычитателей каждой строки соединены со входами соответствующего реверсивного сяетчика, выход п -го одноразрядного сумматоравычитателя каждого столбца соединен с первым входом (h +l)-ro одноразрядного сумматора-вычитателя и с пер вым входом элемента ИЛИ, выход которого соединен со входом (п +1)-го сдвигового регистра. Выход знакового разряда (n+l)-ro сдвигового регистр соединен с входом соответствующего реверсивного счетчика. Выход (и+1)-го сдвигового регистр. соединен со вторым входом блока анализа и через первый элемент И - со вторым входом элемента ИЛИ и со вторым входом перого одноразрядного сумматора-вычитс1теля соответствующего столбца, а через второй элемент И - со ВТОЕ входом (h+l)-ro одноразрядного сумматора-вычитателя, выход которого со единен с третьим входом блока анализ Вторые входы элементов И всех столбцов и управляющие входы реверсивных счетчиков соединены с управляющей шиной. НГедостатком этого устрюйства такж является большой объем оборудования. Целью изобретения является упрощение устройства. Поставленная цель достигается тем, что устройство, содержащее блок памяти коэффициентов и свободных членов, сщресный вход которого соединен с выходом счетчика адреса, регистры сдвига, элементы И, сумглатор-накопитель, содержит сумматор единиц и коммутатор, первый вход кот рого соединен с выходом счетчика адреса. Первый вход каждого элеме нта И соединен с соответствующим выходом блока памяти коэффициентов и свободных членов, один из выходов которого подключен к первому входу сумматора-накопителя, второй вход которог соединен с выходом сумматора единиц, входы которого соединены соответсственно с .выходами элементов И. Выход каждого регистра сдвига соединен со своим первым входом и с вторым входом соответствующего элемента И. Второй вход каждого регистра сдвига соединен с соответствующим выходом коммутатора, второй вход которого подключен к выходу сумматора-накопителя. Выход счетчика адреса является входом устройства. Схема устройства представлена на чертеже, где обозначены блок 1 памяти коэффициентов и свободных членов, счетчик 2 адреса, регистры сдвига 3 - 3f, , элементы И 4 - 4п , сумматор единиц 5, сумматор-накопи -. уель б и коммутатор 7. Устройство работает следующим образом. Для решения уравнения системы первоначально преобразуются к виду , a,j Xj 4 1,2... ,п , И коэффициенты системы и свобод,-ч ные члены « записываются в блок 1памяти . Начальные приближения корней заносятся в регистры 3 сдвига. Каждое (k; +l)-е приближение корней вычисляется по следующей формуле:«.+1), --1 {Ki-n . (К.) Х bii- OijXj V.5. q)Xj Приближение X ; в каждой итерации вычисляется за гт) циклов, в каждом из которых выполняется m так тов. В каждом цикле выполняются следующие действия. В первом цикле, первом такте из блока 1 считываются младшие разряды всех коэффициентов а,( 12 ...,1) и логически умножаются на элементах И 4п на младшие разряды чисел (приближений корней), находящихся в регистрах 3. Образованная на выходе сум1-1атора единиц 5 сумма произведений младших разрядов всех коэффициентов на младшие разряды всех приближений корней складывается с содержимым сумматора-накопителя 6 и младшим разрядом свободного члена Ъ. В сумматоре-накопителе 6 делается сдвиг на один разряд в сторону старших разрядов. К счетчику 2добавляется единица в младший разряд, что вызывает модификацию адреса. В первом цикле, втором такте повторяется процедура, аналогичная описанной в первом такте для следующих разрядов коэффициентов за исключением того, что во втором и последукяцих тактах цикла очередной разряд к сумме не добавляется. В первом цикле такие такты повторяются m раз. Второй цикл начинается со сдвига содержимого сумматора-накопителя на (т -1) разряд в сторону младших разрядов и циклического сдвига содер. жимого всех регистров 3 на один разряд в сторону младших разрядов. Таким образом, ко входам элементов И подключены очередные разряды приближений неизвестных, хранящихся в регистрах 3. Далее цикл вычислений выполняется, как и предыдущий. число циклов вычислений, которое требуется выполнить, равно in {по числу разрядов кодов чисел, хранимых в региртрах сдвига З).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для решения системлиНЕйНыХ уРАВНЕНий | 1978 |

|

SU798862A1 |

| Устройство для решения системлиНЕйНыХ АлгЕбРАичЕСКиХ и диф-фЕРЕНциАльНыХ уРАВНЕНий | 1978 |

|

SU798860A1 |

| Устройство для решения систем ли-НЕйНыХ АлгЕбРАичЕСКиХ уРАВНЕНий | 1978 |

|

SU811274A1 |

| Устройство для решения систем линейных алгебраических уравнений | 1975 |

|

SU543943A1 |

| Многоканальное устройство дляРЕшЕНия СиСТЕМ лиНЕйНыХ АлгЕбРАичЕС-КиХ уРАВНЕНий | 1978 |

|

SU807318A1 |

| Узловой элемент цифровой сетки для решения краевых задач | 1984 |

|

SU1246111A1 |

| Преобразователь кодов | 1973 |

|

SU526884A1 |

| Устройство для вычисления элементарных функций | 1975 |

|

SU553612A1 |

| УСТРОЙСТВО АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ | 1992 |

|

RU2042269C1 |

| Устройство для решения системлиНЕйНыХ АлгЕбРАичЕСКиХ уРАВНЕНий | 1978 |

|

SU805336A1 |

Авторы

Даты

1981-03-07—Публикация

1978-09-18—Подача