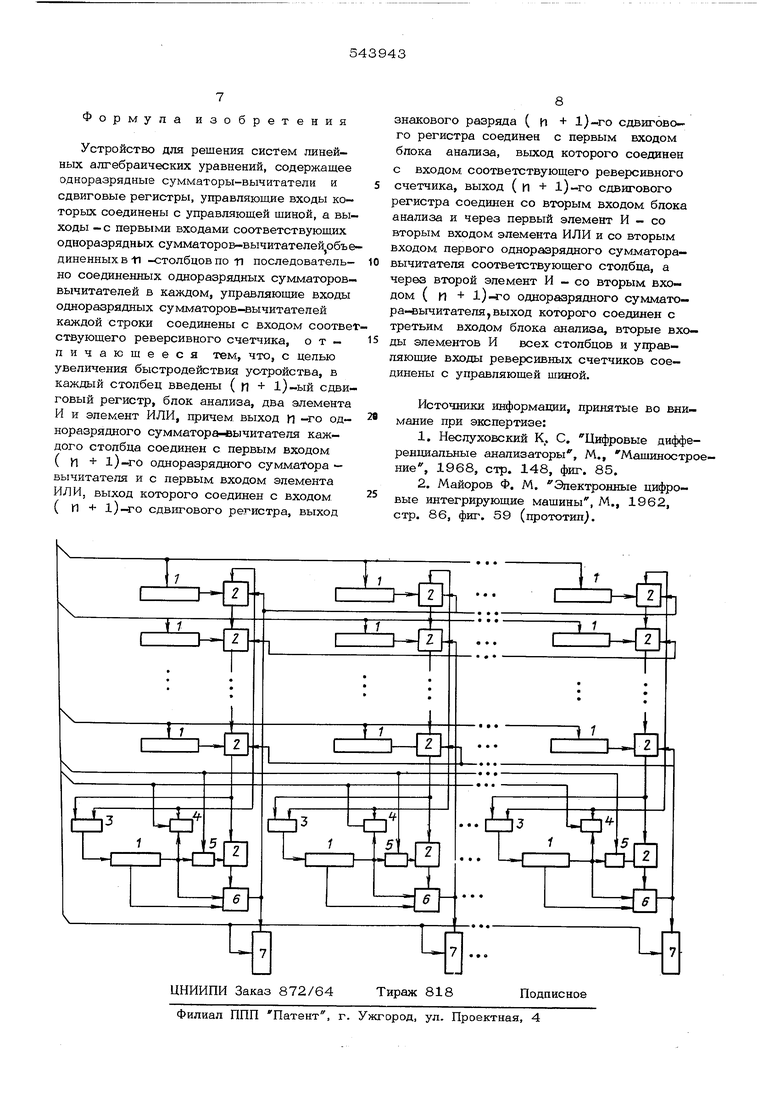

( И + l)-го сдвигового регистра, выход знакового разряда ( И + l)-го сдвигового регистра соединен с первым входом блока анализBj выход которого соединен с входом соответствующего реверсивного счет- чика, выход (и + l)-ro сдвигового регистра соединен со вторым входом блока анализа и через первый элемент И - со вторым входом элемента ИЛИ и со вторым входом первого одноразрядного сумматора-вы- читателя соответствующего столбца, а через второй элемент И - со вторым входом ( П + l)-ro одноразрядного сумматора- вычитателя, выход которого соединен с третьим входом блока анализа, вторые входы элементов И всех столбцов и управляющие входы реверсивных счетчиков соединены с управляющей щиной.

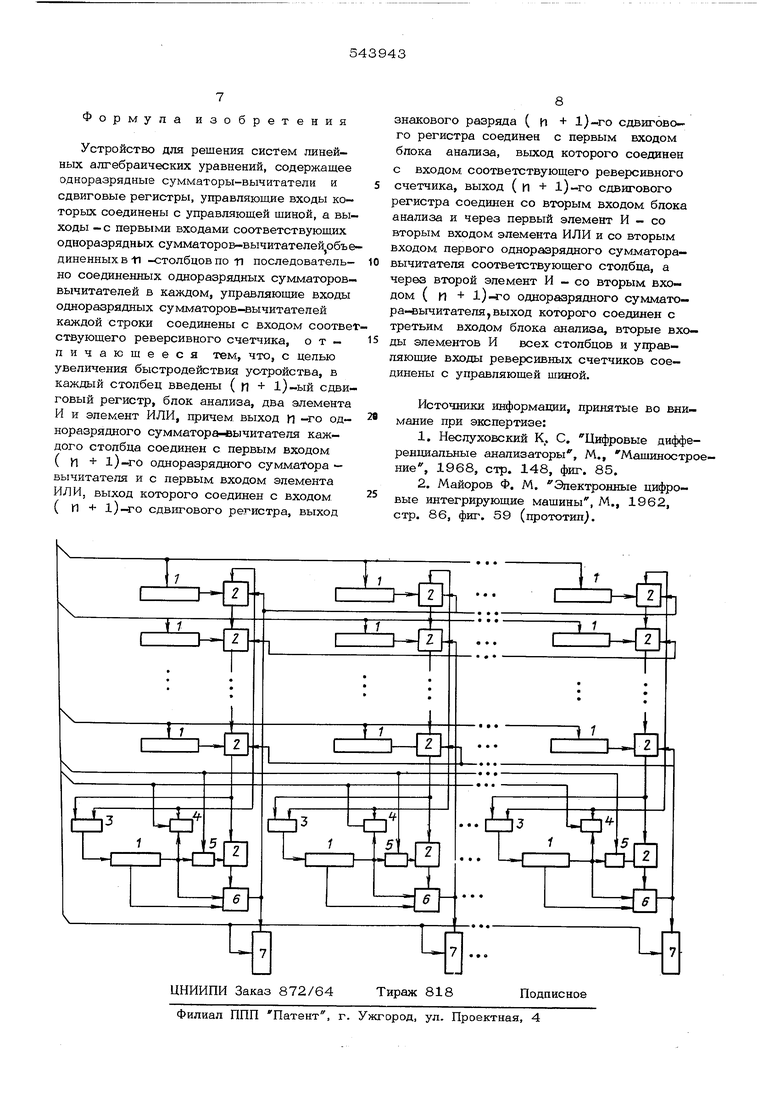

На чертеже изображена блок-схема предлагаемого устройства.

Устройство состоит из сдвиговых регистров 1, одноразрядных сумматоров-вычита- телей 2, элементов ИЛИ 3, элементов И 4, 5j блоков анализа 6 и реверсивных счетчиков 7,

Блок анализа 6 предназначен для выделения знака разности невязок р -ой и (р -1)-ой итерации соответствующего,уравнения системы, определения знака прираше- ния соответствующего неизвестного и запоминания кода знака на время итерации.

Устройство работает следующим, образом.

Коды коэффициентов Q., при неизвестных системы, уравнений заносятся в соответствуюшие сдвиговые регистры 1. В ( ц + l) ые сдвиговые регистры заносятся соответственно коды свободны.х членов Ь; блоке 6 устанавливается код знака соответствующего свободного члена Ь; Ре- версивные счетчики 7 устанавливаются в нулевое состояние j ( И + 1)-ые одноразрядные сумматоры-вычитатели 2 работают в режиме вычитания, С выхода ( + 1 )-го сдвигового регистра 1 код соответствую- щего свободного члена Ь- . начиная с млад- щих разрядов, через элемент И 4 поступает на второй вход первого одноразрядного сумматора-вычитателя 2 соответствующего столбца, а через элемент ИЛИ 3 перезаписывается в ( п + 1)-ый сдвиговый регистр 1. Этот код, просуммировавшись с соответствующими коэффициентами, поступивщими со сдвиговых регистров, подается через элемент ИЛИ 3 в (h + 1 )-ый регистр 1 и на первый вход соответствующего (Т1 + 1J-го одноразрядного сумматора-вычита-

Т8ЛЯ 2, на второй вхоц которого через элемент И 5 поступает код из {-Tl + 1) - го сдвигового регистра 1, В зависимости от результатов вычитания ( р - 1 )-ой ир-ой невязок соответствующий код сигнала с выхода ( п + 1)-го одноразрядного сумматоравычитателя 2 подается на третий вход блока анализа 6, на первый и второй входы которого поступают в этот момент знаки прдыдущей и настоящей невязок. По коду сигнала на своем третьем входе блок анализа 6 определяет код приращения Д X; на своем выходе. Код приращения Д X с выхода блок анализа 6 подается на вход счатчика 7, где суммируется с предыдущим содержимым последнего и на управляющие входы всех одноразрядных сумм.аторов-вычитателей 2 соответствующих строк для установления ре- жим.а работы одноразрядных сумматоров-вычталай. После каждой итерации по управляющему сигналуз подаваемому на управляющие входы реверсивных счетчиков 7, их со.держимые сдвигаются на один разряд в сторону старших разрядов. По управляющим сигналам, поступающим на управляющие входы сдвиговых регистров 1 соответствующих строк, производится сдвиг кодов соответствующих коэффициентов в сторону младщих разрядов и их перезапись в тот же регистр,

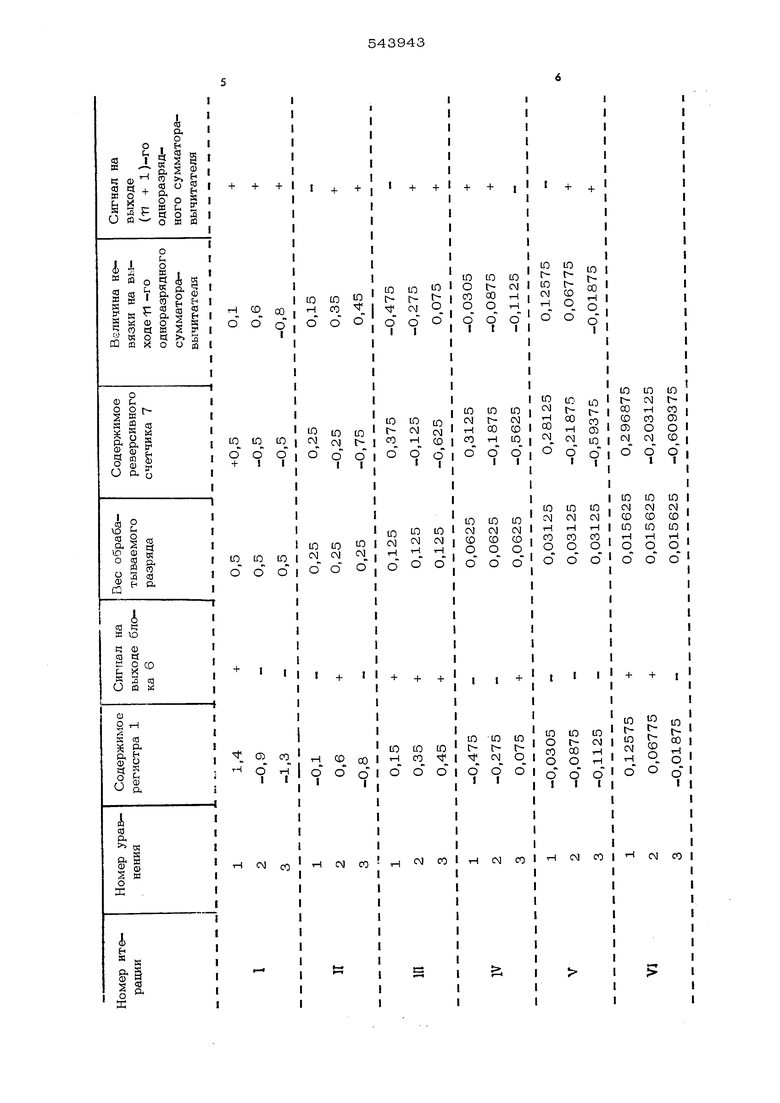

В качестве илпкхзтрахщи работы устройства проведено рещение следующей системы алгебраических уравнений;

1Х + :/,4;

Xi + 3XjfXj -D,9-,

Х -Ха-ьЗХз -,3,

Точное рещение данной системы

,з; ,а , ,6.

Считают что величины неизвестных не превосходят единицы, т.е. решение начинают со старщего разряда, вес которого равен О, 5, Процесс рещвния сведен в таблицу.

Технико-экономический эффект, который достигнут за счет введения в каждый столбец ( п + 1)-го сдвигового регистра, блока анализа, двух элементов И и элемента ИЛИ, а также новых связей между блоками, состоит в том, что быстродействие предлагаемого устройства в 2 /к раз больще по сравнению с известными устройствами, что, например, при разрядности k -10 дает выигрыщ по быстродействию примерно в 100 раз.

Формула изобретения

Устройство для решения систем линейных алгебраических уравнений, содержащее одноразрядные сумматоры-вычитатели и

сдвиговые регистрь, управляющие входы которых соединены с управляющей шиной, а выходы - с первыми входами соответствующих одноразрядных сумматоров-вычитателей объединенныхвп -столбцов по п последователь- но соединенных одноразрядных сумматороввычитателей в каждом, управляющие входы одноразрядных сумматоров-вычитателей каждой строки соединены с входом соотвествующего реверсивного счетчика, о т личающееся тем, что, с целью увеличения быстродействия ус-тройства, в каждый столбец введены ( П + 1)-ый сдвиговый регистр, блок анализа, два апемента И и элемент ИЛИ, причем выход ц -го одноразрядного сумматора- ычитателя каждого столбца соединен с первым входом ( И + l)-ro одноразрядного сумматора - вычитателя и с первым входом элемента ИЛИ, выход которого соединен с входом

( И + l)-ro сдвигового регистра, выход

8

знакового разряда ( h + 1}-го сдвигового регистра соединен с первым входом блока анализа, выход которого соединен с входом соответствующего реверсивного счетчика, выход ( и + 1)-го сдвигового регистра соединен со вторым входом блока анализа и через первый элемент И - со вторым входом элемента ИЛИ и со вторым входом первого одноразрядного сумматора- вычитателя соответствующего столбца, а через второй элемент И - со вторым входом ( И + 1)-го одноразрядного сумматора-вычитателя,выход которого соединен с третьим входом блока анализа, вторые входы элементов И всех столбцов и управляющие входы реверсивных счетчиков соединены с управляющей щиной.

Источники информации, принятые во внимание при экспертизе:

1.Неслуховский К. С. Цифровые дифференциальные анализаторы, М., Машинострние, 1968, стр. 148, фиг. 85.

2.Майоров Ф. М. Электронные цифровые интегрирующие мащины, М., 1962, стр. 86, фиг. 59 (прототип.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для решения систем ли-НЕйНыХ АлгЕбРАичЕСКиХ уРАВНЕНий | 1978 |

|

SU811275A1 |

| Устройство для решения системлиНЕйНыХ АлгЕбРАичЕСКиХ и диф-фЕРЕНциАльНыХ уРАВНЕНий | 1978 |

|

SU798860A1 |

| Многоканальное устройство дляРЕшЕНия СиСТЕМ лиНЕйНыХ АлгЕбРАичЕС-КиХ уРАВНЕНий | 1978 |

|

SU807318A1 |

| Устройство для решения систем ли-НЕйНыХ АлгЕбРАичЕСКиХ уРАВНЕНий | 1978 |

|

SU811274A1 |

| Устройство для решения системлиНЕйНыХ уРАВНЕНий | 1978 |

|

SU798862A1 |

| Устройство для решения системлиНЕйНыХ АлгЕбРАичЕСКиХ уРАВНЕНий | 1978 |

|

SU805336A1 |

| Матричный вычислитель экспоненты | 1981 |

|

SU1024911A1 |

| Устройство для вычисления скалярного произведения двух векторов | 1981 |

|

SU955088A1 |

| Устройство для вычисления произведения векторов (его варианты) | 1984 |

|

SU1280389A1 |

| Устройство для вычисления элементарных функций | 1981 |

|

SU999046A1 |

Авторы

Даты

1977-01-25—Публикация

1975-02-25—Подача