Изобретение относится к запоминающим устройствам, и может использоваться при проектировании стендовой аппаратуры для контроля блоков памяти ifo основному авт. св. № 607283 известно устройство, содержащее источник управляющих импульсов, первый выхо которого подключен ко входу формирова теля опросного тока, регистр числа, входы которого соединены со входами устройства, а выходы - с одними входами блока сравнения, блок индикации, элементы И, дополнительный формирователь опросного тока и счетный триггер один выход которого подключен к первому входу первого элемента И, а другой - к первым входам второго, третьего и четвертого элементов И, первый и второй-выходы источника управлякйцих импульсов соединены соответственно со вторыми входами второго и третьего элементов и , третий и четвертый выходы источника управления импульсов под ключены соответственно ко вторым входам первого и четвертого элементов И и входу счетного триггера, выходы первого, второго и четвертого элементов И соединены соответственно с управляющим входом регистра числа, входом ополнительного формирователя опросного тока и одним из входов блока индикации, третий вход третьего элемента И подключен к выходу блока сравнения, другие входы которого соединены со входами устройства, а выход третьего элемента И подключен к другому входу блока индикации 1). Однако это устройство, обеспечивая контроль ошибок типа прошивка в одно окно , не позволяет обнаруживать, ряд технологических дефектов блоков памяти, вызванных замыканиями между отдельными проводами в жгуте, что снижает область применения устройства. Цель изобретения - расширение овласти применения устройства за счет обеспечения возможности выявления коротких замыканий между информационными проводами. Поставленная цель достигается тем, что устройство содержит дополнительный счетный триггер и коммутатор, то новый вход которого подключен к дополнительного формирователя опросного тока, управляющий вход - к первому выходу дополнительного счетного триггера,-второй выход которого подсоединен к одним из входов первого элемента И и блока индикации, вход дополнительного счетного триггера соединен с первым выходом счетного триггера, выход блока сравнения подключен к одному из входов источника управляющих импульсов.

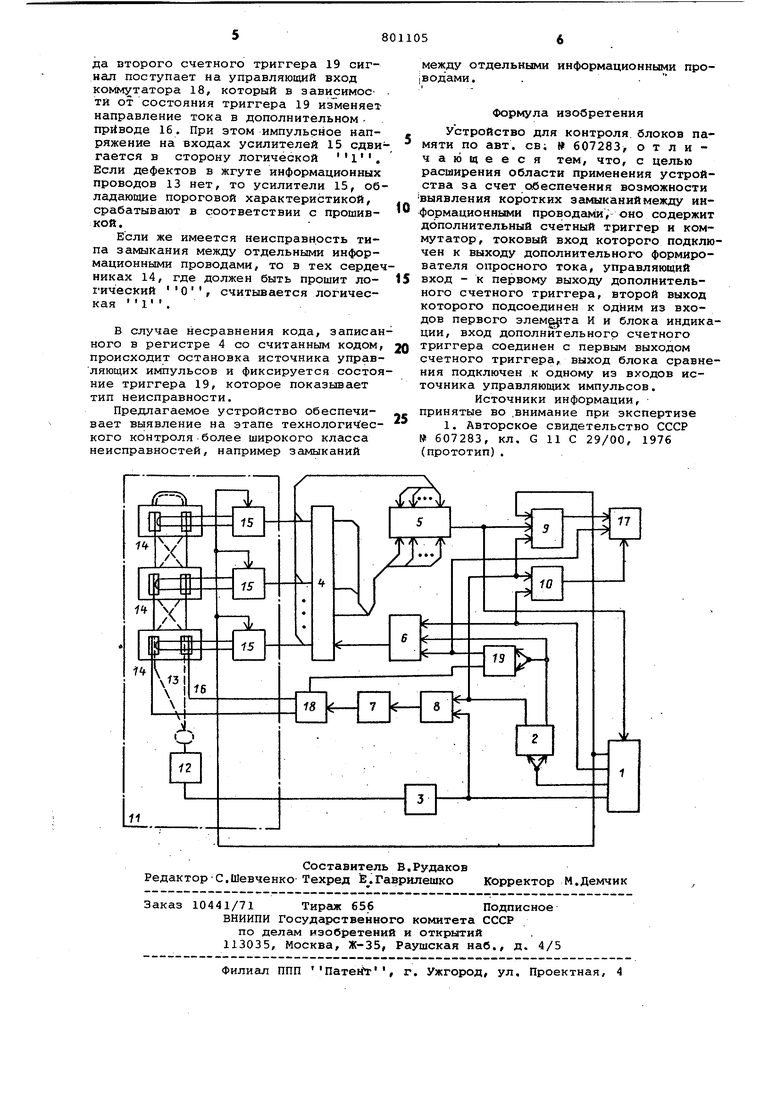

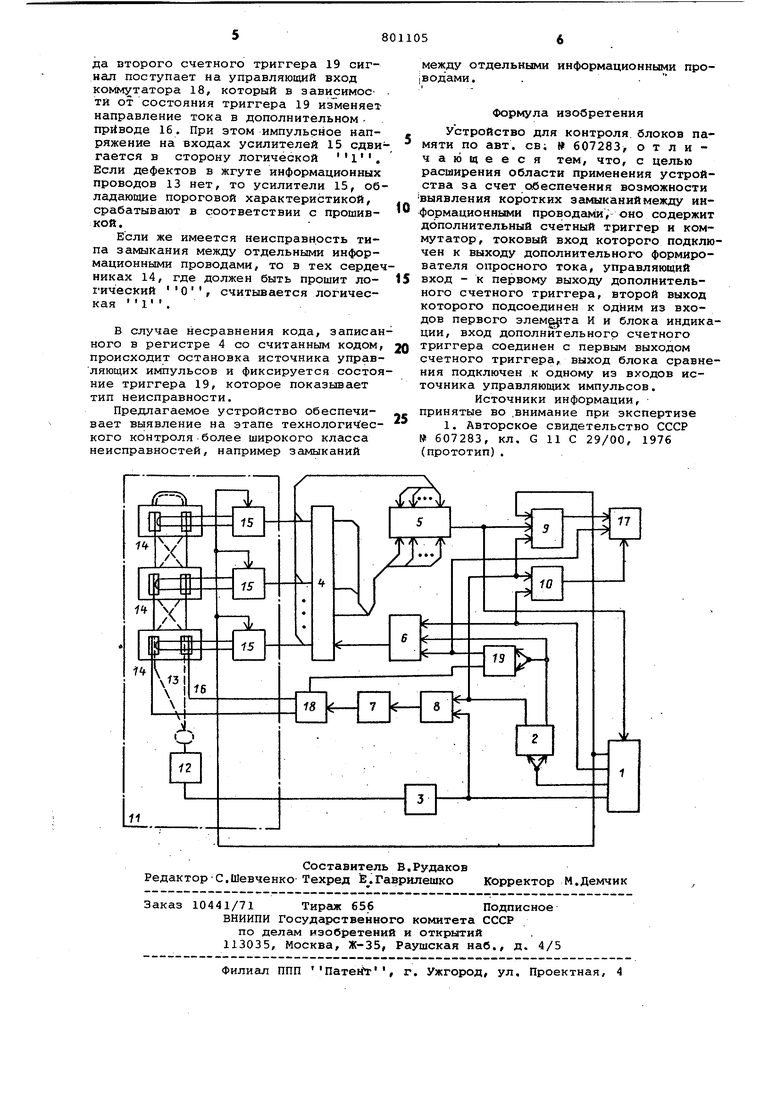

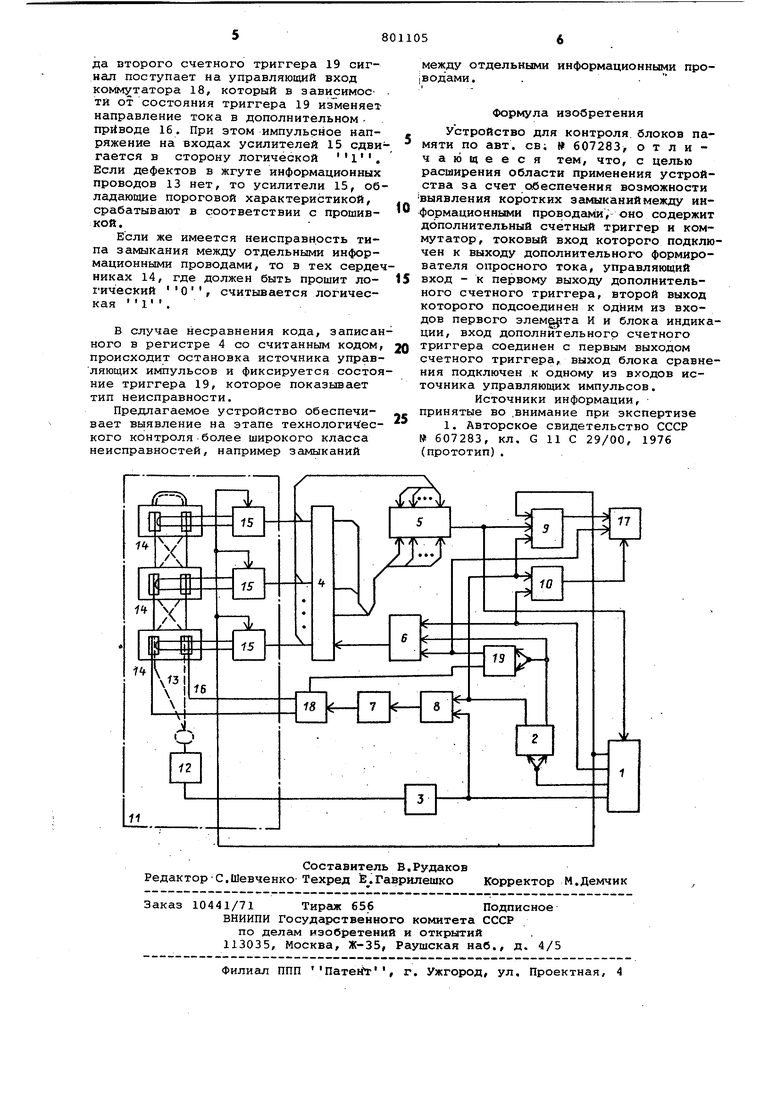

На чертеже представлена функциональная схема устройства.

Устройство содержит источник. 1 управляющих импульсов, счетный триггер 2, формирователь 3 опросного тока, регистр 4 числа, блок 5 сравнения, первый элемент И 6, дополнительный формирователь 7. опросного тока, второй 8, третий 9 и четвертый 10 элементы И. Входы и выходы устройства подключены к выходам и входам контролируемого блока 11 памяти. Блок 11 содержит дешифратор 12, информационные провода 13, прошивающие разрядные.сердечники 14, однополярные усилители 15 считывания, дополнительный провоД 16.В состав устройства для контроля блоков памяти входят также блок 17 индикации, коммутатор 18 и дополнительный счетный триггер 19.

Один выход триггера 2 подключен к первому входу элемента И 6, а другойк первым входам элементов И 8-10, первый и второй выходы источника 1 управляющих импульсов соединены соответственно со вторыми.входами элементов И 8 и 9, третий и четвертый выходы источника 1 управляющих импульсов подключены соответственно ко вторым входам элементов И 6 и 10, выходы элементов И 6, 8 и 10 соединены соответственно с управляющим входом регистра 4 числа, входом формирователя 7 и одним из входов блока 17 индикации, третий вход элемента И 9 подключен к выходу блока 5 сравнения, другие входы которого -соединены со входами устройства, а выход элемента И 9 подключен к другому входу блока 17 индикации,

Токовый вход коммутатора 18 подключен к выходу дополнительного формирователя 7 опросного тока, управляющей вход - к первому выходу счетного триггера- 19, второй выход которого подсовдинен к третьему входу первого элемента И б и к третьему входу блока 17 индикации. Вход счетного триггера 19 соединен с первым выходом счет-; него триггера 2. Выход блока 5 сравнения подключен ко входу основного источника 1 управляющих: импульсов. Устройствб работает следующим образом.

С одногоиз выходов счетного триггера 2 подаётся импульс разрешения на прохождение через элемент.И 8 импуль.сов с первого выхода источника 1 управляющих импульсов, а также элементы И 9 и 10 соответственно импульсов со второго и третьего выходов источника 1 управляющих импульсов, только в четном цикле работы устройства,

С другого выхода счетного триггера 2 на элемент И 6 подается импульс раз

решения на прохождение импульсов с третьего выхода источника 1 управляющих импульсов только в нечетном цикле Импульсы с первого выхода источника 1 управляющих импульсов поступают на вход .формирователя 3, который в каждом цикле формирует ток через дешифратор 12 в информационных проводах 13 блока 11 памяти, прошивающих ра.зрядные сердечники 14 в различных направлениях. Наведенная от этого тока в разрядных обмотках сердечников 14 ЭДС сигналов подается на входы однополярных усилителей 15 считывания, на стробируемые входы которых поступает в каждом цикле строб со второго выхода источника i управляющих импульсов .

С выходов усилителей 15 в момент строба считанный информационный код поразрядно подается на входы регистра 4 числа, предварительно в пеювом и далее в каждом нечетном цикле установленного в О импульсом с выхода элемента И 6, и на один из входов блока 5 сравнения.

С выхода регистра 4 числа записанный в первом цикле информационный код снимается на другие входы блока 5 сравнения.

Во втором цикле работы устройства с выхода элемента И 8 импульсы подаются на вход дополнительного формирователя 7, который в четные циклы в дополнительном проводе 16, прошивающем все разрядные сердечники в направлении, соответствующем логическому О, формирует ток .такой полярности, что импульсное напряжение считанных сигналов, формируемых с помощью основного формирователя 3, сдвигается в сторону логического О. При этом в тех разрядах, где прошивка выполнена в одно окно, т.е. с ошибкой, сигнал на входе усилителей 15 считывания соответствует логическому О; тогда как в предыдущем цикле без дополнительного кода, сигнал соответствует логической . Считанный При этом во время прихода- строба с выходов усилителей 15 код, не изменяя записанной в первом цикле информации в регистре 4 числа, поступает на один из входов блока 5 сравнения кодов. При появлении в элементе И 9 разрешаю,щего импульса,на вход блока 17 индикации, предварительно установленного

импульсом с выхода элемента

И 10,проходит сигнал сравнения информационного кода,записанного в регистр :4 числа в первом цикле,с кодом,снятым с однополярных усилителей 15 во втором цикле. Несравнение кодов высвечивается блоком 17 индикации,что соответствует ошибке типа прошивка в одно окно .

Сигнал с первогоI выхода счетного триггера 2 поступает на вход второго счетного триггера 19, С первого выхода второго счетного триггера 19 сигнал поступает на управляющий вход ко№1;/татора 18, который в зависимоетй от состояния триггера 19 изменяео направление тока в дополнительном приводе 16. При этом импульсное напряжение на входах усилителей 15 сдви гается в сторону логической . Если дефектов в жгуте информационных проводов 13 нет, то усилители 15, об ладающие пороговой характеристикой, срабатывают в соответствии с прошивкой , Если же имеется неисправность типа замыкания между отдельными информационными проводами, то в тех серде никах 14, где должен быть прошит ло1ический О , считывается логическая 1 . в случае несравнения кода, записан ного в регистре 4 со считанным кодом происходит остановка источника управляющих импульсов и фиксируется состоя ние триггера 19, которое показывает тип неисправности. Предлагаемое устройство обеспечивает выявление на этапе технологического контроля-более широкого класса неисправностей, например замыканий между отдельными информационными про|ВОдами. .. Формула изобретения Устройство для контроля блоков памяти по авт. ев; 607283, отличающееся тем, что, с целью расширения области применения устройства за счет обеспечения возможности выявления коротких замыканиймежду информационными проводами, оно содержит дополнительный счетный триггер и коммутатор, токовый вход которого подключен к выходу дополнительного формирователя опросного тока, управляющий вход - к первому выходу дополнительного счетного триггера, второй выход которого подсоединен к одним из вхо дов первого элеме.рта И и блока индикации, вход дополнительного счетного триггера соединен с первым выходом счетного триггера, выход блока сравнения подключен к одному из входов источника управляющих импульсов. Источники информации, принятые во .внимание при экспертизе 1. Авторское свидетельство СССР 607283, кл, G 11 с 29/00, 1976 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля блоков памяти | 1976 |

|

SU607283A1 |

| Устройство для контроля монтажа | 1985 |

|

SU1352505A1 |

| Устройство для автоматического регулирования температуры | 1988 |

|

SU1645945A1 |

| Измеритель линейных перемещений | 1986 |

|

SU1401273A1 |

| Преобразователь линейного перемещения в код | 1984 |

|

SU1274156A1 |

| Устройство для телеизмерения давления скважинных штанговых насосов | 1990 |

|

SU1711218A1 |

| Устройство для централизованного контроля и оперативного управления | 1977 |

|

SU633029A1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

| Устройство для ввода-вывода информации | 1983 |

|

SU1136141A1 |

| Аналого-цифровой преобразователь неэлектрических величин | 1985 |

|

SU1403374A1 |

Авторы

Даты

1981-01-30—Публикация

1979-03-26—Подача