(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ БЛОКОВ

1 ПАМЯТИ

2

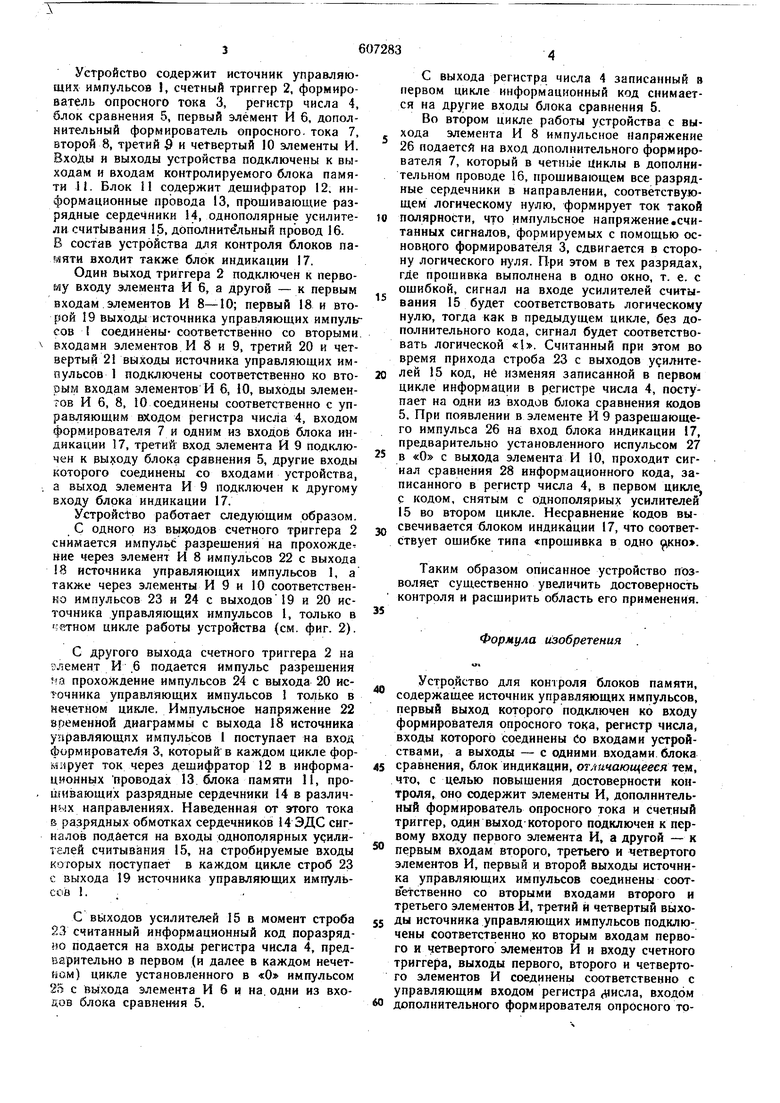

Устройство содержит источник управляющих импульсов , счетный триггер 2, формирователь опросного тока 3, регистр числа 4, блок сравнения 5, первый элемент И 6, дополнительный формирователь опросного, тока 7, второй 8, третий 5 и четвертый 10 элементы И. и выходы устройства подключены к выходам и входам контролируемого блока памяти 11. Блок 11 содержит дешифратор 12. информационные провода 13, прошиваюи1ие разрядные сердечники 14, однополярные усилители считУвания 15, дополнительный провод 16. В состав устройства для контроля блоков павляти входит также блок индикации 17.

Один выход триггера 2 подключен к первому входу элемента И 6, а другой - к первым входам элементов И первый 18 и второй 19 выходу источника управляющих импульсов I соединены- соответственно со вторыми входами элементов И 8 и 9, третий 20 и четвертый 2 выходы источника управляющих импульсов 1 подключены соответственно ко вторым входам элементов И 6, 10, выходы элементов И 6, 8, 10 соединены соответственно с управляющим входом регистра числа 4, входом формирователя 7 и одним из входов блока индикации 17, третий вход элемента И 9 подключен к выходу блока сравнения 5, другие входы которого соединены со входами устройства, а выход элемента И 9 подключен к другому входу блока индикации 17.

Устройство работает следующим образом.

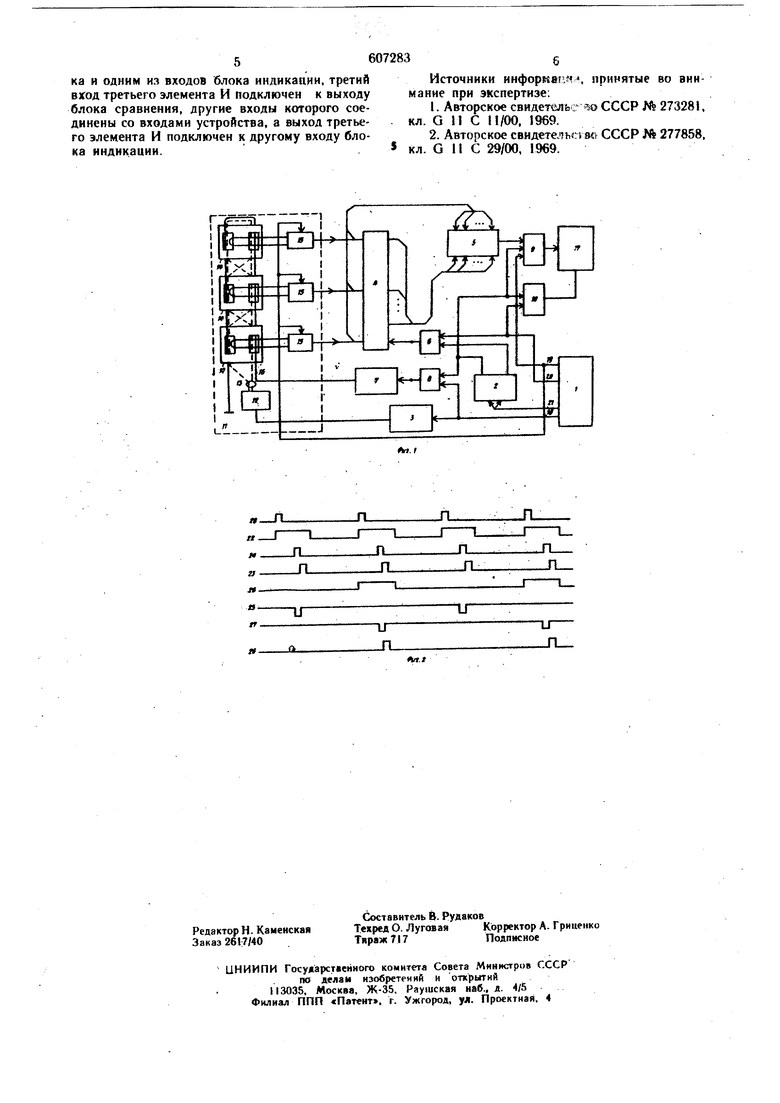

С одного из выводов счетного триггера 2 снимается импульс разрещения на прохожде ние через элемент И 8 импульсов 22 с выхода 18 источника управляющих импульсов 1, а также через элементы И 9 и 10 соответственно импульсов 23 и 24 с выходов19 и 20 источника управляющих импульсов 1, только в «етном цикле работы устройства (см. фиг. 2).

С другого выхода счетного триггера 2 на элемент И .6 подается импульс разрешения tia прохождение импульсов 24 с выхода 20 источника управляющих импульсов 1 только в нечетном цикле. Импульсное напряжение 22 временной диаграммы с выхода 18 источника управляющих импульсов 1 поступает на вход формировате;5я 3, который в каждом цикле формирует ток через дешифратор 12 в информационных проводах 13 блока памяти 11, прошивающих разрядные сердечники 14 в различных направлениях. Наведенная от этого тока в разрядных обмотках сердечников 14 ЭДС сигналов подается на входы однополярных удилителей считывания 15, на стробируемые входы которых поступает в каждом цикле строб 23 с выхода 19 источника управляющих импульСОВ 1..

с выходов усилителей 15 в момент строба 23 считанный информационный код поразрядно подается на входы регистра числа 4, предварительно в первом (и далее в каждом нечетном) цикле установленного в «О импульсом 25 с выхода элемента И 6 и на. одни из входов блока сравнения 5.

С выхода регистра числа 4 записанный в первом цикле информационный код снимается на другие входы блока сравнения 5.

Во втором цикле работы устройства с выхода элемента И 8 импульсное напряжение 26 подается на вход дополнительного формирователя 7, который в четные циклы в дополнительном проводе 16, прощивающем все разрядные сердечники в направлении, соответствующем логическому нулю, формирует ток такой

полярности, что импульсное напряжение,считанных сигналов, формируемых с помощью основного формирователя 3, сдвигается в сторону логического нуля. При этом в тех разрядах, гДе прошивка выполнена в одно окно, т. е. с ошибкой, сигнал на входе усилителей считывания 15 будет соответствовать логическому нулю, тогда как в предыдущем цикле, без дополнительного кода, сигнал будет соответствовать логической «I. Считанный при этом во время прихода строба 23 с выходов удилнтелей 15 код, не изменяя записанной в первом цикле информации в регистре числа 4, поступает на одни из входов блока сравнения кодов 5. При появлении в элементе И 9 разрещающего импульса 26 на вход блока индикации 17, предварительно установленного испульсом 27

в «О с выхода элемента И 10, проходит сигнал сравнения 28 информационного кода, записанного в регистр числа 4, в первом цикле, С кодом, снятым с однополяриых усилителей 15 во втором цикле. Несравнение кодов высвечивается блоком индикации 17, что соответствует ошибке типа «прошивка в одно кно.

Таким образом описанное устройство позволяет существенно увеличить достоверность контроля и расширить область его применения.

Формула изобретения .

Устройство для контроля блоков памяти, содержащее источник управляющих импульсов, первый выход которого подключен ко входу формирователя опросного тока, регистр числа, входы которого соединены Со входами устройствами, а выходы - с одними входами блока

сравнения, блок индикации, ог/тчаюи ееея тем, что, с целью повышения достоверности контроля, оно содержит элементы И, дополнительный формирователь опросного тока и счетный триггер, один выход которого подключен к первому входу первого элемента И, а другой - к первым входам второго, третьего и четвертого элементов И, первый и второй выходы источника управляющих импульсов соединены соотвеТственно со вторыми входами второго и третьего элементов И, третий и четвертый выходы источника управляющих импульсов подключены соответственно ко вторым входам первого и четвертого элементов И и входу счетного триггера, выходы первого, второго и четвертого элементов И соединены соответственно с управляющим входом регистра уисла, входом

дополнительного формирователя опросного тока и одним из входов блока индикации, третий вход третьего элемента И подключен к выходу блока сравнення, другие входы которого соединены со входами устройства, а выход третьего элемента И подключен к другому входу блока индикации.

Источники инфоркам н., принятые во вни мание прн экспертизе:

1.Авторское свидетелье «о СССР № 273281 кл. G 11 С 11/00. 1969.

2.Авторское свндетельсгш СССР № 277858, кл. О 11 С 29/00, 1%9.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля блоковпАМяТи | 1979 |

|

SU801105A2 |

| Устройство для контроля монтажа | 1985 |

|

SU1352505A1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

| Устройство для централизованного контроля и оперативного управления | 1977 |

|

SU633029A1 |

| УНИВЕРСАЛЬНОЕ УСТРОЙСТВО КОДИРОВАНИЯ СИГНАЛОВ | 1993 |

|

RU2037270C1 |

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

| Сигнатурный анализатор | 1986 |

|

SU1386995A1 |

| Устройство для контроля памяти | 1983 |

|

SU1280459A1 |

| Преобразователь последовательного комбинированного кода в параллельный двоичный код | 1982 |

|

SU1078424A1 |

| Запоминающее устройство | 1985 |

|

SU1259336A2 |

а

TJ /т.

LI

1Г Г1

Л

Авторы

Даты

1978-05-15—Публикация

1976-12-29—Подача