(54) АСИНХРОННОЕ УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ДИСКРЕТНОЙ ИНФОРМАЦИИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для передачи и приема дискретных сигналов | 1978 |

|

SU766032A1 |

| Устройство для передачи и приема дискретной информации | 1977 |

|

SU690646A1 |

| Система передачи цифровой информации | 1987 |

|

SU1518911A1 |

| Устройство для приема избыточной информации | 1984 |

|

SU1167638A1 |

| Система передачи штриховых изображений с сегментным кодированием | 1980 |

|

SU944158A1 |

| СИСТЕМА СВЯЗИ | 2003 |

|

RU2249914C2 |

| Устройство передачи и приема команд согласования скоростей | 1989 |

|

SU1793553A1 |

| ЦЕНТРАЛЬНАЯ СТАНЦИЯ СИСТЕМЫ РАДИОСВЯЗИ С ПОДВИЖНЫМИ ОБЪЕКТАМИ | 2022 |

|

RU2780810C1 |

| СПОСОБ ПЕРЕДАЧИ ИНФОРМАЦИИ В СИСТЕМАХ СВЯЗИ С ШУМОПОДОБНЫМИ СИГНАЛАМИ И ПРОГРАММНЫЙ ПРОДУКТ | 2003 |

|

RU2277760C2 |

| ВОЛОКОННО-ОПТИЧЕСКАЯ СИСТЕМА С БЕЗОПАСНОЙ ПЕРЕДАЧЕЙ ИНФОРМАЦИИ | 1995 |

|

RU2100906C1 |

1

Изобретение относится к связи кг может использоваться в асинхронноадресных системах связи для передачи команд или сообщений.

Известно асинхронное устройство для передачи и приема дискретной информации 7 содержащее на передающе стороне кодер адреса, вход которого соединен с входом счетчика и первым входом первого элемента И, выход которого подключен к входу кодера информации, выход которого соединен с первым входом модулятора и входом элемента НЕ, выход которого подключен к первому входу второго элемента И, второй вход и выход которого соединены соответственно с вторьом входом первого элемента И и вторым входом модулятора, а также элемент или, на приемной стороне - последовательно соединенные пороговый блок декодер адреса, первый элемент И, счетчик и декодер информации, к второму входу которого подключен выход второго элемента И, входы которого соединены соответственно с первым выходом решающего блока и выходом декодера адреса, при этом второй вход первого элемента И является татовым входом l.

Однако известное устройство обладает малой скоростью передачи информации .

Цель изобретения - повышение скорости передачи информации.

Цель достигается тем, что в устройстве на передающей стороне выход счётчика подключен к первому входу элемента ИЛИ, второй вход и выход которого соединены соответственно с выходом кодера адреса и вторым входом первого элемента И, а на приемной стороне введены последовательно соединенные блок памяти и блок элементов И, второй вход и выход которого соединены соответственно с выходом декодера адреса и третьим входом декодера информации , причем к входу блока памяти подключен первый выход решающего блока, второй выход которого соединен с входом порогового блока.

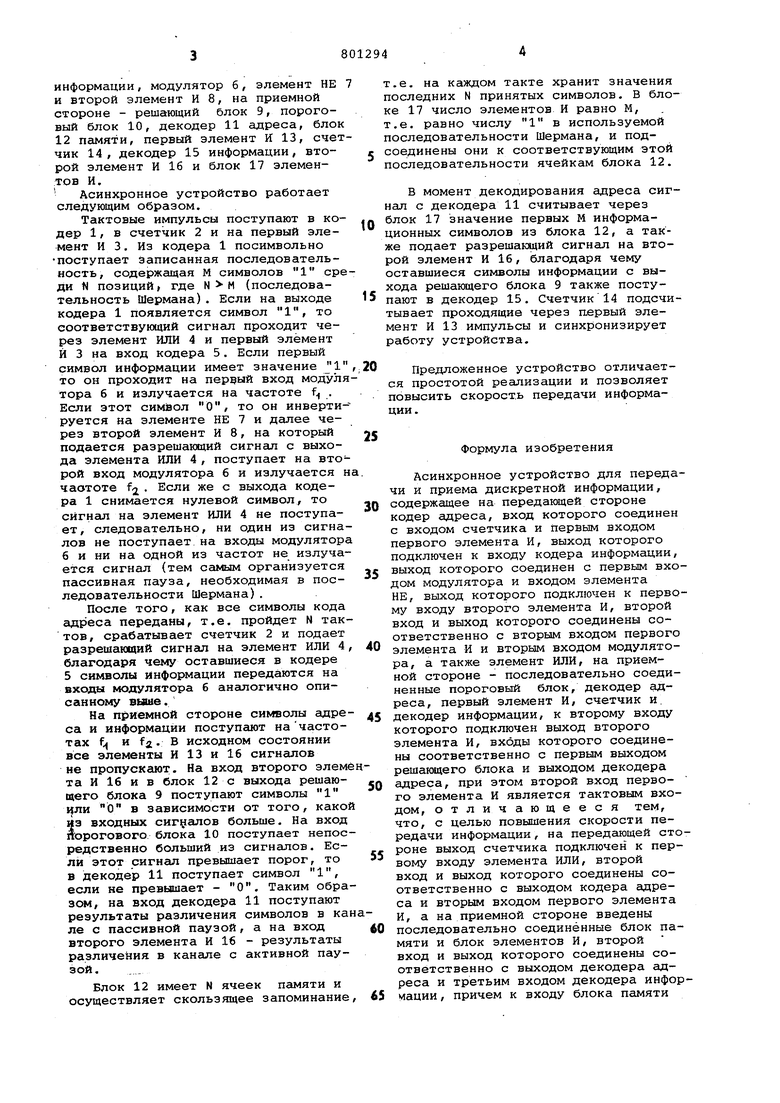

На чертеже приведена структурная электрическая схема предложенного устройства.

Асинхронное устройство для передачи и приема дискретной информации содержит на передающей стороне кодер 1 адреса, счетчик 2., первый элемент И 3, элемент ИЛИ 4 , кодер 5 информации, модулятор б, элемент НЕ и второй элемент И 8, на приемной стороне - решающий блок 9, пороговый блок 10, декодер 11 адреса, блок 12 памяти, первый элемент И 13, счет чик 14, декодер 15 информации, второй элемент и 16 и блок 17 элементов И, - Асинхронное устройство работает следующим образом. Тактовые импульсы поступают в ко дер 1, в счетчик 2 и на первый элемент И 3, Из кодера 1 посимвольно поступает записанная последовательность, содержащая М символов 1 ср ди N позиций где (последовательность Шермана). Если на выходе кодера 1 появляется символ 1, то соответствующий сигнал проходит через элемент ИЛИ 4 и первый элемент И 3 на вход кодера 5. Если первый символ информации имеет значение 1 то он проходит на первый вход модул тора 6 и излучается на частоте f . Если этот сим)аол О, то он инверти руется на элементе НЕ 7 и далее через второй элемент И 8, на который подается разрешающий сигнал с выхода элемента ИЛИ 4 , поступает на вто рой вход модулятора 6 и излучается частоте f. Если же с выхода кодера 1 снимается нулевой символ, то сигнал на элемент ИЛИ 4 не поступает, следовательно, ни один из сигна лов не поступает на входы модулятор 6 и ни на одной из частот не излуча ется сигнал (тем самым организуется пассивная пауза, необходимая в последовательности Шермана). После того, как все символы кода адреса переданы, т.е. пройдет N так тов, срабатывает счетчик 2 и подает разрешающий сигнал на элемент или 4 благодаря чему оставшиеся в кодере 5 символы Информации передаются на вхолы модулятора б аналогично описанному выше. На приемной стороне символы адре са и информации поступают начастотах f и f2. В исходном состоянии все элементы И 13 и 16 сигналов не пропускают. На вход второго элем та И 16 и в блок 12 с выхода решающего блока 9 поступают символы 1 или О в зависимости от того, како из входных сигналов больше. На вход порогового блока 10 поступает непос редственно больший из сигналов. Если этот сигнал превышает порог, то в декодер 11 поступает символ 1, если не превышает - О. Таким обра зом, на вход декодера 11 поступают результаты различения символов в ка ле с пассивной паузой, а на вход второго элемента И 16 - результаты различения в канале с активной паузой. Блок 12 имеет N ячеек памяти и осуществляет скользящее запоминание т.е. на каждом такте хранит значения последних N принятых символов. В блоке 17 число элементов И равно М, т.е. равно числу 1 в используемой последовательности Шермана, и подсоединены они к соответствующим этой последовательности ячейкам блока 12. В момент декодирования адреса сигнал с декодера 11 считывает через блок 17 значение первых М информационных символов из блока 12, а также подает разрешающий сигнал на второй элемент И 16, благодаря чему оставшиеся символы информации с выхода решающего блока 9 также поступают в декодер 15. Счетчик14 подсчитывает проходящие через первый элемент И 13 импульсы и синхронизирует работу устройства. Предложенное устройство отличается простотой реализации и позволяет повысить скорость передачи информации. Формула изобретения Асинхронное устройство для передачи и приема дискретной информации, содержащее на передающей стороне кодер адреса, вход которого соединен с входом счетчика и Первым входом первого элемента И, выход которого подключен к входу кодера информации, выход которого соединен с первым входом модулятора и входом элемента НЕ, выход которого подключен к первому входу второго элемента И, второй вход и выход которого соединены соответственно с вторым входом первого элемента И и вторым входом модулятора, а также элемент ИЛИ, на приемной стороне - последовательно соединенные пороговый блок, декодер адреса, первый элемент И, счетчик и. декодер информации, к второму входу которого подключен выход второго элемента И, входы которого соединены соответственно с первым выходом решающего блока и выходом декодера адреса, при этом второй вход первого элемента И является тактовым входом, отличающееся тем, что, с целью повьпяения скорости передачи информации, на передающей стороне выход счетчика подключен к первому входу элемента ИЛИ, второй вход и выход которого соединены соответственно с выходом кодера адреса и вторым входом первого элемента И, а на приемной стороне введены последовательно соединённые блок памяти и блок элементов И, второй вход и выход которого соединены соответственно с выходом декодера адреса и третьим входом декодера информации , причем к входу блока памяти

подключен первый выход решающего блока, второй выход которого соединен с входом порогового блока.

Источники информации, принятые во внимание при экспертизе

1, Исследование методов адаптации и слежения за состоянием канала связи в системах передачи информации с решающей обратной связью. Отчет 1 УД 4761, Л., 1976, с. 35-59 (прототип) .

Авторы

Даты

1981-01-30—Публикация

1978-03-01—Подача