Устройство относится к многоканальной электросвязи и может использоваться в устройствах временного объединения и разделения цифровых сигналов с двусторонним согласованием скоростей.

Известны устройства временного объединения и разделения цифровых сигналов с двусторонним согласованием скоростей, передающая часть которых содержит блоки асинхронного сопряжения (БАС пер) по числу источников поступающих цифровых сигналов и схему объединения, а приемная часть содержит схему разделения и блоки асинхронного сопряжения (БАС пр) по числу потребителей поступающих цифровых сигналов. В свою очередь, каждый БАС пер. содержит временной детектор, блок памяти, элемент добавления-вычитания и передатчик команд управления согласованием скорости, а каждый БАС пр. состоит из приемника команд управления согласования скорости, блока памяти и схемы фазовой автоподстройки частоты. Увеличение промежутка времени между моментами записи и считывания символа в блоке памяти БАС

пер. свыше периода частоты считывания обнаруживается временным детектором, после чего производится дополнительное считывание из блока памяти символа поступающего цифрового сигнала и его передача по отдельному каналу. Одновременно передатчик команд управления согласованием скорости.вырабатывает команду отрицательного (-1)управления согласованием скорости. Уменьшение промежутка времени между моментами записи и считывания символа в блоке памяти БАС пер. до нуля также обнаруживается временным детектором, после чего производится дополнительная запись в блок памяти согласующего символа, а передатчик команд управления согласованием скорости вырабатывает команду положительного (+1) управления согласованием скорости. Сформированные команды управления согласованием скорости передаются на приемник команд управления согласованием скорости передаются на гтриемник команд управления согласованием скорости соответствующего БАС пр. по специально выделенному в цикле (либо

XI

NQ

W

ел ел

Сл

сверхцикле) группового (объединенного) сигнала цифровому каналу. Поскольку промежуток времени между моментами передачи команд (+1) и (-1) зависит от разности частот опорных генераторов источника поступающего цифрового сигнала и устройства временного объединения и может изменяться, пропускная способность канала передачи команд управления согласованием скорости выбирается с учетом максимального значения модуля этой разности. В случае, когда в рассматриваемый момент не требуется передавать команды (+1) или (-1); в канале передачи команд управления согласованием скорости передаются пассивные команды (0), несущие информацию в том, что согласование скбро- сти выполнять не требуется. Защита команд от искажений производится помехоустойчивыми кодами. Приняв команду отрицательного (-.1) управления согласованием скорости, приемник команд управления согласованием скорости соответствующего БАС пр. с помощью схемы фазовойэвтопод- стройки частоты (ФАПЧ) увеличивает частоту считывания поступающего сигнала из блока памяти таким образом, чтобы произвести дополнительное считывание передан- ного по отдельному каналу дополнительного символа. Приняв команду положительного (+1) управления согласованием скорости, приемник команд управле-. н иясогласованием скорости соответствующего БАС пр. с помощью схемы ФАПЧ уменьшает частоту считывания поступающего сигнала из блока памяти таким образом, чтобы не произошло считывания согласующего символа из блока памяти.; Пассивные команды управлений согласованием скорости (0) приемник команд управления согласованием скорости БАС пр. не воспринимает.

Реализованная в известных устройствах передачи информации о знаке согласования скорости включает дискретизацию с частотой следования команд управления согласованием скорости разности фаз частот записи и считывания поступающего информационного сигнала из блока памяти, квантование дискретных отсчетов на три уровня (+1, О, -Т), кодирование уровня, передачу кода уровня как команды управления согласованием скорости, выполнение согласова- Тн йя ёШрсГстй, ШГгТ&1ШёнШ согласования скорости, после которого квантованный модуль разности фаз частот записи и считывания не превышает уровней (+1) и (-1), э прием информации о знаке согласования скорости включает прием команды управления согласованием скорости, декодирова0

5

0

5

0

5

0

5

0

5

ние кода уровня, восстановление квантованного уровня разности фаз частот записи и считывания поступающего информационного сигнала из блока памяти, выполнения согласования скорости, при котором восстанавливается соответствие частоты считывания поступающего информационного сигнала на стороне; приема частоте записи этого сигнала на стороне передачи.

Недостатком известных устройств является низкая помехозащищенность, т. к. при искажении команды управления двусторонним согласованием скорости (кода уровня) в тракте приема соответствие частоты считывания поступающего сигнала из блока памяти приемной части частоте записи поступающего сигнала в блок памяти передачей части нарушается и в поступающем информационном сигнале возникает проскальзывание.

Наиболее близким к предлагаемому устройству передачи и приема информации о знаке согласования скорости, принимаемым за прототип, является устройство, в котором с целью повышения помехозащищенности производится дополнительная передача информации о знаке выполненного согласования скорости с высокой частотой. /- ;. . .,..;,. .. .

Недостатком прототипа является низкая защищенность информации о знаке со- гласовдния скорости от перерывов в тракте приема (периедов времени, в течение которых вероятность сбоя символа в тракте приема значительно возрастает) более длительных, чем промежуток времени между двумя подряд следующими согласованиями скорости одного знака, ведущих к невыполнению согласования скорости- поступающего сигнала в приемной части и появление.в нем проскальзывания.

Цель изобретения - повышение защищенности информации о знаке согласования скорости от перерывов в тракте приема.

Цель изобретения достигается тем, что разность фаз сигналов записи и считывания поступающего цифрового сигнала из блока памяти квантуется на три уровня (-1, 0, +1), диСкретизируется с определенной частотой, после чего код уровня складывается с суммой по определенному модулю всех предыдущих кодов уровня. Полученная сумма кодируется и передается как команда управления согласованием скорости, затем выполняется согласование скорости. На стороне приема команда управления согласованием скорости принимается, декодируется, после чего, при отсутствии сигнала о перерыве в тракте во время приема рассматриваемой и предшествующей команд,

из полученной суммы вычитается по определенному модулю сумма, полученная при декодировании предшествующей команды. Если модуль этой разности превышает единицу, полученные разности и сумма стираются, если же модуль этой разности не превышает единицу, сумма запоминается, далее последовательно восстанавливаются код уровня дискретизированной разности фаз сигналов записи и считывания, разность фаз, сигнал считывания поступающего цифрового сигнала из блока памяти и выполняется согласование скорости. При перерыве же в тракте во время приема предшествующей команды и отсутствии сигнала перерыва в тракте во время приема рассматриваемой команды из полученной суммы вычитается по определенному модулю сумма, полученная при декодировании последней команды, правильно принятая до возникновения перерыва в тракте приема, определяется знак разности, приписывается единице, последовательно восстанавливаются код уровня дискретизированной разности фаз сигналов записи и считывания, разность фаз, сигнал считывания посту- пающего цифрового сигнала из блока памяти и выполняется согласование скорости столько раз, каково значение полученной разности сумм. При появлении сигнала перерыва в тракте во время приема рассматриваемой команды полученная сумма стирается и сохраняется сумма, полученная при декодировании последней правильно принятой команды. Технико-экономическая эффективность предлагаемого устройства передачи и приема команд согласования скоростей заключается в том, что первая же правильно принятая после перерыва в тракте приема команда управления согласованием скорости позволяет исправить проскальзывание, появившееся в цифровом сигнале источника из-заневыполнения согласования его скорости в блоке асинхронного сопряжения во время перерыва. Это предотвращает истинный сбой циклового синхронизма . в аппаратуре временного разделения нижней ступени иерархии, ведущей к размножению Ошибок в цифровых каналах.

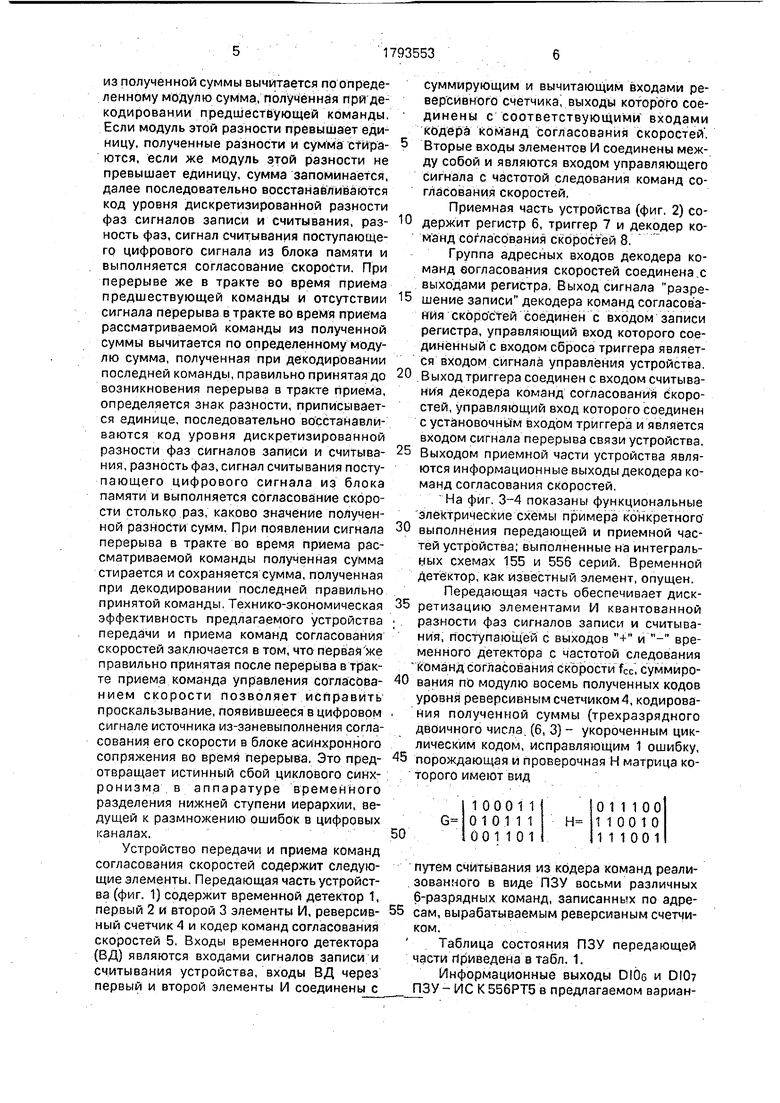

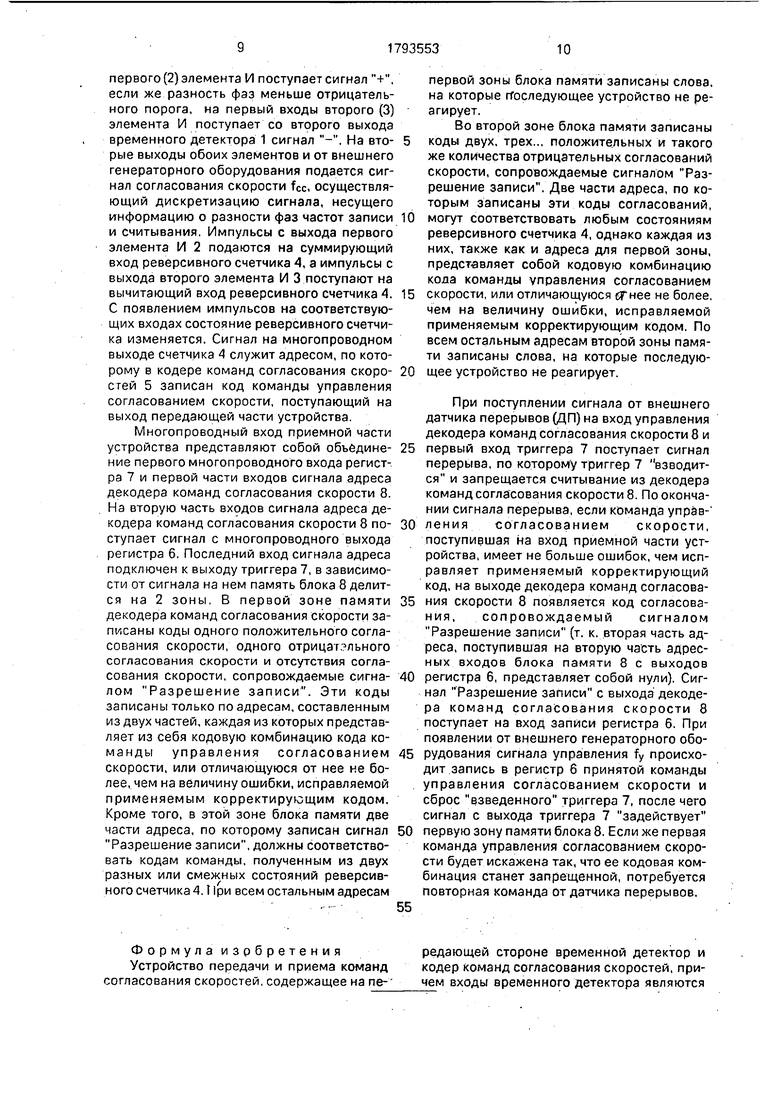

Устройство передачи и приема команд согласования скоростей содержит следующие элементы. Передающая часть устройства (фиг. 1) содержит временной детектор 1, первый 2 и второй 3 элементы И, реверсивный счетчик 4 и кодер команд согласования скоростей 5. Входы временного детектора (ВД) являются входами сигналов записи и считывания устройства, входы ВД через первый и второй элементы I/I соединены с

суммирующим и вычитающим входами ре- вер сйвного счётчика выходы которого соединены с соответствующими входами кодера команд согласования скоростей .

Вторые входы элементов И соединены между собой и являются входом управляющего сигнала с частотой следования команд согласования скоростей.

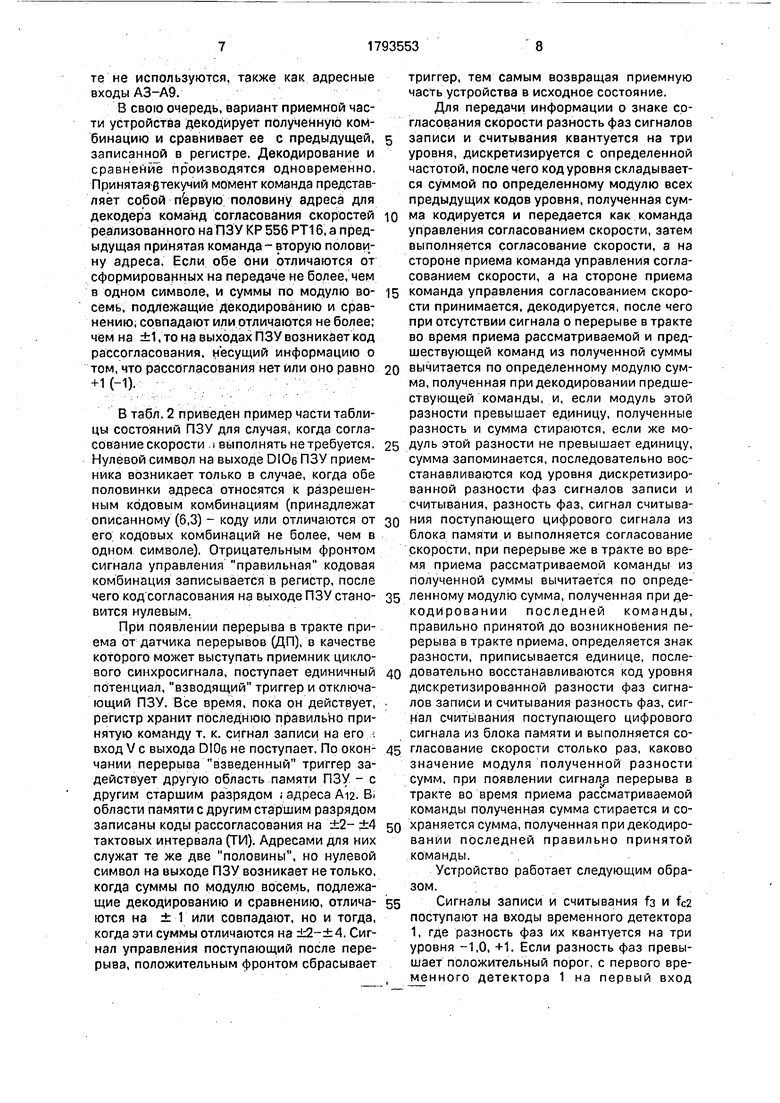

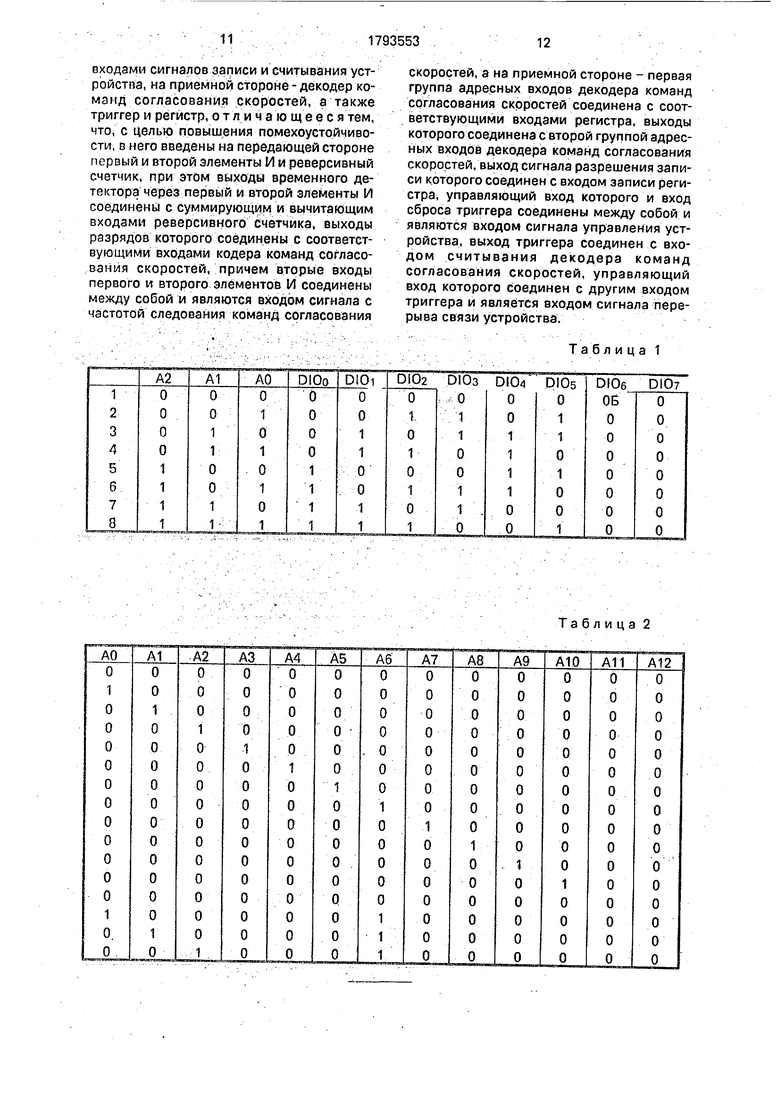

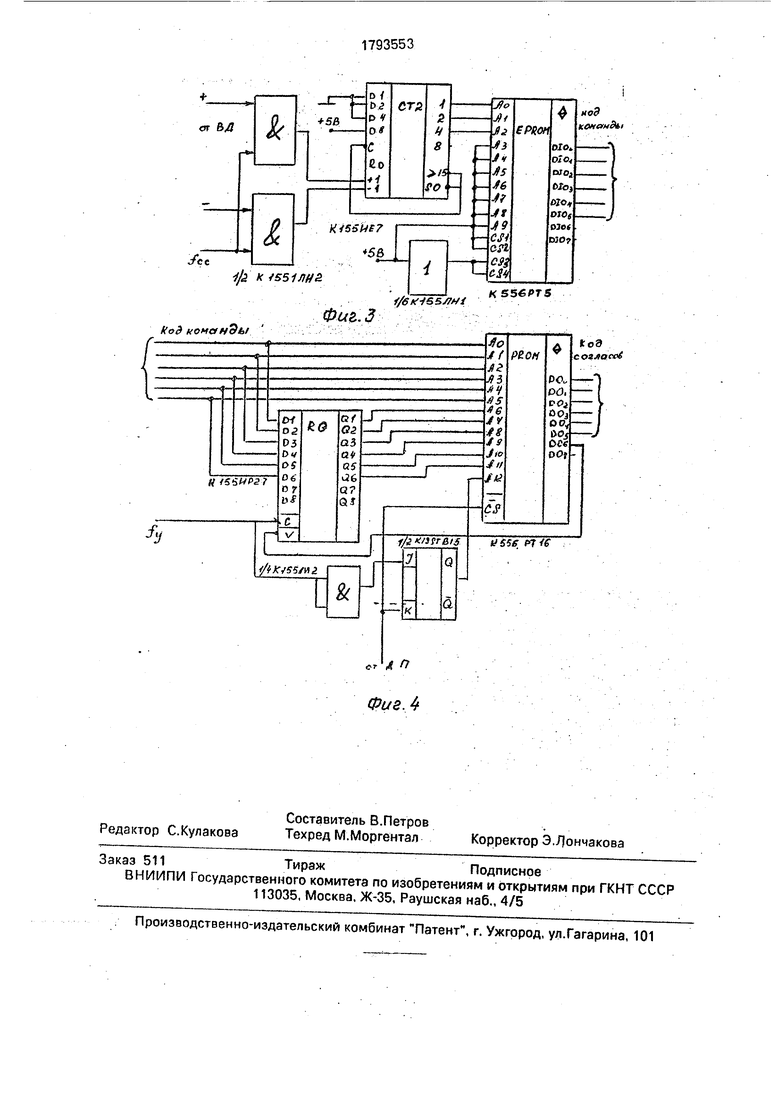

Приемная часть устройства (фиг. 2) содержит регистр 6, триггер 7 и декодер команд согласования скоростей 8.

Группа адресных входов декодера команд еогласования скоростей соединена.с выходами регистра. Выход сигнала разрешение записи декодера команд согласования скЬро Стёй соединен с входом записи регистра, управляющий вход которого соединённый с входом сброса триггера является входом сигнала управления устройства.

Выход триггера соединен с входом считывания декодера команд согласования скоростей, управляющий вход которого соединен с установочным входом триггера и является входом сигнала перерыва связи устройства.

Выходом приемной части устройства являются информационные выходы декодера команд согласования скоростей.

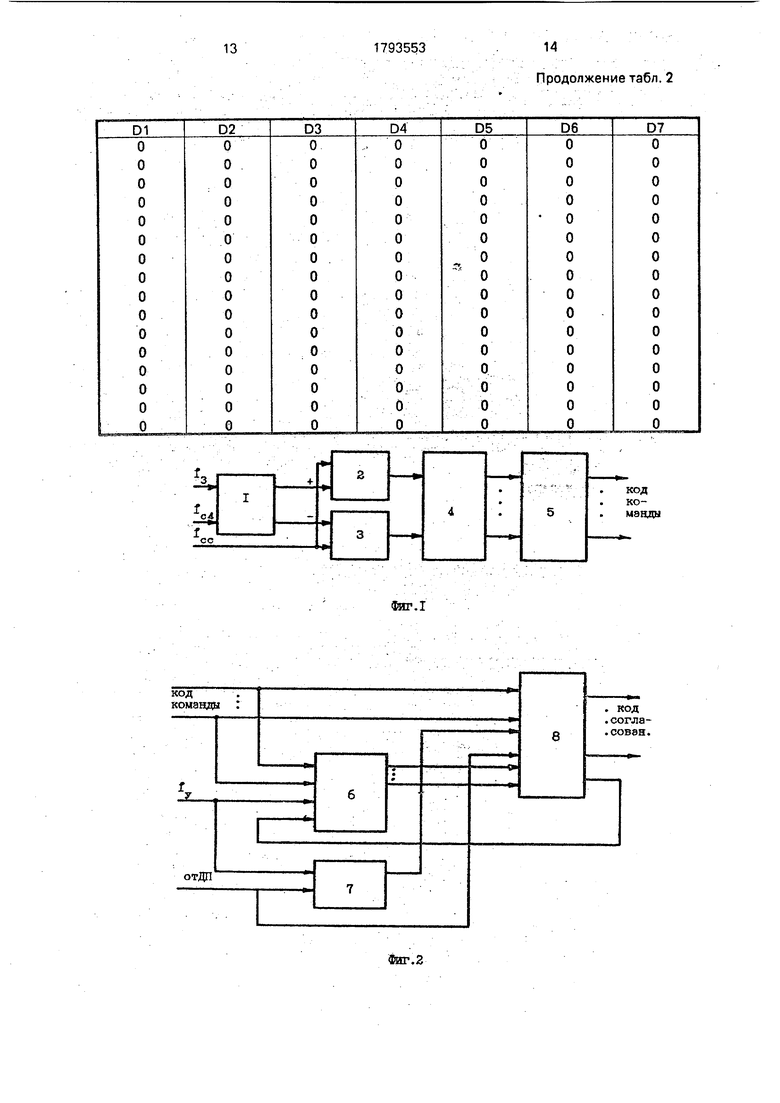

На фиг. 3-4 показаны функциональные электрические схемы примера конкретного

выполнения передающей и приемной частей устройства; выполненные на интегральных схемах 155 и 556 серий. Временной детектор, как известный элемент, опущен. Передающая часть обеспечивает дискретизацию элементами И квантованной

разности фаз сигналов записи и считывания, поступающей с выходов + и - временного детектора с частотой следования команд согласования скорости сс, суммирования по модулю восемь полученных кодов уровня реверсивным счетчиком 4, кодирования полученной суммы (трехразрядного двоичного числа, (6, 3} - укороченным циклическим кодом, исправляющим 1 ошибку,

порождающая и проверочная Н матрица которого имеют вид

G

100011

010111

001101

Н

011100

110010

111001

путем считывания из кодера команд реали- . зеванного в виде ПЗУ восьми различных (5-разрядных команд, записанных по адре- 55 сам, вырабатываемым реверсивным счетчиком.

Таблица состояния ПЗУ передающей части приведена в табл. 1.

Информационные выходы ОЮб и DIO ПЗУ - НС К 556РТ5 в предлагаемом варианте не используются, также как адресные входы АЗ-А9.

В свою очередь, вариант приемной части устройства декодирует полученную комбинацию и сравнивает ее с предыдущей, записанной в регистре. Декодирование и сравнение производятся одновременно. Принятая б текучий момент команда представляет собой первую половину адреса для декодера команд согласования скоростей реализованного на ПЗУ КР 556 РТ16, а предыдущая принятая команда- вторую половину адреса. Если обе они отличаются от сформированных на передаче не более, чем в одном символе, и суммы по модулю восемь, подлежащие декодированию и сравнению, совпадают или отличаются не более; чем на ±1, то на выходах ПЗУ возникает код рассогласования, несущий информацию о том, что рассогласования нет или оно равно +4-1).

В табл. 2 приведен пример части таблицы состояний ПЗУ для случая, когда согласование скорости .1 выполнять не требуется, Нулевой символ на выходе DlOe ПЗУ приемника возникает только в случае, когда обе половинки адреса относятся к разрешенным кодовым комбинациям (принадлежат описанному (6,3) - коду или отличаются от его; кодовых комбинаций не более, чем в одном символе). Отрицательным фронтом сигнала управления правильная кодовая комбинация записывается в регистр, после чего код согласования на выходе ПЗУ становится нулевым,

При появлении перерыва в тракте приема от датчика перерывов (ДП), в качестве которого может выступать приемник циклового синхросигнала, поступает единичный потенциал, взводящий триггер и отключающий ПЗУ. Все время, пока он действует, регистр хранит последнюю правильно принятую команду т. к. сигнал записи на его : вход V с выхода DIOs не поступает. По окончании перерыва взведенный триггер задействует другую область памяти ПЗУ - с другим старшим разрядом ; адреса Ai2. В; области памяти с другим старшим разрядом записаны коды рассогласования на ±2- ±4 тактовых интервала (ТИ). Адресами для них служат те же две половины, но нулевой символ на выходе ПЗУ возникает не только, когда суммы по модулю восемь, подлежащие декодированию и сравнению, отличаются на ± 1 или совпадают, но и тогда, когда эти суммы отличаются на ±2-±4. Сигнал управления поступающий после перерыва, положительным фронтом сбрасывает

триггер, тем самым возвращая приемную часть устройства в исходное состояние.

Для передачи информации о знаке согласования скорости разность фаз сигналов

записи и считывания квантуется на три уровня, дискретизируется с определенной частотой, после чего код уровня складывается суммой по определенному модулю всех предыдущих кодов уровня, полученная сумма кодируется и передается как команда управления согласованием скорости, затем выполняется согласование скорости, а на стороне приема команда управления согласованием скорости, а на стороне приема

5 команда управления согласованием скорости принимается, декодируется, после чего при отсутствии сигнала о перерыве в тракте во время приема рассматриваемой и предшествующей команд из полученной суммы

0 вычитается по определенному модулю сумма, полученная при декодировании предшествующей команды, и, если модуль этой разности превышает единицу, полученные разность и сумма стираются, если же мр5 дуль этой разности не превышает единицу, сумма запоминается, последовательно восстанавливаются код уровня дискретизиро- ванной разности фаз сигналов записи и считывания, разность фаз, сигнал считыва0 ния поступающего цифрового сигнала из блока памяти и выполняется согласование скорости, при перерыве же в тракте во время приема рассматриваемой команды из полученной суммы вычитается по опреде5 ленному модулю сумма, полученная при де- кодировании последней команды, правильно принятой до возникновения перерыва в тракте приема, определяется знак разности, приписывается единице, после0 довательно восстанавливаются код уровня дискретизированной разности фаз сигналов записи и считывания разность фаз, сигнал считывания поступающего цифрового сигнала из блока памяти и выполняется со5 гласование скорости столько раз, каково значение модуля полученной разности сумм, при появлении сигналу перерыва в тракте во время приема рассматриваемой команды полученная сумма стирается и со0 храняется сумма, полученная при декодировании последней правильно принятой ; команды.

Устройство работает следующим образом.

5 Сигналы записи и считывания fa и fc2 поступают на входы временного детектора 1, где разность фаз их квантуется на три уровня -1,0, +1. Если разность фаз превышает положительный порог, с первого временного детектора 1 на первый вход

первого (2) элемента И поступает сигнал +, если же разность фаз меньше отрицательного порога, на первый входы второго (3) элемента И поступает со второго выхода временного детектора 1 сигнал -. На вто- рые выходы обоих элементов и от внешнего генераторного оборудования подается сигнал согласования скорости fee, осуществляющий дискретизацию сигнала, несущего информацию о разности фаз частот записи и считывания. Импульсы с выхода первого элемента И 2 подаются на суммирующий вход реверсивного счетчика 4, а импульсы с выхода второго элемента И 3 поступают на вычитающий вход реверсивного счетчика 4. С появлением импульсов на соответствующих входах состояние реверсивного счетчика изменяется. Сигнал на многопроводном выходе счетчика 4 служит адресом, по которому в кодере команд согласования скоро- стей 5 записан код команды управления согласованием скорости, поступающий на выход передающей части устройства.

Многопроводный вход приемной части устройства представляют собой объедине- ние первого многопроводного входа регистра 7 и первой части входов сигнала адреса декодера команд согласования скорости 8. На вторую часть входов сигнала адреса декодера команд согласования скорости 8 по- ступает сигнал с многопроводного выхода регистра 6. Последний вход сигнала адреса подключен к выходу триггера 7, в зависимости от сигнала на нем память блока 8 делится на 2 зоны. В первой зоне памяти декодера команд согласования скорости записаны коды одного положительного согласования скорости, одного отрицательного согласования скорости и отсутствия согласования скорости, сопровождаемые сигна- лом Разрешение записи. Эти коды записаны только по адресам, составленным из двух частей, каждая из которых представляет из себя кодовую комбинацию кода ко- манды управления согласованием скорости, или отличающуюся от нее не более, чем на величину ошибки, исправляемой применяемым корректирующим кодом. Кроме того, в этой зоне блока памяти две части адреса, по которому записан сигнал Разрешение записи, должны соответствовать кодам команды, полученным из двух разных или смежных состояний реверсивного счетчика 4.1 ри всем остальным адресам

первой зоны блока памяти записаны слова, на которые последующее устройство не реагирует.

Во второй зоне блока памяти записаны коды двух, трех.., положительных и такого же количества отрицательных согласований скорости, сопровождаемые сигналом Разрешение записи. Две части адреса, по которым записаны эти коды согласований, могут соответствовать любым состояниям реверсивного счетчика 4, однако каждая из них, также как и адреса для первой зоны, представляет собой кодовую комбинацию кола команды управления согласованием скорости, или отличающуюся сгнее не более, чем на величину ошибки, исправляемой применяемым корректирующим кодом. По всем остальным адресам второй зоны памяти записаны слова, на которые последующее устройство не реагирует.

При поступлении сигнала от внешнего датчика перерывов (ДП) на вход управления декодера команд согласования скорости 8 и первый вход триггера 7 поступает сигнал перерыва, по которому триггер 7 взводится и запрещается считывание из декодера команд согласования скорости 8. По окончании сигнала перерыва, если команда управ- ления согласованием скорости, поступившая на вход приемной части устройства, имеет не больше ошибок, чем исправляет применяемый корректирующий код, на выходе декодера команд согласования скорости 8 появляется код согласования, сопровождаемый сигналом Разрешение записи (т. к. вторая часть адреса, поступившая на вторую часть адресных входов блока памяти 8 с выходов регистра 6, представляет собой нули). Сигнал Разрешение записи с выхода декодера команд согласования скорости 8 поступает на вход записи регистра 6. При появлении от внешнего генераторного оборудования сигнала управления fy происходит .запись в регистр 6 принятой команды управления согласованием скорости и сброс взведенного триггера 7, после чего сигнал с выхода триггера 7 задействует первую зону памяти блока 8. Если же первая команда управления согласованием скорости будет искажена так, что ее кодовая комбинация станет запрещенной, потребуется повторная команда отдатчика перерывов.

| название | год | авторы | номер документа |

|---|---|---|---|

| СИНХРОННЫЙ АДАПТИВНЫЙ МУЛЬТИПЛЕКСОР | 1993 |

|

RU2078401C1 |

| Устройство сопряжения асинхронных разноскоростных цифровых сигналов | 1990 |

|

SU1755386A1 |

| Устройство для передачи и приема информации | 1988 |

|

SU1684799A1 |

| УСТРОЙСТВО СОПРЯЖЕНИЯ АСИНХРОННЫХ РАЗНОСКОРОСТНЫХ ДИСКРЕТНЫХ СИГНАЛОВ | 1991 |

|

RU2014737C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ НЕСАНКЦИОНИРОВАННОГО ДОСТУПА | 2002 |

|

RU2221270C2 |

| УСТРОЙСТВО ВРЕМЕННОГО ГРУППООБРАЗОВАНИЯ | 2006 |

|

RU2306674C1 |

| УСТРОЙСТВО ДЛЯ ЦИФРОВОЙ МАГНИТНОЙ ЗАПИСИ ИНФОРМАЦИИ НА ВИДЕОМАГНИТОФОНЕ | 1993 |

|

RU2042218C1 |

| Устройство для обмена информацией | 1987 |

|

SU1497619A1 |

| РАДИОЛИНИЯ С ПРОГРАММНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 2004 |

|

RU2273099C1 |

| Устройство для сопряжения ЭВМ с каналом связи | 1988 |

|

SU1656544A1 |

Использование: многоканальная электросвязь в устройствах временного объединения разделения цифровых сигналов с двусторонним согласованием скоростей. Сущность изобретения: устройство передачи и приема команд согласования скоростей содержит на передающей стороне временной детектор, первый и второй элементы И, реверсивный счетчик и кодер команд согласования скоростей, а на приемной стороне - регистр, триггер и декодер команд согласования скоростей. Устройство обеспечивает повышение помехоустойчивости. 4 ил., 2 табл.

Формулаизрбретения Устройство передачи и приема команд согласования скоростей, содержащее на пе-

редающей стороне временной детектор и кодер команд согласования скоростей, причем входы временного детектора являются

входами сигналов записи и считывания устройства, на приемной стороне - декодер команд согласования скоростей, а также триггер и регистр, от л и чаю щ е ее я тем, что, с целью повышения помехоустойчивости, в него введены на передающей стороне первый и второй элементы И и реверсивный счетчик, при этим выходы временного детектора через первый и второй элементы И соединены с суммирующим и вычитающим входами реверсивного. счетчика, выходы разрядов которого соединены с соответствующими входами кодера команд согласования скоростей, причем вторые входы первого и второго элементов И соединены между собой и являются входом сигнала с частотой следования команд согласования

скоростей, а на приемной стороне - первая группа адресных входов декодера команд согласования скоростей соединена с соответствующими входами регистра, выходы которого соединена с второй группой адресных входов декодера команд согласования скоростей, выход сигнала разрешения записи которого соединен с входом записи регистра, управляющий вход которого и вход сброса триггера соединены между собой и являются входом сигнала управления устройства, выход триггера соединен с входом считывания декодера команд согласования скоростей, управляющий вход которого соединен с другим входом триггера и является входом сигнала перерыва связи устройства.

Та б л и ц а 1

Таблица 2

код команды

Продолжение табл. 2

8

. код .согла- .сован.

Фиг. 4

| Система для асинхронного сопряжения импульсных потоков | 1986 |

|

SU1420670A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1993-02-07—Публикация

1989-02-03—Подача