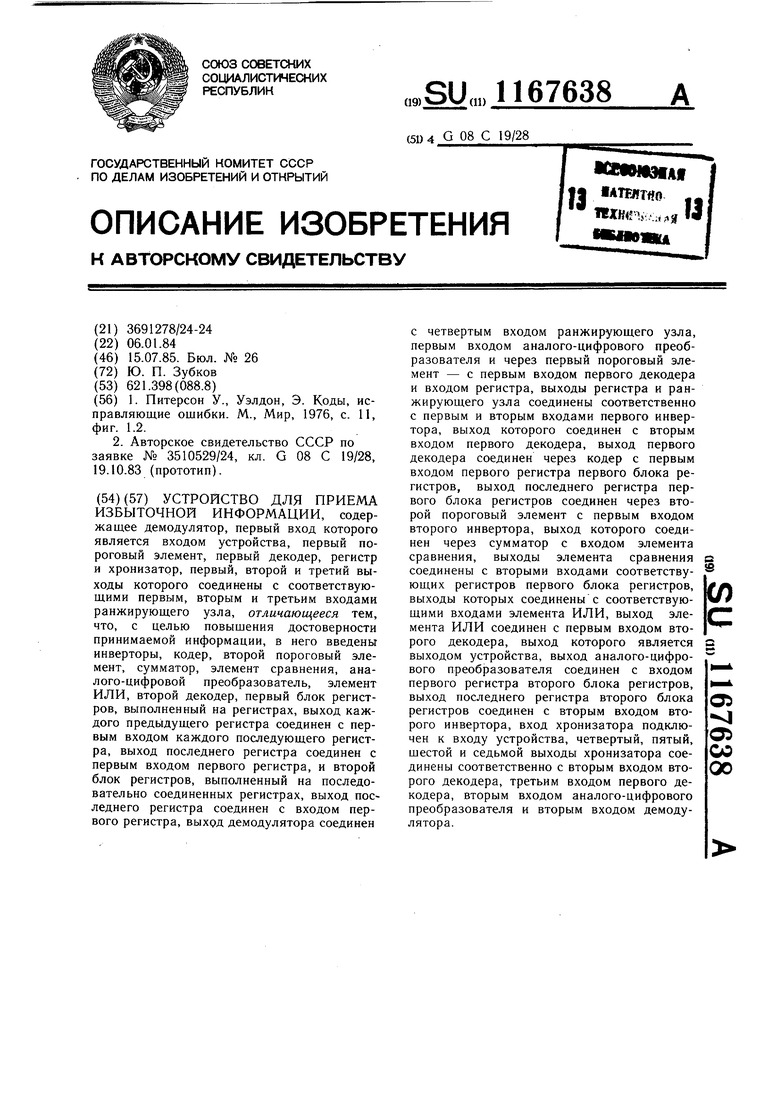

Изобретение относится к электросвязи и может быть использовано в системах передачи информации, использующих составные сигналы с избыточностью, формируемые на основе длинных и сверхдлинных помехоустойчивых кодов. Известно устройство для передачи и избыточной информации, содержащее аналого-цифровой преобразователь, кодер, модулятор, канал связи, демодулятор, декодер -и цифроаналоговый преобразователь 1. Недостатком известного устройства является низкая достоверность принимаемой информации, поскольку при декодировании сообщений в декодере не используется информация об амплитуде элементарных аналоговых сигналов. Наиболее близким по технической сущности к предлагаемому является устройство для приема избыточной информации, содержащее демодулятор, вход которого яв ляется входом устройства, выход демодулятора соединен с первым входом первого блока памяти, выход которого соединен с первым входом ранжирующего узла и через пороговый элемент с входом первого счетчика, первый и второй выходы первого счетчика соединены соответственно с первым входом генератора импульсов и с входом первого регистра, выходы первого регистра соединены с соответствующими первыми входами второго регистра, выход которого соединен с первым входом третьего регистра, выход третьего регистра соединен с первым входом первого ключа и входом декодера, выход декодера соединен с первым входом второго счетчика и вторыми входами первого ключа, генератора импульсов и первого блока памяти, выход первого ключа является выходом устройства, выход генератора импульсов соединен с входом третьего счетчика, первый и второй выходы которого соединены соответственно с первым входом второго блока памяти и вторым входом второго счетчика, первый и второй выходы второго блока памяти соединены с первыми входами соответственно второго ключа и четвертого счетчика, выходы второго и четвертого счетчиков соединены соответственно с первым и вторым входами блока сравнения, выход которого соединен с первым входом третьего блока памяти и вторыми входами второго блока памяти и второго ключа, хронизатор, первый, второй и третий выходы которого соединены с соответствующими вторым, третьим и четвертым входами ранжирующего узла, выход ранжирующего узла соединен с вторым входом третьего блока памяти, выходы третьего блока памяти и второго клю ча соединены соответственно с первым и вторым входами коммутатора, выход коммутатора соединен с входами элементов сравнения, первые входы которых соедине18 ны с соответствующими вторыми входами третьего регистра, вторые выходы элементов сравнения соединены с соответствующими входами элемента И, выход которого соединен с вторым входом второго регистра 2. В этом устройстве используется апостериорная информация об амплитуде элементарных сигналов, однако использование этой информации производится недостаточно полно, что снижает достоверность принимаемой информации. Цель изобретения - повышение достоверности принимаемой информации. Указанная цель достигается тем, что в устройство для приема избыточных сигналов, содержащее демодулятор, первый вход которого является входом устройства, первый пороговый элемент, первый декодер, регистр и хронизатор, первый, второй и третий выходы которого соединены с соответствующими первым, вторым и третьим входами ранжирующего узла, введены инверторы, кодер, второй пороговый элемент, сумматор, элемент, сравнения, аналого-цифровой преобразователь, элемент ИЛИ, второй декодер, первый блок регистров, выполненный на регистрах, выход каждого предыдущего регистра соединен с первым входом каждого последующего регистра, выход последнего регистра соединен с первым входом первого регистра, и второй блок регистров, выполненный на последовательно соединенных регистрах, выход последнего регистра соединен с входом первого регистра, выход демодулятора соединен с четвертьш входом ранжирующего узла, первым входом аналого-цифрового преобразователя и через первый пороговый элемент - с первым входом первого декодера, и входом регистра, выходы регистра ранжирующего узла соединены соответственно с первым и вторым входами первого инвертора, выход которого соединен с вторым входом первого декодера, выход первого декодера соединен через кодер с первым входом первого регистра первого блока регистров, выход последнего регистра первого блока регистров соединен через второй пороговый элемент с первым входом второго инвертора, выход которого соединен через сумматор с входом элемента сравнения, выходы элемента сравнения соединены с вторыми входами соответствующих регистров первого блока регистров, выходы которых соединены с соответствующими входами элемента ИЛИ, выход элемента ИЛИ соединен с первым входом второго декодера, выход которого является выходом устройства, выход аналого-цифрового преобразователя соединен с входом первого регистра второго блока регистров, выход последнего регистра второго блока регистров соединен с вторым входом второго инвертора, вход хронизатора подключен к входу устройства, четвертый, пятый, шестой и седьмой выходы хронизатора соединены соответственно с вторым входом второго декодера, третьим входом первого декодера, вторым входом аналогоцифрового преобразователя и вторым входом демодулетяора.

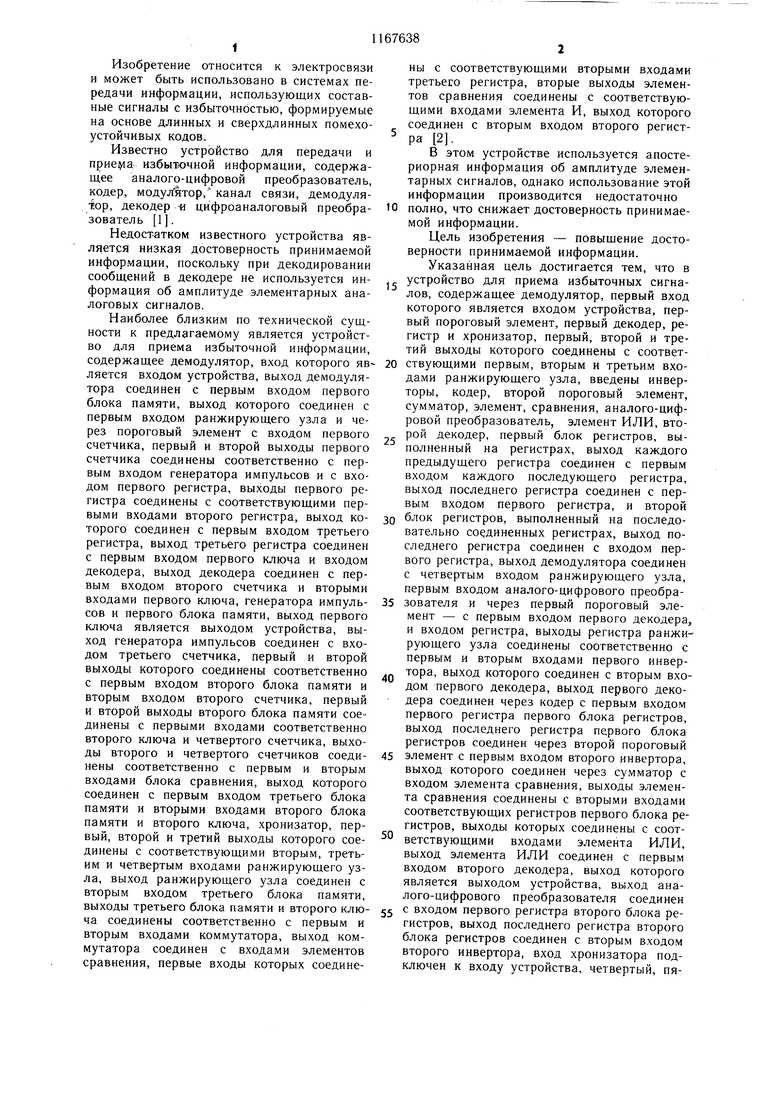

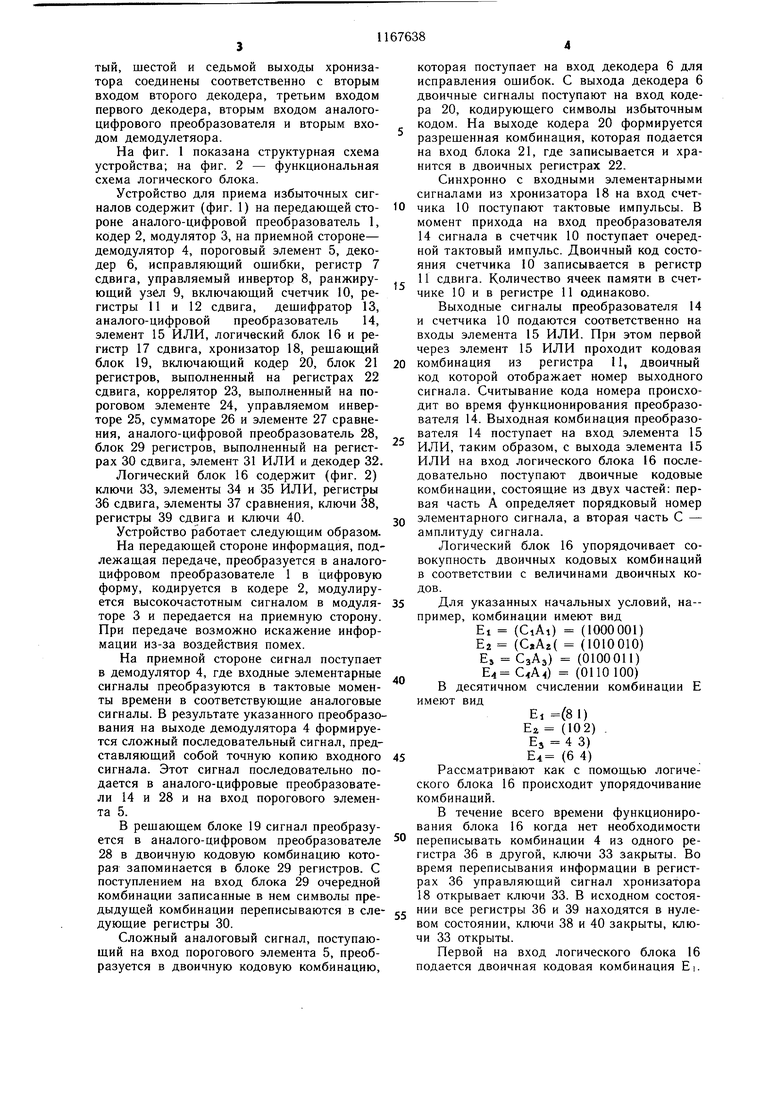

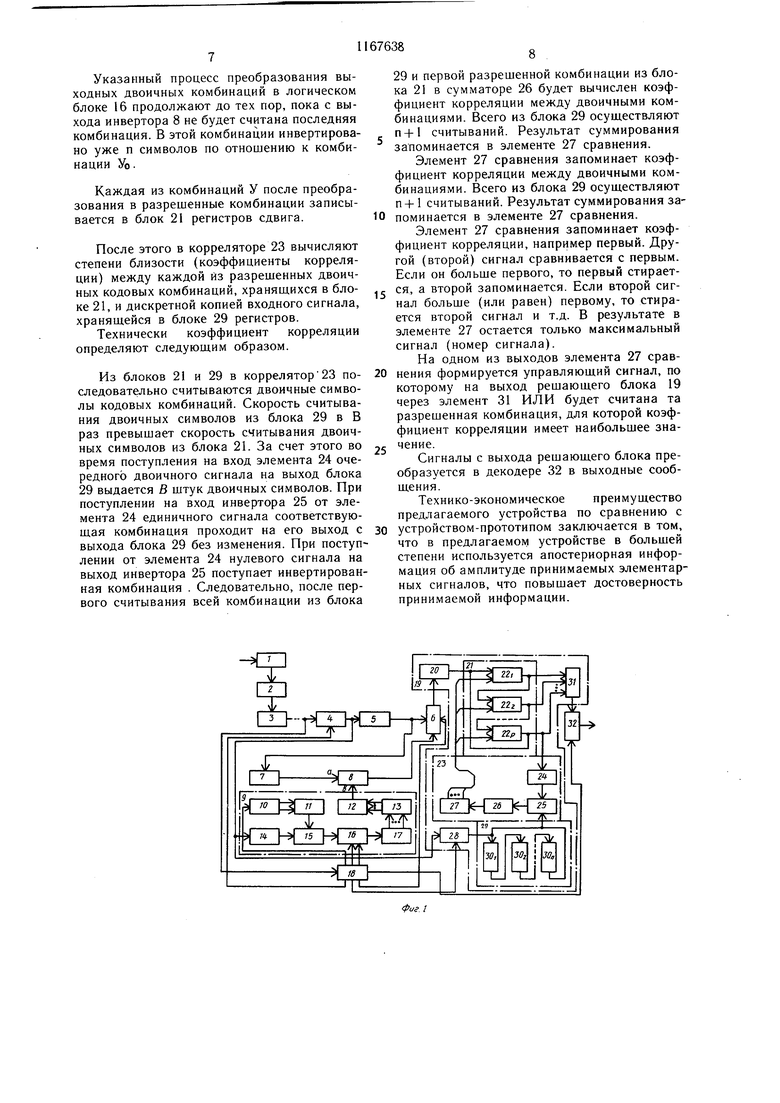

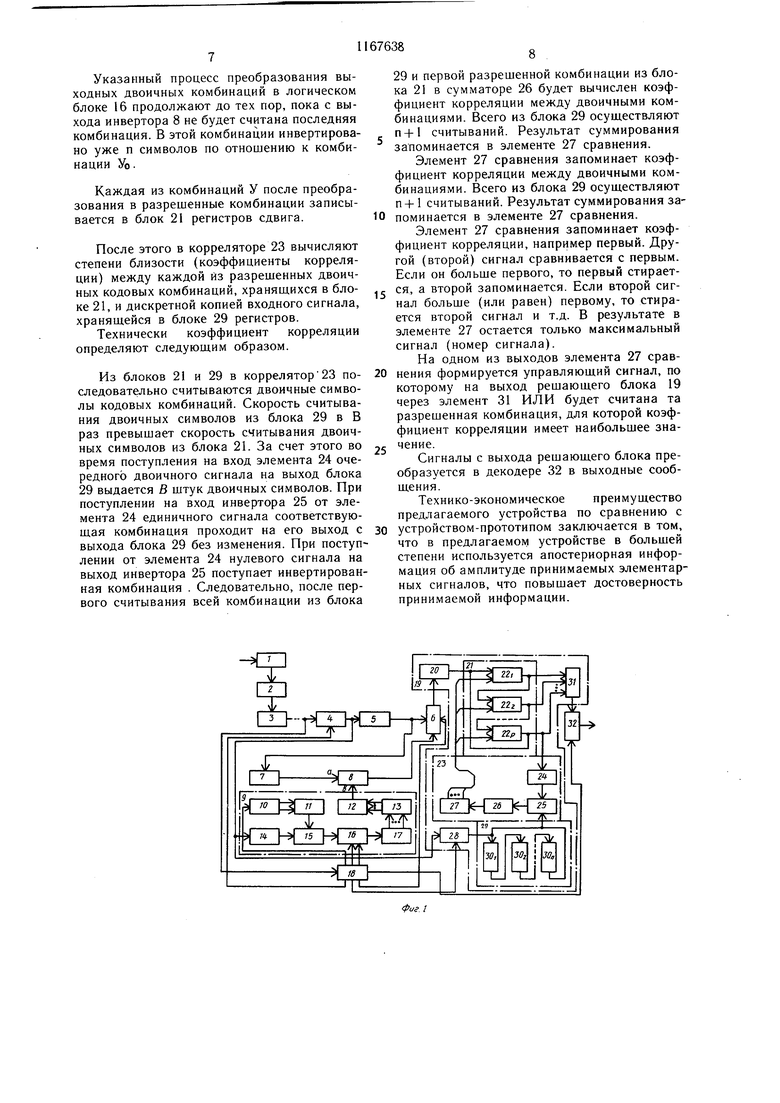

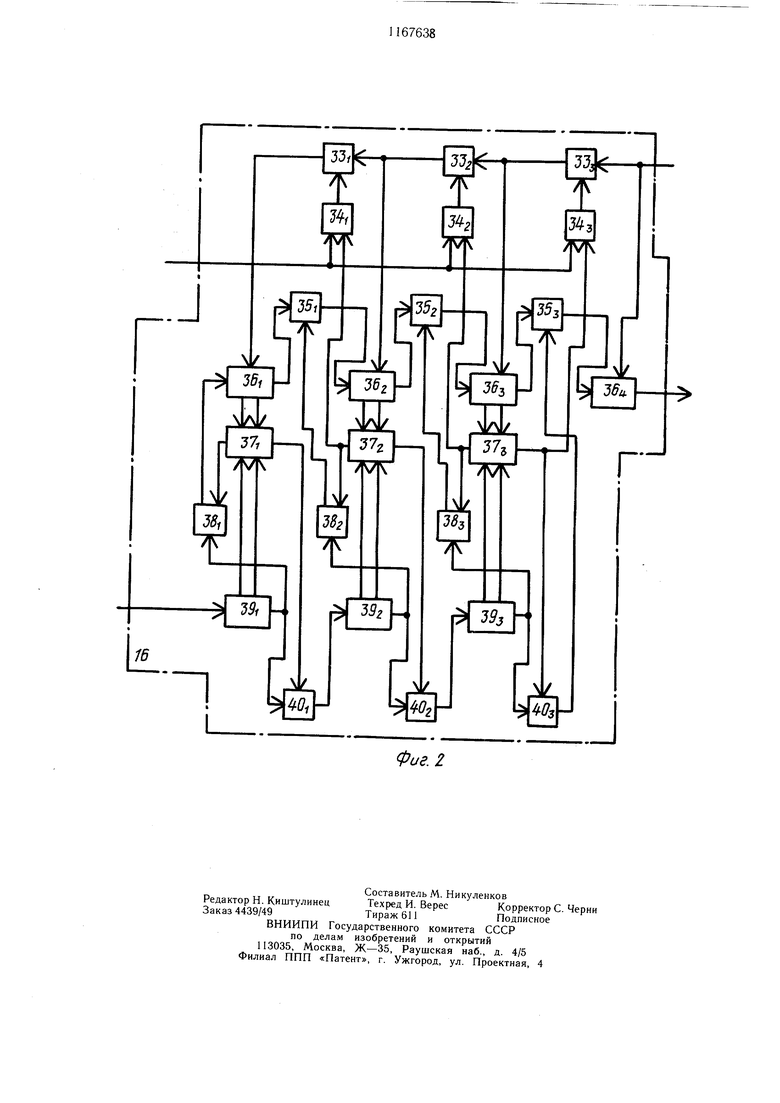

На фиг. 1 показана структурная схема устройства; на фиг. 2 - функциональная схема логического блока.

Устройство для приема избыточных сигналов содержит (фиг. 1) на передающей стороне аналого-цифровой преобразователь 1, кодер 2, модулятор 3, на приемной стороне- демодулятор 4, пороговый элемент 5, декодер 6, исправляющий ощибки, регистр 7 сдвига, управляемый инвертор 8, ранжирующий узел 9, включающий счетчик 10, регистры 11 и 12 сдвига, дещифратор 13, аналого-цифровой преобразователь 14, элемент 15 ИЛИ, логический блок 16 и регистр 17 сдвига, хронизатор 18, решающий блок 19, включающий кодер 20, блок 21 регистров, выполненный на регистрах 22 сдвига, коррелятор 23, выполненный на пороговом элементе 24, управляемом инверторе 25, сумматоре 26 и элементе 27 сравнения, аналого-цифровой преобразователь 28, блок 29 регистров, выполненный на регистрах 30 сдвига, элемент 31 ИЛИ и декодер 32.

Логический блок 16 содержит (фиг. 2) ключи 33, элементы 34 и 35 ИЛИ, регистры 36 сдвига, элементы 37 сравнения, ключи 38, регистры 39 сдвига и ключи 40.

Устройство работает следующим образом.

На передающей стороне информация, подлежащая передаче, преобразуется в аналогоцифровом преобразователе 1 в цифровую форму, кодируется в кодере 2, модулируется высокочастотным сигналом в модуляторе 3 и передается на приемную сторону. При передаче возможно искажение информации из-за воздействия помех.

На приемной стороне сигнал поступает в демодулятор 4, где входные элементарные сигналы преобразуются в тактовые моменты времени в соответствующие аналоговые сигналы. В результате указанного преобразования на выходе демодулятора 4 формируется сложный последовательный сигнал, представляющий собой точную копию входного сигнала. Этот сигнал последовательно подается в аналого-цифровые преобразователи 14 и 28 и на вход порогового элемента 5.

В рещающем блоке 19 сигнал преобразуется в аналого-цифровом преобразователе 28 в двоичную кодовую комбинацию которая запоминается в блоке 29 регистров. С поступлением на вход блока 29 очередной комбинации записанные в нем символы предыдущей комбинации переписываются в еледующие регистры 30.

Сложный аналоговый сигнал, поступающий на вход порогового элемента 5, преобразуется в двоичную кодовую комбинацию.

которая поступает на вход декодера 6 для исправления ощибок. С выхода декодера 6 двоичные сигналы поступают на вход кодера 20, кодирующего символы избыточным кодом. На выходе кодера 20 формируется разрешенная комбинация, которая подается на вход блока 21, где записывается и хранится в двоичных регистрах 22.

Синхронно с входными элементарными сигналами из хронизатора 18 на вход счетчика 10 поступают тактовые импульсы. В момент прихода на вход преобразователя 14 сигнала в счетчик 10 поступает очередной тактовый импульс. Двоичный код состояния счетчика 10 записывается в регистр 11 сдвига. Количество ячеек памяти в счетчике 10 и в регистре 11 одинаково.

Выходные сигналы преобразователя 14 и счетчика 10 подаются соответственно на входы элемента 15 ИЛИ. При этом первой через элемент 15 ИЛИ проходит кодовая комбинация из регистра 11, двоичный код которой отображает номер выходного сигнала. Считывание кода номера происходит во время функционирования преобразователя 14. Выходная комбинация преобразователя 14 поступает на вход элемента 15 ИЛИ, таким образом, с выхода элемента 15 ИЛИ на вход логического блока 16 последовательно поступают двоичные кодовые комбинации, состоящие из двух частей: первая часть А определяет порядковый номер элементарного сигнала, а вторая часть С - амплитуду сигнала.

Логический блок 16 упорядочивает совокупность двоичных кодовых комбинаций в соответствии с величинами двоичных кодов.

Для указанных начальных условий, на-пример, комбинации имеют вид

EI (CiAi) (1000001)

Ег (( (1010010)

ES СзАэ) (0100011)

Е4 ) (ОНО 100)

В десятичном счислении комбинации Е имеют вид

Е, (81) Ег (102) . ЕЗ 4 3) Е4 (6 4)

Рассматривают как с помощью логического блока 16 происходит упорядочивание комбинаций.

В течение всего времени функционирования блока 16 когда нет необходимости переписывать комбинации 4 из одного регистра 36 в другой, ключи 33 закрыты. Во время переписывания информации в регистрах 36 управляющий сигнал хронизатора 18 открывает ключи 33. В исходном состоянии все регистры 36 и 39 находятся в нулевом состоянии, ключи 38 и 40 закрыты, ключи 33 открыты.

Первой на вход логического блока 16 подается двоичная кодовая комбинация Еь

Она записывается в регистр 391. Параллельные выходы имеются не у всех ячеек памяти этого регистра 39, а только у тех ячеек, в которых записан код величины аналоговых сигналов - двоичная комбинация С. Следовательно, на одни входы элемента 37 сравнения подается двоичный код G -1000, а на другие ее входы аналогично подается нулевой код из регистра 361. В элементе 371 сравнения указанные коды сравниваются между собой. Если в результате сравнения окажется, что код Ci меньше или равен коду регистра 361, то сигнал управления с правого выхода элемента 37 поступает на управляющий вход ключа 40,В рассматриваемом случае код d больше нулевого кода и поэтому управляющий сигнал выдается с левого выхода элемента 37i сравнения на управляющий вход ключа 38i, открывая его. В этот момент времени с выходов элементов 34 ИЛИ снимают управляющий синхроимпульс хронизатора 18, длительность которого определяется временем переписывания двоичной кодовой комбинации Et из регистра 39i через открытый ключ 38t в регистр 36i. В то же время на все регистры 36 подаются тактовые импульсы от хронизатора 18 через открытые ключи 33. В результате комбинация Ej переписывается из регистра 391 в регистр 36i. Далее в регистр 39i записывается комбинация Ej. С помощью элемента 37i сравнения ее код С г сравнивается с кодом Ci комбинации EI из регистра Збь Величина двоичного числа С г (в десятичной системе счисления 10) больше величины двоичного числа Ci (в десятичной системе 8). Поэтому на левом выходе элемента 37i формируется управляющий сигнал, открывающий ключ 381, через который из регистра 391 в регистр 361 переписывается двоичная кодовая комбинация ЕЗ, сдвигая при этом комбинацию EI через элемент 351 ИЛИ в регистр Збг. В это время через открытые ключи 33 тактовые импульсы подаются на все регистры 36.

Очередная двоичная кодовая комбинация ЕЗ поступает в регистр 39i и в элементе 37 I, сравнения ее код С з (в десятичной системе 4) сравнивается с кодом Сг. Так как Сз меньше Cj, то на правом выходе элемента 371 сравнения формируется управляющий сигнал, который открывает ключ 40i, после чего из регистра 39i в регистр 39г переписывается комбинация Ej и осуществляется операция сравнения в элементе 372. В элементе 37 код С сравнивают с кодом Ci. Вследствие того, что код Сз меньше кода Ci, управляющий сигнал элемента 37 сравнения формируется на его правом выходе. По этому сигналу открывается ключ 40г, пропуская в регистр 39з двоичную комбинацию Е из регистра 39г. Теперь код Cj сравнивают с помощью

элемента 37} сравнения с нулевым кодом регистра Збз. В результате сравнения управляющий сигнал появляется на левом выходе элемента 37. Он открывает ключ 38з и закрывает ключ ЗЗг (последний закрывают для того, чтобы исключить поступление импульсов от хронизатора 18 для считывания комбинации Еа из регистра 36i).

В этом время снимается сигнал запрета на элементы 34 ИЛИ от хронизатора 18 и комбинация Ej из регистра 39 переписывается в регистр Звз.

Наконец во входной регистр 39 записывают комбинацию Е и осуществляют сравнение ее кода С с кодом Са комбинации Е , хранящейся в регистре 36i. Так как результат сравнения С4 меньше С (в десятичном представлении 6 меньще 10), то управляющий сигнал появляется на правом выходе элемента 37i сравнения, вследствие чего Е переписывается в регистр 39g, код С сравнивается с помощью элемента 37 сравнения с кодом С комбинации Ej. из регистра 36г. Результат сравнения: С. меньще Ci (6 меньще 8). Управляющий сигнал формируется на

правом выходе элемента 37г и осуществляется переписывание комбинации Е в регистр 39з. В регистре 39э код С сравнивают с кодом Сз комбинации ЕЗ из регистра Збз. Так как код С больще кода С j (6 больше 4), по управляющему сигналу с левого выхода

0 элемента 37 сравнения комбинации ЕЗ переписывается из регистра Збз в регистр 36, на ее место в регистр Збз переписывается из регистра 39з комбинация Е.

В результате в регистрах 36i - 36 соответственно записаны двоичные кодовые комбинации Ег, Ej, Е, Ej. К данному моменту времени заканчивается запись в регистр 7 двоичной кодовой комбинации.

Далее начинается последовательное счид тывание двоичных кодовых комбинаций А из регистра 36. При этом первой считывается комбинация АЗ, код С которой соответствует наименьшему символу. Считываясь, комбинации А записываются в регистр 17. С помощью дешифратора 13 код номера преобразуется в позиционный код. Позиционный код в виде кодовой комбинации единичного веса записывается в регистр 12. Одновременно из регистров 7 и 12 (с регенерацией) осуществляют последовательное считывание двоичных кодовых комбинаций через инвертор 8. Если на входе «в инвертора 8 нулевой сигнал, то двоичный сигнал с второго его входа «а проходит на выход без изменений. В противном случае символы с входа «а проходят на выход инвертора 8 с инвертированием. Следовательно, с выхода инвертора 8 на вход декодера б будет выдаваться двоичная кодовая комбинация У, , которая от личается от УО только в одном (наименее надежном) разряде.

Указанный процесс преобразования выходных двоичных комбинаций в логическом блоке 16 продолжают до тех пор, пока с выхода инвертора 8 не будет считана последняя комбинация. В этой комбинации инвертировано уже п символов по отношению к комбинации УО .

Каждая из комбинаций У после преобразования в разрешенные комбинации записывается в блок 21 регистров сдвига.

После этого в корреляторе 23 вычисляют степени близости (коэффициенты корреляции) между каждой из разрешенных двоичных кодовых комбинаций, хранящихся в блоке 21, и дискретной копией входного сигнала, хранящейся в блоке 29 регистров.

Технически коэффициент корреляции определяют следующим образом.

Из блоков 21 и 29 в коррелятор23 последовательно считываются двоичные символы кодовых комбинаций. Скорость считывания двоичных символов из блока 29 в В раз превышает скорость считывания двоичных символов из блока 21. За счет этого во время поступления на вход элемента 24 очередного двоичного сигнала на выход блока 29 выдается В штук двоичных символов. При поступлении на вход инвертора 25 от элемента 24 единичного сигнала соответствующая комбинация проходит на его выход с выхода блока 29 без изменения. При поступлении от элемента 24 нулевого сигнала на выход инвертора 25 поступает инвертированная комбинация . Следовательно, после первого считывания всей комбинации из блока

29 и первой разрешенной комбинации из блока 21 в сумматоре 26 будет вычислен коэффициент корреляции между двоичными комбинациями. Всего из блока 29 осуществляют п+1 считываний. Результат суммирования запоминается в элементе 27 сравнения.

Элемент 27 сравнения запоминает коэффициент корреляции между двоичными комбинациями. Всего из блока 29 осуществляют пн- 1 считываний. Результат суммирования за0 поминается в элементе 27 сравнения.

Элемент 27 сравнения запоминает коэффициент корреляции, например первый. Другой (второй) сигнал сравнивается с первым. Если он больше первого, то первый стираетс ся, а второй запоминается. Если второй сигнал больше (или равен) первому, то стирается второй сигнал и т.д. В результате в элементе 27 остается только максимальный сигнал (номер сигнала).

На одном из выходов элемента 27 срав0 нения формируется управляющий сигнал, по которому на выход решающего блока 19 через элемент 31 ИЛИ будет считана та разрешенная комбинация, для которой коэффициент корреляции имеет наибольшее зна5 чение.

Сигналы с выхода решающего блока преобразуется в декодере 32 в выходные сообщения.

Технико-экономическое преимущество предлагаемого устройства по сравнению с устройством-прототипом заключается в том, что в предлагаемом устройстве в большей степени используется апостериорная информация об амплитуде принимаемых элементарных сигналов, что повышает достоверность принимаемой информации.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема и обработки избыточных сигналов | 1982 |

|

SU1078455A1 |

| Устройство для приема и обработки избыточных сигналов | 1982 |

|

SU1115086A1 |

| Устройство для приема и обработки избыточных сигналов | 1983 |

|

SU1152017A2 |

| Устройство для приема и градиентного декодирования избыточных сигналов | 1983 |

|

SU1152016A1 |

| Устройство для приема избыточных сигналов | 1989 |

|

SU1695353A1 |

| Устройство для приема сигналов с избыточностью | 1983 |

|

SU1128281A1 |

| Устройство для приема избыточной информации | 1982 |

|

SU1032470A1 |

| Устройство для приема и обработки избыточных сигналов | 1984 |

|

SU1193713A1 |

| Устройство для приема избыточной информации | 1983 |

|

SU1107146A1 |

| Устройство для приема и градиентного декодирования избыточных сигналов | 1985 |

|

SU1282184A1 |

УСТРОЙСТВО ДЛЯ ИЗБЫТОЧНОЙ ИНФОРМАЦИИ, содержащее демодулятор, первый вход которого является входом устройства, первый пороговый элемент, первый декодер, регистр и хронизатор, первый, второй и третий выходы которого соединены с соответствующими первым, вторым и третьим входами ранжирующего узла, отличающееся тем, что, с целью повышения достоверности принимаемой информации, в него введены инверторы, кодер, второй пороговый элемент, сумматор, элемент сравнения, аналого-цифровой преобразователь, элемент ИЛИ, второй декодер, первый блок регистров, выполненный на регистрах, выход каждого предь1дущего регистра соединен с первым входом каждого последующего регистра, выход последнего регистра соединен с первым входом первого регистра, и второй блок регистров, выполненный на последовательно соединенных регистрах, выход последнего регистра соединен с входом первого регистра, выхрд демодулятора соединен с четвертым входом ранжирующего узла, первым входом аналого-цифрового преобразователя и через первый пороговый элемент - с первым входом первого декодера и входом регистра, выходы регистра и ранжирующего узла соединены соответственно с первым и вторым входами первого инвертора, выход которого соединен с вторым входом первого декодера, выход первого декодера соединен через кодер с первым входом первого регистра первого блока регистров, выход последнего регистра первого блока регистров соединен через второй пороговый элемент с первым входом второго инвертора, выход которого соединен через сумматор с входом элемента сравнения, выходы элемента сравнения § соединены с вторыми входами соответствующих регистров первого блока регистров, (Л выходы которых соединены с соответствующими входами элемента ИЛИ, выход элемента ИЛИ соединен с первым входом второго декодера, выход которого является выходом устройства, выход аналого-цифрового преобразователя соединен с входом первого регистра второго блока регистров, выход последнего регистра второго блока О) регистров соединен с вторым входом вто рого инвертора, вход хронизатора подклюО5 чен к входу устройства, четвертый, пятый, со шестой и седьмой выходы хронизатора сое00 динены соответственно с вторым входом второго декодера, третьим входом первого декодера, вторым входом аналого-цифрового преобразователя и вторым входом демодулятора.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Питерсон У., УЭЛД.ОН, Э | |||

| Коды, исправляющие ошибки | |||

| М., Мир, 1976, с | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР по заявке № 3510529/24, кл | |||

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1985-07-15—Публикация

1984-01-06—Подача