t

(21)4246123/24-09

(22)19.05.87

(46) 30.10.89. Бюл. № 40

(71)Харьковский политехнический институт им.Б.И. Ленина

(72)В.П. Гетман, М.А. Иванов и И.И. Сватовский

(53)621.376.52(088.8)

(56)Пекин П.И. и др. Радиотехнические системы передачи информации. М.: Радио и связь, 1984, с. 192-193.

(54)СИСТЕМА ПЕРЕДАЧИ ЦИФРОВОЙ ИНФОРМАЦИИ

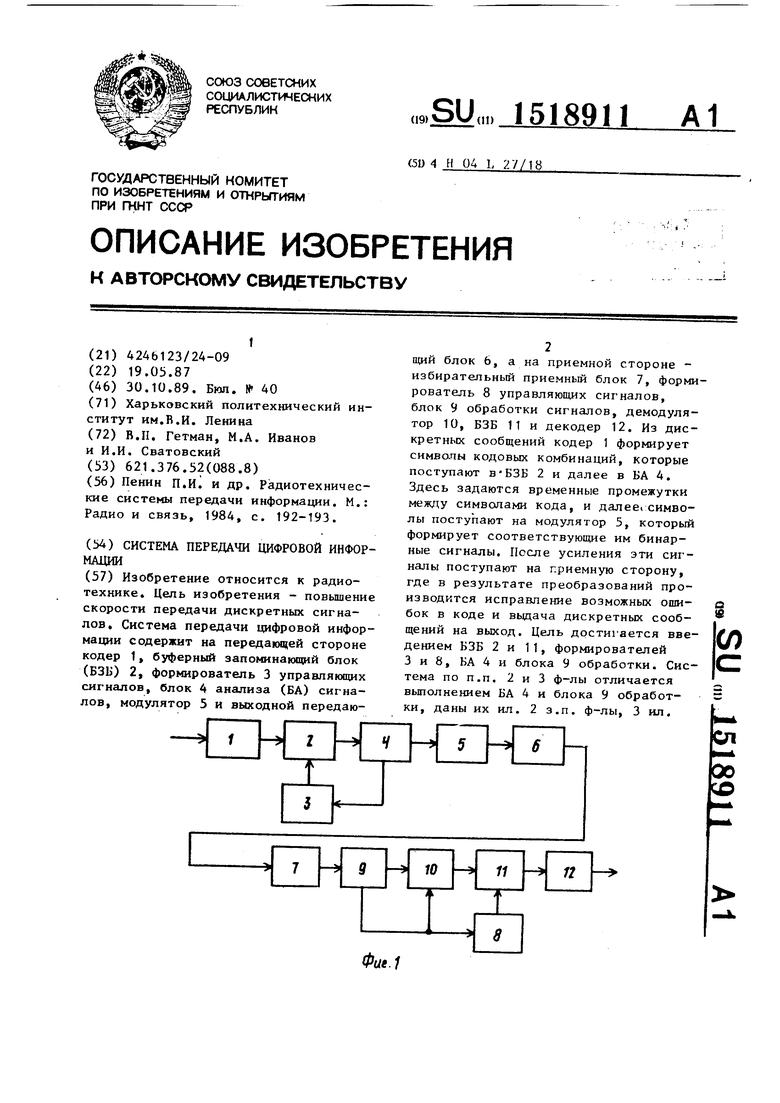

(57)Изобретение относится к радиотехнике. Цель изобретения - повышение скорости передачи дискретных сигналов. Система передачи цифровой информации содержит на передающей стороне кодер 1, буферный запоминающий блок (БЗЬ) 2f формирователь 3 управляющих сигналов, блок 4 анализа (БА) сигналов, модулятор 5 и выходной передающий блок 6, а на приемной стороне - избирательный приемный блок 7, формирователь 8 управляющих сигналов, блок 9 обработки сигналов, демодулятор 10, БЗБ 11 и декодер 12. Из дискретных сообщений кодер 1 формирует симвапы кодовых комбинаций, которые поступают в-БЗБ 2 и далее в БА 4. Здесь задаются временные промежутки между символами кода, и далее символы поступают на модулятор 5, который формирует соответствующие им бинарные сигналы. После усиления эти сигналы поступают на приемную сторону, где в результате преобразований производится исправление возможных ошибок в коде и вьщача дискретных сообщений на выход. Цель достигается введением БЗБ 2 и 11, формирователей 3 и 8, БА 4 и блока 9 обработки. Система по п.п. 2 и 3 ф-лы отличается выполнением БА 4 и блока 9 обработки, даны их ил. 2 з.п. ф-лы, 3 ил.

(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| МУЛЬТИМИКРОКОНТРОЛЛЕРНАЯ СИСТЕМА | 1997 |

|

RU2120135C1 |

| СТАРТСТОПНАЯ СИСТЕМА СВЯЗИ | 2003 |

|

RU2252489C2 |

| Система для телеконтроля промежуточных станций линий связи | 1987 |

|

SU1453603A1 |

| РАДИОМОДЕМ | 2010 |

|

RU2460215C1 |

| Кодер | 1990 |

|

SU1783623A1 |

| Устройство коррекции двойных ошибок с использованием кода Рида-Соломона | 1988 |

|

SU1662010A1 |

| Многоканальное устройство для регистрации аналоговых и цифровых сигналов | 1988 |

|

SU1564649A1 |

| Устройство для контроля знаний обучаемых | 1987 |

|

SU1524082A1 |

| Устройство для согласования потоков телеметрических отсчетов | 1987 |

|

SU1543561A1 |

| Устройство для отображения информации | 1986 |

|

SU1446642A1 |

Изобретение относится к радиотехнике. Цель изобретения - повышение скорости передачи сигналов. Система передачи цифровой информации содержит на передающей стороне кодер 1, буферный запоминающий блок (БЗБ) 2, формирователь 3 управляющих сигналов, блок анализа (БА) 4 сигналов, модулятор 5 и выходной передающий блок 6, а на приемной стороне избирательный приемный блок 7, формирователь 8 управляющих сигналов, блок 9 обработки сигналов, демодулятор 10, БЗБ 11 и декодер 12. Из дискретных сообщений кодер 1 формирует символы кодовых комбинаций, которые поступают в БЗБ 2 и далее в БА 4. Здесь задаются временные промежутки между символами кода, и далее символы поступают на модулятор 5, который формирует соответствующие им бинарные сигналы. После усиления эти сигналы поступают на приемную сторону, где в результате преобразований производится исправление возможных ошибок в коде и выдача дискретных сообщений на выход. Цель достигается введением БЗБ 2 и 11, формирователей 3 и 8, БА 4 и блока 9 обработки. Система по п.п. 2 и 3 ф-лы отличаются выполнением БА 4 и блока 9 обработки, даны их ил. 2 з.п.ф-лы, 3 ил.

ел

00

со

Фае.1

И ujOpi- teHHe относится к радшггех- miKt и может быть использовано в ра- ;у1осис:темах передачи дискретной информации,

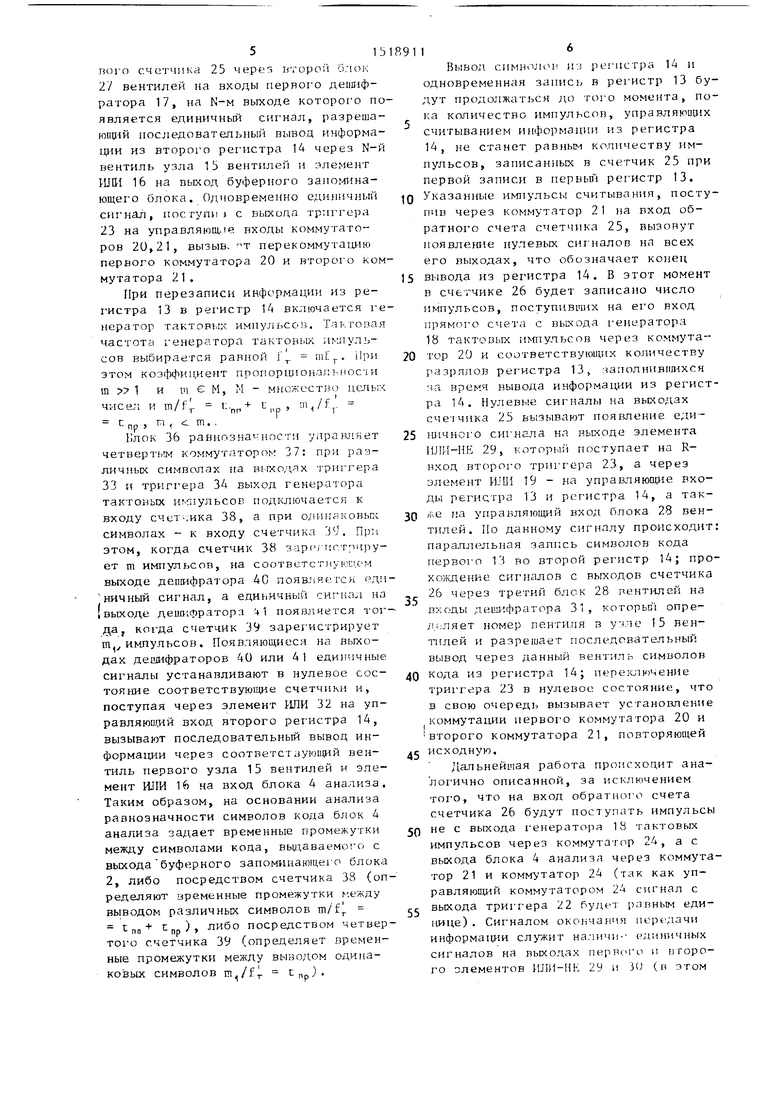

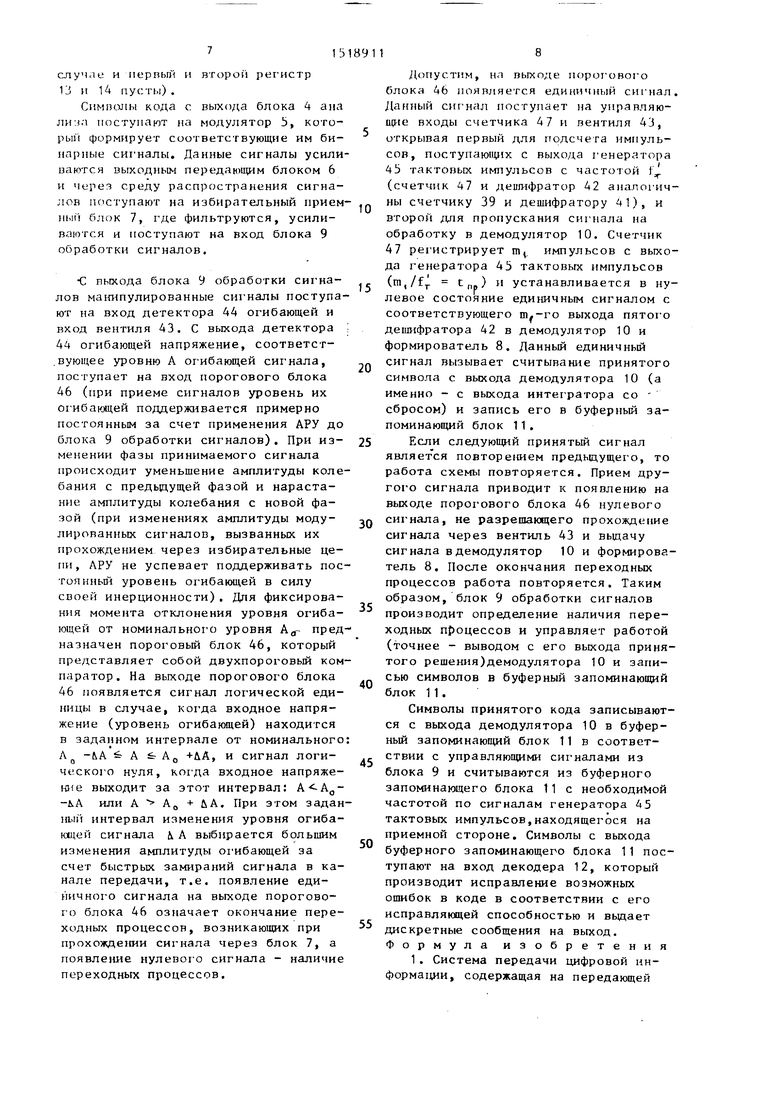

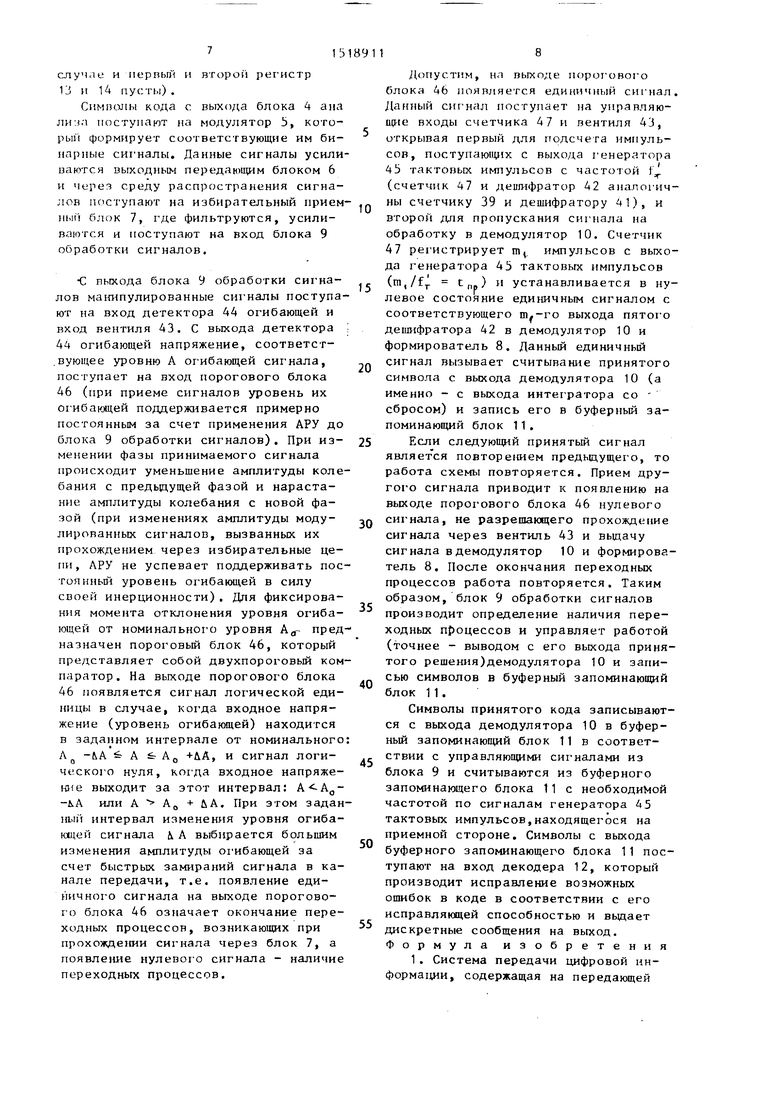

Цель изобретения - повышение скорости нередачи дискретных сигналов. На фиг. 1 изображена структурная элекг - ическая схема предложенной системы; на фиг. 2 - структурная элект- рическая схема блока анализа сигналов, структурная электрическая схема буфе11ного запоминающего блока и структурная электрическая схема фор- мир пватеня управляющих сш-налов; на фиг- . 3 - структурная электрическая .схема блока обработки сигналов. I Система передачи цифровой информации содержит на передающей стороне кодер 1, буферный запоминающий блок 2, формирователь 3 управляющих сигналов, блок 4 анализа сигналов, модулятор 5 и выходной передающий блок 6, а на приемной стороне - избирательный приемный блок 7, формирсва- тель 8 управляюпщх сигналов, блок 9 обработки сигналов, демодулятор 10, буферный запоминаюп й блок 11 и декодер 12.

Буферный запоминающий блок содер- жит первый и второй регистры 13 и 14 узел 15 вентилей и элемент ИЛИ 16.

Формирователь управляющих сигна- лов содержит первый дешифратор 17, генератор 18 тактовых импульсов, эле мент Ш1И 19, первьш и второй коммутаторы 20 и 21, первый и второй триггеры 22 и 23, третий коммутатор 24, первый и второй счетчики 2Ь и 26, первый и второй блоки 27 и. 28 венти- лей, первый и второй элементы ИЛИ-НЕ 29 и Зи и второй дешифратор 31.

Блок анализа сигналов содержит элемент Ш1И 32, первый и второй триггеры 33 и 34, 1 енератор 35 тактовых импульсов, блок 36 равнозначности, коммутатор 37, первый и второй счетчики 38 и 39 и первый и второй дешифраторы 40 и 41.

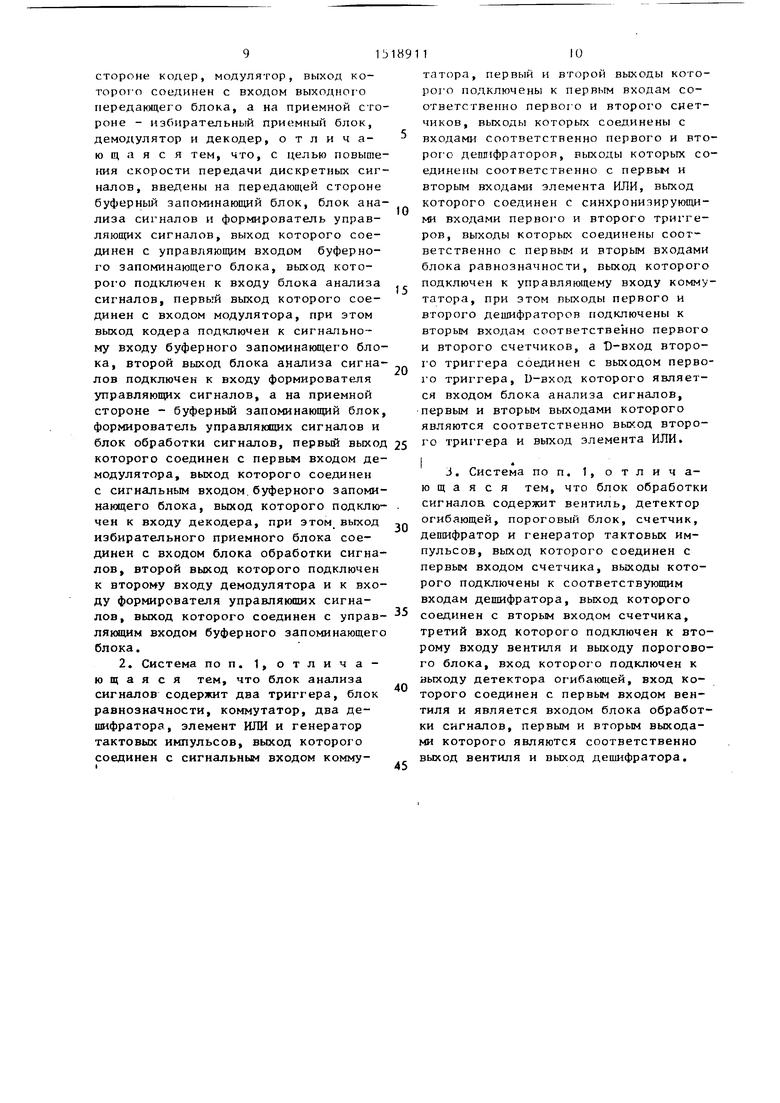

Блок обработки сигналов содержит дешифратор 42, вентиль 43, детектор 44 огибающей, генератор 45 тактовых импульсов, порот овый блок 46 и счетчик 47 .

Система работает следующим образом.

На вход кодера 1 поступают дискретные сообщения в виде последовательности двоичных символов (нулей

д

0

и единиц) , п к торые вносится но специсгльному алгоритму некоторая избыточность (помехоустойчивое кодирование) . Символы кодовых комбинаций с выхода кодера 1 поступают на вход буферного запоминающего блока 2,которое выполняет функции промежуточного хранения символов кода и вывода последних в соответствии с результатами их анализа в блоке 4 анализа сигналов.

Для вьтолнения данной функции символы кодов записываются в первый регистр 13 по сигналам записи, поступающим с выхода генератора 18 тактовых импульсов с такой же тактовой частотой f, что и символы кода (для простоты считаем, что тактовая частота поступления символов кода уже согласована с условиями дальнейшей передачи по каналу, т.е. f. 1/ /( trjp) . С началом заполнения первого регистра 13, емкость которого равна N символам, тактовые импульсы поступают через первый коммутатор «20 на вход прямог о счета первого счетчика 25, а также через третий коммутатор 24 - на вход обратного счета второго счетчика 26 (счетчики

25и 26 представляют собой 1-разрядные счетчики с входами прямого и обратного счета, в исходном положении первый счетчик 25 обнулен, а в 1 разрядов второго счетчика 26 записаны единицы, при этом 1 log(N+l). Поступающие на второй счетчик 26 тактовые импульсы приводят к установке его в нулевое состояние в тот момент, когда полностью заполняется первый регистр 13. Появление нулевых сигналов на всех выходах второго счетчика

26вызывает появление единичного сигнала на выходе элемента ИЛИ-НЕ 30. Данный единичньй сигнал поступает на S-вход второго триггера 23 и выэьша- ет его переключение из исходного нулевого в единичное состояние. Этот

же единичный сигнал поступает через элемент ИЛИ 19 на входы управления первого регистра 13 и второго регистра 14 и вызывает параллельную перезапись символов кода с перво1-о регистра 13 во второй регистр 14, а также устанавливает первый триггер 22 из исходного нулевого в единичное состояние. Единичный сигнал с выхода элемента ИПИ-НЕ 30 также разрешает прохождение сигналов с выходов пер515

Boro с,четч1 ка 25 через второ) 5:ioK 27 вентилей на входы первог о деишф- ратора 17, на N-M выходе которог о появляется единичный сиг нал, разреша- последовательный вывод информации из второго регистра 14 через N-й вентиль узла 15 вентилей и элеме1гг ШШ 16 на вькод буферного запог-тина- ющего блока. Одт овременно единичньй сигнал, поступи с выхода тр;1ггера 23 на управляющие входы коммутаторов 20,21, вызыв. перекоммутадию первого коммутатора 20 и второго коммутатора 21.

При перезаписи инфсфмации из регистра 13 в регистр 14 включается генератор такторьгх импульсо з. Тактовая частота генератора тактонык импульсов выбирается равной Г mt-j.. При зтом коэеЬфициент nponopiyionajn-tioc-i и m 1 и 14 е М, М - множсст1зо чисел и m/f; i:.+ tm,

m. .

Нлок 36 равнознаь:иости {травляет четвертьтм KOMMyTaTOpoN 37: при различных символах на выходах триггера 33 и триггера 34 выход генератора тактовых иг-шульсов под1 слючается к входу счетчика 38, а при о,пипаковьк символах - к входу счетчика 39. Пр:1 этом, когда счетчик 38 зарргиг.трчру- ет m импульсов, на соответстиую :1ом выходе депшфрап ора 40 пoявJ яeтc i едм с пр , п,

ничный сигнал, а единичнын сигнал на

(Выходе дешифратора - появляется тог да, когда счетчик 39 зарегч{стрирует т импульсов. Появляющиеся на выходах дешифраторов 40 или 41 единичные сигналы устанавливают в нулевое сое- соответствующие счетчики и, поступая через элемент ИЛИ 32 на уп- равляюидай вход второго регистра 14, вызывают последовательный вывод информации через соответствующий вен- тиль первого узла 15 вентилей и элемент ИЛИ 16 на вход блока 4 анализа. Таким образом, на основании анализа равнозначности символов кода блок 4 анализа задает временные промежутки между символами кода, выдаваемого с выхода буферного запоминающего блока 2, либо посредством счетчика 38 (определяют временные промежутки ,eждy выводом различных символов т/f

Сп„+ t ), либо посредством четвертого счетчика 39 (определяет временные промежутки между выводом одина- ковьа символов t ).

д 5

0

5 0

5

Q 5 0

М6

Вывод симнол(1Б И .) регистра 14 и одновременная запись в регистр 13 будут продолжаться до того момента, пока количество импульсов, управляюищх считыванием информации из регистра 14, не станет равным количеству импульсов, записанных в счетчик 25 ири первой записи в иервьш регистр 13. Указаннь е импульсы считывания, поступив через коммутатор 21 на вход обратного счета счетчика 25, вызовут появление нулевьк сиг налов на всех его выходах, что обозначает конец вывода из регистра 14. В этот момент в счетчике 26 будет записано число импульсов, поступивишх на его вход Г1РЯМОГО счета с выхода генератора 18 тактовых 1 тульсов через коммутатор 20 и соответствующих количеству разрялов регистра 13 заг1олнив1Ш1хся ма время вывода информа1ц 1и из регистра 14. Нулевые сигналы на выходах счетчика 25 вызывают поягшение еди- iai4Horo сигнала на выходе элемента ИЛИ-НК; 29, который поступает на R- нход второго триггера 23, а через элемент ШШ 19 - на управляющие входы регистра 13 и регистра 14, а также на управляющий вход блока 28 вентилей. По данному сигналу происходит: параплельная запись символов кода первого 13 во второй регистр 14; про холадение сигналов с выходов счетчика 26 через третий блок 28 рент1-шей на входы дешифратора 31, которьп опре- л.«;ляет номер пентиля в унле 15 вентилей и разрешает последовательный вывод через данный вентиль символов кода из регистра 14; переключение триггера 23 в нулевое, состояние, что в СБОЮ очередь вызывает установление коммутащш иервог О коммутатора 20 и второго коммутатора 21, повторяющей исходную.

Дальнейшая работа происходит аналогично описанной, за исключением того, что на вход обратнот о счета счетчика 26 будут поступать импульсы не с выхода генератора 18 тактовых импульсов через коммутатор 24, а с выхода блока 4 анализа через коммутатор 21 и коммутатор 24 (так как управляющий коммутатором 24 сигнал с выхода триггера 22 будет равным единице) . Сигналом окончания передачи информации служит на.чичи- еди1 ичных сигналов на выходах первси о и второго элементов ИЛИ-НК 29 и 30 (в этом

случае и мервьш и второй регистр 13 и 14 пусты).

СИМПШ1Ы кода с выхода блока 4 ана липа поступают на модулятор Ь, который формирует соответствующие им бинарные сиг налы. Данные сигналы усили иаются выходным передающим блоком 6 и через среду распространения сигналов поступают на избирательный прием П1,11 блок 7, где фильтруются, усиливаются и поступают на вход блока 9 обработки сигналов.

С выхода блока 9 обработки сигналов манипулированные сигналы поступают на вход детектора ДА огибающей и вход вентиля A3. С выхода детектора 44 огибающей напряжение, соответст- .вующее уровню А огибающей сигнала, поступает на вход порогового блока 46 (при приеме сигналов уровень их О1 ибающей поддерживается примерно постоянным за счет применения АРУ до блока 9 обработки сигналов). При изменении фазы принимаемого сигнала происходит уменьшение амплитуды колебания с предьдущей фазой и нарастание амплитуды колебания с новой фазой (при изменениях амплитуды модулированных сигналов, вызванных их прохождением через избирательные цепи , АРУ не успевает поддерживать постоя нньш уровень огибающей в силу своей инерционности). Для фиксирования момента отклонения уровня огибающей от номинального уровня предназначен пороговый блок 46, который представляет собой двухпороговый компаратор. На выходе порогового блока 46 появляется сигнал логической единицы в случае, когда входное напряжение (уровень огибающей) находится в заданном интерпале от номинального Ад А АО +ЛА, и сигнал логического нуля, когда входное напряжение выходит за этот интервал; -КА или А АО + ЬА. При этом заданный интервал изменения уровня огибающей сигнала h. А выбирается большим изменения амплитуды огибающей за счет быстрых замираний сигнала в канале передачи, т.е. появление единичного сигнала на выходе порогового блока 46 означает окончание переходных процессов, возникающих при прохождении сигнала через блок 7, а появле1ше нулевого сигнала - наличие переходных процессов.

0

5

0

5

0

5

0

5

0

5

Допустим, нл выходе порогового блока 46 появляется единичный сигнал. Данный сигнал поступает на управляющие входы счетчика 47 и вентиля 43, открывая первый для подсчета импульсов, поступающих с выхода генератора 4Ь тактовых импульсов с частотой i . (счетчик 47 и деишфратор 42 аналогичны счетчику 39 и дешифратору 41), и второй ;ц1я пропускания сигнала на обработку в демодулятор 10. Счетчик 47 регистрирует т, импульсов с выхода генератора 45 тактовых импульсов (m,/f Ср ) и устанавливается в нулевое состояние единичным сигналом с соответствующего выхода пятого де11П1фратора 42 в демодулятор 10 и формирователь 8. Данный единичный сигнал вызывает считывание принятого символа с вьсхода демодулятора 10 (а именно - с выхода интегратора со - сбросом) и запись его в буферный запоминающий блок 11.

Если следующий принятый сигнал является повторением предьщущего, то работа схемы повторяется. Прием другого сигнала приводит к появлению на выходе порогового блока 46 нулевого сигнала, не разрешающего прохождение сигнала через вентиль 43 и выдачу сигнала в демодулятор 10 и формирователь 8. После окончания переходных процессов работа повторяется. Таким образом, блок 9 обработки сигналов производит определение наличия переходных п{)оцессов и управляет работой (точнее - выводом с его выхода принятого решения)демодулятора 10 и записью символов в буферный запоминающий блок 11.

Символы принятого кода записываются с выхода демодулятора 10 в буферный запоминающий блок 11 в соответствии с управляющими сигналами из блока 9 и считываются из буферного запоминающего блока 11 с необходи юй частотой по сигналам генератора 45 тактовых импульсов,находящегося на приемной стороне. Символы с выхода буферного запоминающего блока 11 поступают на вход декодера 12, который производит исправление возможных ошибок в коде в соответствии с его исправляющей способностью и вьщает дискретные сообщения на выход. Формула изобретения

стороне кодер, модулятор, выход ко- торог о соединен с входом выходног-о передающего блока, а на приемной стороне - избирательный приемный блок, демодулятор и декодер, отличающаяся тем, что, с целью повып1е- ния скорости передачи дискретных сигналов, введены на передающей стороне буферный запоминающий блок, блок анализа сигналов и формирователь управляющих сигналов, выход которого соединен с управляющим входом буферного запоминающего блока, выход которого подключен к входу блока анализа сигналов, первый выход которого соединен с входом модулятора, при этом выход кодера подключен к сигнальному входу буферного запоминающего блока, второй выход блока анализа сигналов подключен к входу формирователя управляющих сигналов, а на приемной стороне - буферный запоминающий блок, формирователь управляющих сигналов и блок обработки сигналов, первый вькод которого соединен с первым входом демодулятора, выход которого соединен с сигнальным входом.буферного запоминающего блока, выход которого подключен к входу декодера, при этом выход избирательного приемного блока соединен с входом блока обработки сигналов, второй выход которого подключен к второму входу демодулятора и к входу формирователя управляющих сигналов, выход которого соединен с управ- лякяцим входом буферного запоминающего блока.

2, Система по п. 1, отличающая с я тем, что блок анализа сигналов содержит два триггера, блок равнозначности, коммутатор, два дешифратора, элемент ИЛИ и генератор тактовых импульсов, выход которого соединен с сигнальным входом комму0

5

0

5

0

5

0

5

татора, первый и второй выходы которого подключены к первым входам соответственно первог о и второго снет- чиков, выходы которых соединены с входами соответственно первого и вто- рог о депл1фраторов, выходы которых соединены соответственно с первым и вторым входами элемента ИЛИ, выход которого соединен с синхронизирующими входами первого и второго триггеров, выходы которых соединены соответственно с первым и вторым входами блока равнозначности, выход которого подключен к управляющему входу коммутатора, при этом выходы первого и второго деишфраторов подключены к вторым входам соответственно первого и второго счетчиков, а Т)-вход второ- I O триггера соединен с выходом первого триггера, D-вход которого является входом блока анализа сигналов, первым и вторым выходами которого являются соответственно выход второго три1 гера и выход элемента ИЛИ.

I.

Авторы

Даты

1989-10-30—Публикация

1987-05-19—Подача