(54) ЦИФРОВОЙ РЕГУЛЯТОР ДАВЛЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство автоматического согласования и контроля режимов многоступенчатых насосных и гидротранспортных установок | 1982 |

|

SU1079568A1 |

| Адаптивная система управления для объектов с изменяющимся запаздыванием | 1984 |

|

SU1191884A1 |

| Регулятор | 1979 |

|

SU824133A1 |

| Устройство для регулирования технологических параметров по заданной программе | 1983 |

|

SU1136121A1 |

| Трехпозиционное импульсное пороговое устройство | 1987 |

|

SU1529173A1 |

| Устройство для измерения уровней радиосигналов в системах связи | 1978 |

|

SU758539A1 |

| Адаптивная система управления для объектов с запаздыванием | 1985 |

|

SU1310774A1 |

| Многоканальный регулятор | 1988 |

|

SU1564586A1 |

| Электропривод подъемной машины | 1985 |

|

SU1339852A1 |

| Импульсный регулятор | 1984 |

|

SU1259209A1 |

1

Устройство относится к приборам и системам автоматического управления и регулирования и может быть использовано в различных .областях науки и техники для квазиоптимального по быстродействию регулирования давления в системах второго порядка.

Известно устройство для автоматического управления, предназначенное для квазиоптимального по быстродействию управле,ния в системах второго порядка 1.

Наиболее близким по технической сущности к предлагаемому является регулятор давления, содержащий датчик сигнала рассогласования и релейный усилитель 2.

Однако известный регулятор давления не учитывает при работе величину возмущений и поэтому в системах, подверженных сильным возмущениял не обеспечивает высокой точности регулирования.

Цель изобретения - увеличение точности, регулятора давления.

Поставленная цель достигается тем, что в известное устройство введены аналогоцифровой преобразователь, элемент зядержки, пороговый элемент, блок формирования знака и последовательно соединенные дещифратор, блок памяти и блок изменения

порога, причем выход датчика сигнала рассогласования соединен с входом аналогоцифрового преобразователя, выход которого соединен с входом элемента зад., с входом дещифратора и с первыми входами порогового элемента и блока формирования знака, выход которого соединен с входом релейного усилителя, а второй вход - с выходом порогового элемента, второй вход - с выходом элемента задержки, а третий вход - с выходом блока изменения порога.

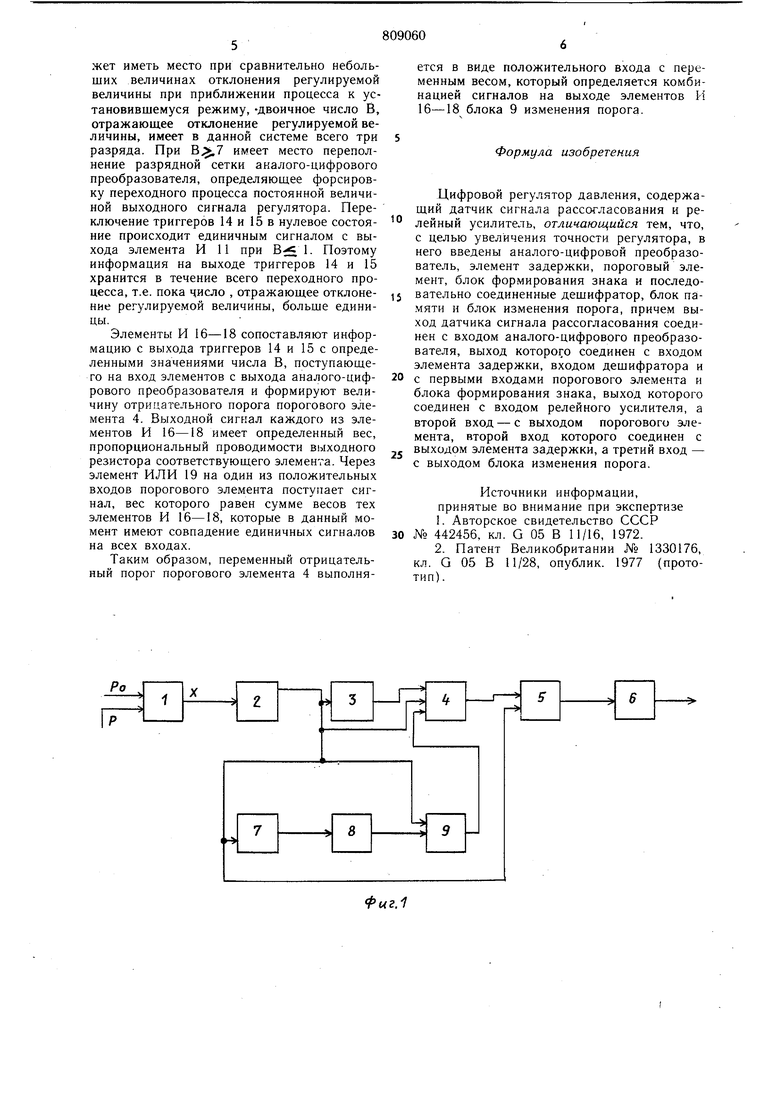

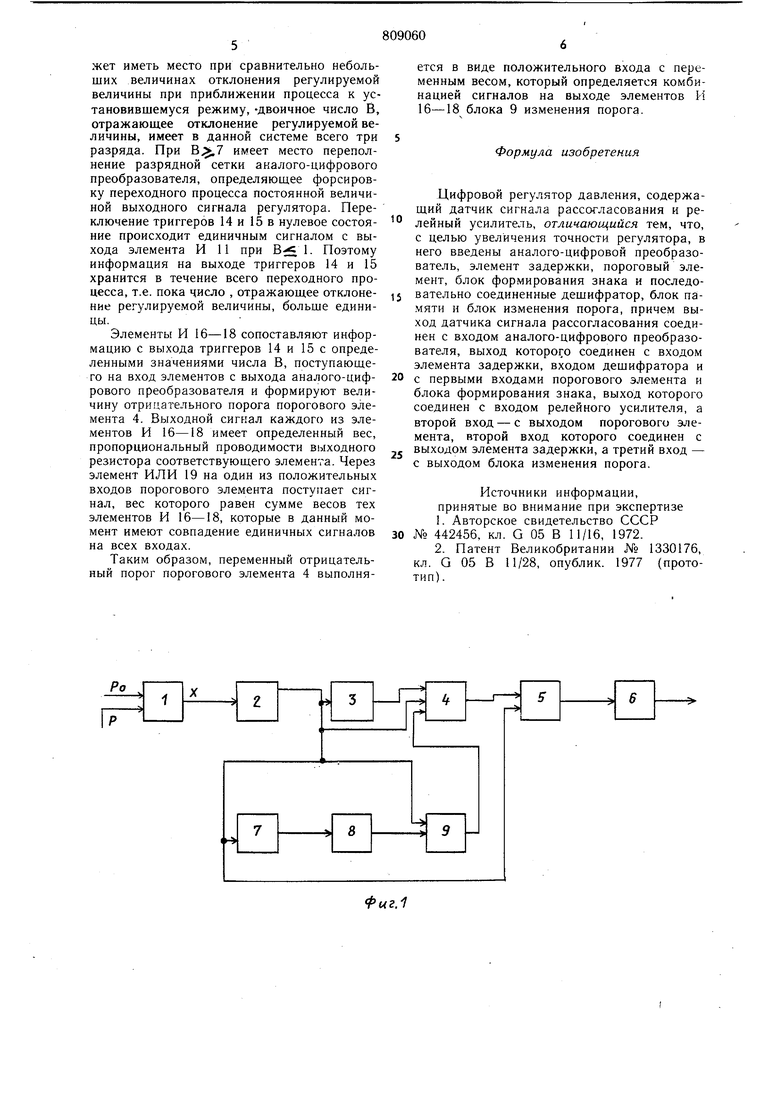

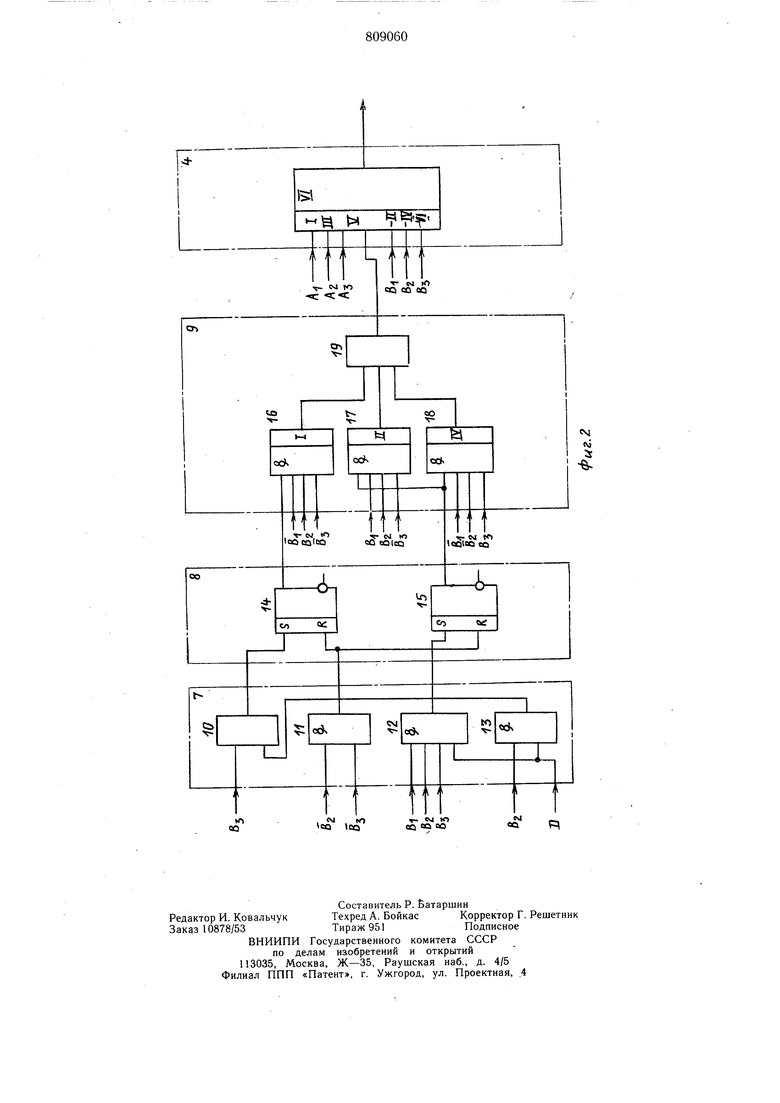

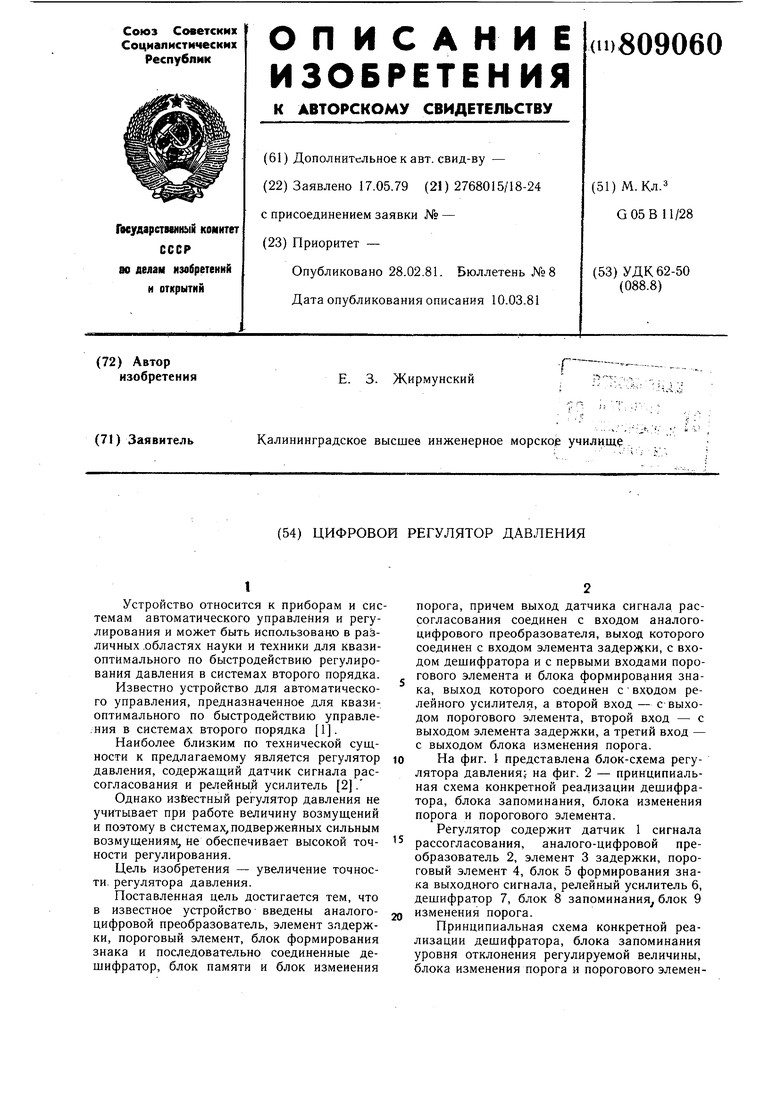

0 На фиг. 1 представлена блок-схема регулятора давления;- на фиг. 2 - принципиальная схема конкретной реализации дещифратора, блока запоминания, блока изменения порога и порогового элемента.

Регулятор содержит датчик 1 сигнала рассогласования, аналого-цифровой преобразователь 2, элемент 3 задержки, пороговый элемент 4, блок 5 формирования знака выходного сигнала, релейный усилитель 6, дешифратор 7, блок 8 запоминания блок 9

изменения порога.

Принципиальная схема конкретной реализации дещифратора, блока запоминания уровня отклонения регулируемой величины, блока изменения порога и порогового элемента с переменным отрицательным порогом содержит логический элемент ИЛИ 10, логические элементы И 11 -13, триггеры 14, . 15, логические элементы И 16-18, выходные резисторы которых имеют различные проводимости, -пропорциональные составляющим (весам) переменного порога, логический элемент ИЛИ 19. Кроме того, обозначены веса I-VI входов и выходов, цифровые разряды А(-АЗС выхода элемента задержки, цифровые разряды А с инверсных выходов, цифровые разряды BI-Bj с выхода аналого-цифрового преобразователя, вход Д-знакового разряда аналого-цифрового преобразователя. Пороговый элемент представляет собой триггер Шмидта, в котором резисторные разветвления в базовых цепях первого и второго каскадов являются соответственно положительными и отрицательными входами, веса которых определяются проводимостью резисторов, линия 3 задержки в сочетании с пороговым элементом 4 является дифференциатором отклонения регулируемой величины, а пороговый элемент является одновременно сумматором пропорциональной и дифференциальной составляющих регулируемой величины. Устройство работает следующим образом. Датчик 1 сигнала рассогласования выдает на вход блока 2 аналоговый сигнал. На выходе аналого-цифрового преобразователя этот сигнал преобразуется в цифровой двоичный код и подается на отрицательные входы порогового элемента 4 и через элемент 3 задержки на положительные входы порогового элемента. Кроме того, аналого-цифровой преобразователь 2 вырабатывает тактовые импульсы и обеспечивает одновременность поступления информации со своего выхода и с выхода линии 3 задержки на вход порогового элемента 4. Пороговый элемент 4, имея на положительных входах число, отображающее X (п), а на отрицательных X (п + 1) сравнивает разность взвещенных в соответствии с весами входов сигналов на положительном и отрицательном входах порогового элемента с пере.менным отрицательным по рогом. Таким образо.м, производится сопоставление пропорциональной и дифференциаль ной составляющих отклонения регулируемой величины, а также учет возмущении и начальных условий процесса (через переменный отрицательный порог) и определяется момент переключения выходного сигнала регулятора. Блок 5 определения знака выходного сигнала, сопоставляя информацию с выхода порогового элемента 4 с информацией о знаке отклонения регулируелмой величины, поступающей с выхода аналогоцифрового преобразователя 2, определяет знак выходного сигнала регулятора между моментами переключений. Релейное усилительное звено 6 задает соответствующий уровень выходного сигнала регулятора, определяемый ограничениями в данной конкретной системе. При этом форма выходного сигнала является релейной и задача регулятора в основном сводится к определению момента переключения с форсировки переходного процесса на интервал, снимающий перерегулирование. Дешифратор 7, блок 8 запоминания уровня отклонения регулируемой величины, блок 9 изменения порога совместно с пороговым элементом 4 осуществляют коррекцию по возмущениям, определяя дискретно уровень возмущений по уровню максимального отклонения регулируемой величины, дешифратор 7 фиксирует факт достижения максимальным отклонением регулируемой величины определенного уровня и передает инфор.мацию на вход блока 8 запоминания уровня отклонения регулируемой величины, который преобразует эту информацию в соответствующую комбинацию выходных сигналов триггеров и хранит ее в течение всего переходного процесса. Блок 9 изменения порога сопоставляет информацию с выхода блока 8 запоминания уровня отклонения регулируемой величины с информацией о текущем значении отклонения регулируемой величины с выхода аналого-цифрового преобразователя 2 и задает соответствующую величину отрицательного порога порогового элемента 4, который, сопоставляя ее с пропорциональной и дифференциальной сопоставляющими отк.,1онениями регулируемой величины, определяет момент переключения выходного сигнала регулятора. Работу элементов, осуществляющих коррекцию по возмущениям, лучше проследить по принципиальной схеме конкретной реализации этих элементов (фиг. 2). Вход D элементов И 12, 13 имеет единицу только при отрицательных отклонениях регулируемой величины и определяет неравнозначность инфор.мации на выходе дешифратора 7 при различных знаках отклонения регулируемой величины для данной конкретной системы. При положительном отклонении регулируемой величины и достижении им значения, соответствующего числу В 4 (это означает единичный сигнал на входе третьего разряда В) с выхода элемента ИЛИ 10 поступает единичный сигнал на вход S триггера 14 и переключает его в единичное состояние. При отрицательном отклонении регулируемой величины то же самое происходит при В 2, поскольку в этом случае с выхода элемента И 13 через элемент ИЛИ 10 на вход S триггера 14 также поступает единичный сигнал. При отрицательном отклонении регулируемой величины и при В 7 с выхода элемента И 12 поступает единичный сигнал на вход S триггера 15, устанавливая его в единичное состояние. Поскольку переключение выходного сигнала регулятора может иметь место при сравнительно небольших величинах отклонения регулируемой величины при приближении процесса к установившемуся режиму, -двоичное число В, отражающее отклонение регулируемой величины, имеет в данной системе всего три разряда. При имеет место переполнение разрядной сетки аналого-цифрового преобразователя, определяющее форсировку переходного процесса постоянной величиной выходного сигнала регулятора. Переключение триггеров 14 и 15 в нулевое состояние происходит единичным сигналом с выхода элемента И 11 при 1. Поэтому информация на выходе триггеров 14 и 15 хранится в течение всего переходного процесса, т.е. пока число , отражающее отклонение регулируемой величины, больше единицы.

Элементы И 16-18 сопоставляют информацию с выхода триггеров 14 и 15 с определенными значениями числа В, поступающего на вход элементов с выхода аналого-цифрового преобразователя и формируют величину отрицательного порога порогового элемента 4. Выходной сигнал каждого из элементов И 16-18 имеет определенный вес, пропорциональный проводимости выходного резистора соответствующего элемента. Через элемент ИЛИ 19 на один из положительных входов порогового элемента поступает сигнал, вес которого равен сумме весов тех элементов И 16-18, которые в данный момент имеют совпадение единичных сигналов на всех входах.

Таким образом, переменный отрицательный порог порогового элемента 4 выполняется в виде положительного входа с переменным весом, который определяется комбинацией сигналов на выходе элементов И 16-18 блока 9 изменения порога.

Формула изобретения

Цифровой регулятор давления, содержащий датчик сигнала рассогласования и релейный усилитель, отличающийся тем, что, с целью увеличения точности регулятора, в него введены аналого-цифровой преобразователь, элемент задержки, пороговый элемент, блок формирования знака и последовательно соединенные дещифратор, блок памяти и блок изменения порога, причем выход датчика сигнала рассогласования соединен с входом аналого-цифрового преобразователя, выход которого соединен с входом элемента задержки, входом дещифратора и

с первыми входами порогового элемента и блока формирования знака, выход которого соединен с входом релейного усилителя, а второй вход - с выходом порогового элемента, второй вход которого соединен с

выходом элемента задержки, а третий вход - с выходом блока изменения порога.

Источники информации, принятые во внимание при экспертизе

Фиг.1

, м ю

ю

(со |вэ 00

«М (j

IM

- ем ю

CQ CQ ео ао

Авторы

Даты

1981-02-28—Публикация

1979-05-17—Подача