(54) УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭЛЕКТРОННЫХ ВЫЧИСЛИТЕЛЬНЫХ МАШИН

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для программного сопряжения электронных вычислительных машин | 1976 |

|

SU641434A1 |

| Устройство для ввода измерительной информации | 1986 |

|

SU1354179A1 |

| Устройство для контроля последовательности байтов данных дисковой памяти | 1985 |

|

SU1315979A1 |

| Устройство для сопряжения ЭВМ с внешними устройствами | 1986 |

|

SU1396147A1 |

| Устройство для сопряжения вычислительнойМАшиНы C ТЕРМиНАлАМи | 1979 |

|

SU798786A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство для сопряжения ЭВМ с абонентами | 1985 |

|

SU1305698A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1553978A1 |

| Устройство для формирования управляющей информации при обработке данных сейсмических колебаний | 1981 |

|

SU1000766A1 |

| Устройство для распаковки команд | 1990 |

|

SU1702367A1 |

1

Изобретение относится к вычислительной технике и может быть использовано для программного сопряжения электронных вычислительных машин (ЭВМ) в многомашинных вычислительных системах.

Известны устройства для сопряжения ЭВМ, содержашие блок селекции, блок синхронизации, блок оперативной памяти и блок буферной памяти 1.

Недостатки этих устройств - большая трудоемкость подготовки данных и программ и низкое быстродействие вследствие ограниченных их функциональных возможностей.

Наиболее близким к предлагаемому является устройство для программного сопряжения электронных вычислительных машин, содержащее блок селекции, блок синхронизации, блок оперативной памяти и блок буферной памяти, блок преобразования числовой информации и блок преобразованизя командной информации, первые входы которых соединены со вторыми выходами блока буферной памяти, а выходы соединены соответственно со вторым и третьим входами блока буферной памяти, второй вход блока преобразования

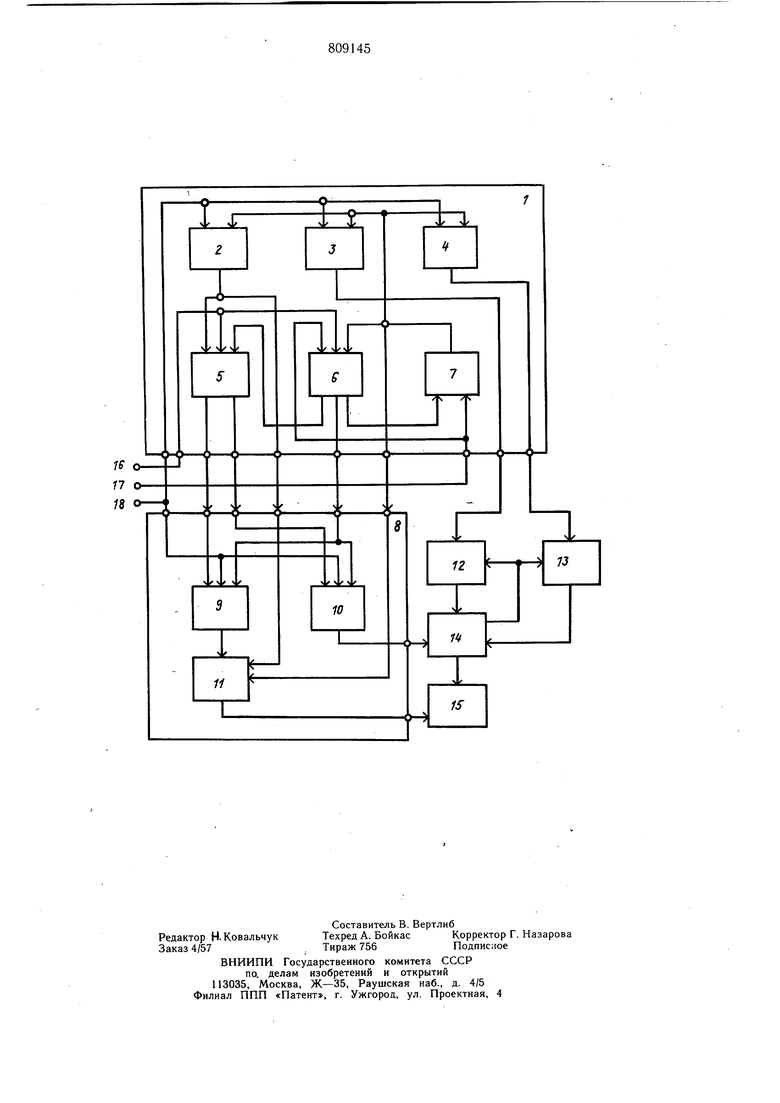

числовЬй информации подключен к пятому выходу блока селекции, шестой выход которого связан со вторым входом блока преобразования командной информации, причем первый, второй, третий и четвертый выходы 5 блока селекции соответственно подключены к первому, второму, третьему и четвертому входам блока синхронизации, пятый и шестой входы которого подключены соответственно к первому и второму входам блока селекции и информационному и управляющему входам устройства, первый и второй выходы блока синхронизации соединены соответственно с адресным входом блока оперативной памяти и первым входов блока буферной памяти, первый выход которого подключен к информационному входу блока оперативной памяти, блок преобразования числовой информации содержит дешифратор, первый и второй входы которого соединены соответственно с первым и вторым вхадами блока, управления, соединенный первым входом с дешифратором, схему сравнения, соединенную первым выходом с третьим входом дешифратора и вторым в.ходом узла управления, память констант, соединенную входом с первым выходом yj.u управления, а первым выходом - с первым входом схемы сравнения, второй вход которой подключен к первому входу блока, сумматор, подключенный тремя входами соответственно ко второму выходу схемы сравнения, второму выходу памяти констант и первому выходу узла управления, второй выход которого и выход сумматора подключены соответственно к входам группы элементов И, соединенной выходом с выходом блока. Блок преобразования командной информации содержит схему сравнения, узел управления, счетчик модификаторов, память команд и два элемента И, причем первый и второй входы схемы сравнения соединены соответственно с первым входом блока и первым выходом счетчика модификаторов, второй выход которого соединен с первым входом первого элемента И, выход схему сравнения соединен с входом узла управления, первый и второй выходы которого подключены соответственно ко входу счетчика модификаторов и второму входу первого элемента И, вход и выход памяти команд соединены соответственно с выходом первого элемента И и первым входом второго элемента И, второй вход и выход которого подключен соответственно со вторым входом и выходом блока. Блок селекции содержит дешифратор признака команд, дешифратор признака конца массива, дешифратор начального адреса и дешифратор признака числовой информации, первый и второй входы которых соединены соответственно с первым и вторым входом блока, два элемента ИЛИ и два триггера, первые входы которых и четвертый выход блока поДключены к выходу дешифратора признаков конца массива, второй вход первого триггера соединен с выходом первого элемента ИЛИ, а выход соединен с первым выходом блока, второй и третий выходы которого подключены соответственно к выходам второго триггера и второго элемента ИЛИ, первые входы элементов ИЛИ соединены с выходом дешифратора признака команд и шестым выходом блока, а их вторые входы подключены к выходу дешифратора признаков числовой информации и пятому входу блока, третий вход второго элемента ИЛИ и второй вход второго триггера связаны с выходом дешифратора начального адреса. Кроме того блок синхронизации содержит элемент И, первую группу элементов И, первые входы которых соответственно соединены с первым и вторымвходами блока, а выходы - с первым и вторым входами счетчика Адреса, подключенного выходом к первому выходу блока, второй вход первого элемента И подключен к выходу счетчика, вход которого соединен с шестым входом блока и первым входом тактового распределителя, подключенного вторым и третьим входами соответственно к третьему и четвертому входам блока, выход тактового распределителя соединен с первым входом второй группы элементов И, второй вход которых соединен со вторым входо.м первой группы элементов И и пятым входом блока, третий вход первой группы элементов И соединен с первым входом второй группы элементов И, выход которых связан со вторым выходом блока 2. Недостатки известного устройства - низкое быстродействие, связанное с необходимостью ввода и последующего анализа после каждого слова данных байта признака конца массива, и сложность, требуюшая значительных затрат оборудования. Цель изобретения - сокращение аппаратурных затрат и увеличение пропускной способности устройства. Поставленная цель достигается тем, что в блок управления устройства, содержащего блок управления, включающий дещифратор признака начального адреса, дешифратор признаков командной информации, дешифратор признаков числовой информации, первые входы которых соединены с информационным входом устройства, и триггер, первым входом соединенный с выходом дешифратора признака начального адреса, блок формирования адреса, включающий две группы элементов И и счетчик адреса, блок преобразования командной информации и блок преобразования числовой информации, первые входы которых соединены соответственно с выходами дешифратора признаков командной информации и дещифратора признаков числовой информации, вторые входы - С первым выходом блока буферной памяти, а выходы - соответственно с первым и вторым входами блока буферной памяти, второй выход которого подключен к первому входу блока оперативной памяти, вторым входом соединенного с выходом счетчика адреса, группа входов которого подключена к выходам элементов И первой группы, первые входы которых соединены с первым выходом триггера, а вторые входы - с информационным входом устройства и первыми входами элементов И второй группы, выходами подключенных к группе входов блока буферной памяти, введены регистр сдвигов и элемент И, причем первые входы регистра сдвигов и элемента И соединены со входом синхронизации устройства, вторые входы регистра сдвигов и триггера подключены ко входу установки устройства, выход элемента И соединен со вторыми входами дещифратора признака начального адреса, дешифратора признаков командной информации, дешифратора признаков числовой информации, первым входом счетчика адреса и третьим входом регистра сдвигов, первый выход которого соединен со вторым входом элемента И, второй выход - со вторыми входами элементов И второй группы и третьими входами элементов И первой группы, а третий выход - с третьим входом триггера, первый вход и второй выход которого соединены соответственно со вторым входом счетчика адреса и третьими входами элементов И второй группы. На чертеже представлена блок-схема устройства. Схема содержит блок 1 управления в составе дешифратора 2 признака начального адреса, дешифратора 3 признаков командной информации, дешифратора 4 признаков числовой информации, триггера 5, регистра 6 сдвигов и элемента И 7, блока 8 формирования адреса в составе элементов И 9 первой группы элементов И 10 второй группы и счетчика 11 адреса, блок 12 преобразования командной информации, блок 13 преобразования числовой информации, блок 14 буферной памяти, блок 15 оперативной памяти, вход 16 установки устройства, вход 17 синхронизации устройства и информационный вхоД 18 устройства. Устройство работает следуюшим образом. Сопряжение осуществляется ЭВМ типов «Наири-2 (ЭВМ-1) и «Минск-222 (ЭВМ-г). Вся информация в виде команд, чисел и начальных адресов размещения их массивов задана на восьмидорожечной перфоленте, подготовленной на ЭВМ-1. Каждое полноразрядное слово информации (т.е. команда, адрес или число) на перфоленте представлено несколькими байтами информации и сопровождается байтом признака информации. Работа начинается с начальной установки в ноль триггера 5 и регистра б по входу 16. Затем с перфоленты побайтно вводится начальный адрес массива данных. Порядок поступления данных следующий. Перед маесивом вводится кодовый сигнал начального адреса массива данных,а за ним побайтно вводится и на счетчике 11 формируется сам начальный адрес. После начального адреса поступает массив команд и массив чисел, причем каждая команда и каждое число вводится побайтно, пословно формируется в блоке 14, преобразуется в блоке 12 или в блоке 13 и пересылается через блок 14 буферной памяти в блок 15 оперативной памяти в ячейки, адреса которых формируются на счетчике 11 адреса. Признаки начального адреса, командной и числовой информации дешифрируются в блоке 1 управления соответствующими дешифраторами. Управление, формирование и преобразование адресной, числовой и командной информации производится следующим образом. Поступающий по входу 18 сигнал начального адреса массива данных дешифрируется на дешифраторе 2 признака начального адреса, сигнал с выхода которого устанавливает в нулевое состояние, счетчик 11 и в единичное состояние триггер 5, который отпирает элементы И 9 и запирает элементы И 10 на время поступления начального адреса. Информация, поступающая побайтно по входу 18 сопровождается синхроимпульсами по входу 17. Фазы поступления кодовой информации и стробирующих ее управляющих импульсов строго одинаковы. Стробирующие синхроимпульсы производят сдвиг логической единицы по разрядам регистра 6 сдвигов, поочередно открывая соответствующие элементы И 9 и И 10, на соответствующие входы которых побайтно поступает информация начального адреса. Значение начального адреса формируется в счетчике 11 путем побайтной записи информации от элементов И 9. Количество байтов слова определяется состоянием регистра 6. Конец слова определяется сигналом перехода старшего разряда регистра сдвига из единичного состояния в нулевое. Этим сигналом триггер 5 устанавливается в нулевое состояние и отпирает элементы И 10 и запирает элементы И 9. В нулево.и состоянии регистр.6 сдвига сигналами с нулевых выходов открывает элемент И 7 и тем самым разрешает прохождение синхронизирующего импульса на дешифрацию следующего байта информации, являющегося признаком информации, на счетный вход счетчика 11 адреса, и на установку в единичное состояние младшего разряда регистра 6 сдвигов. После приема начального адреса по входу 18 поступает признак командной или числовой информации. Признак командной информации расшифровывает дешифратор 3 и выделяет на выходе сигнал для блока 12. Признак числовой информации расшифровывает дешифратор 4 и выделяет на выходе сигнал для блока 13. Прием и упаковка числовой и командной информации производится через блок 8 в блоке буферной памяти. Процесс приема и упаковки числовой и командной информации заключается в том, что побайтно поступающая информация распределяется с помощью регистра 6 сдвигов в блоке 1 и с помощью элементов И 10 в блоке 8, записывается в бло1 14 буферной памяти, представляющей регистр памяти на триггерах. Процесс распределения аналогичен распределению байтов начальной адресной информации в счетчике 11 адреса. Регистр сдвига поочередно разрешает прохождение поступающей на -входы элементов И 10 информации на входы соответствующих разрядов блока 14. Разрядность регистра 6 сдвигов выбирается с учетом разрядности блока 14 буферной памяти и разрядности одновременно поступающей информации. Например, при разрядности ЭВМ-2 32 бита и побайтно поступающей информации разрядность регистра сдвигов равна четырем разрядам. В связи с тем, что добавление единицы в счетчике 11 адреса производится при анализе признака информации, начальный адрес массива на перфоленте задается на единицу меньше действительного. Таким образом, устройство обеспечивает сопряжение двух ЭВМ при сокращенном объеме оборудования более высоким (по сравнению с известным устройством) быстродействием. Формула изобретения Устройство для сопряжения электронных вычислительных машин, содержащее блок управления, включающий дешифратор признака начального адреса, дешифратор признаков командной информации, дешифратор признаков числовой информации, первые входы которых соединены с информационным входом устройства, и триггер, первым входом соединенный с выходом дешифратора признака начального адреса, блок формирования адреса, включающий две группы элементов И и счетчик адреса, блок преобразования командной информации и блок преобразования числовой информации, первце входы которых соединены соответ ственно с выходами дешифратора признаков командной информации и дешифратора признаков числовой информации, вторые входы - с первым выходом .блока буферной памяти, а выходы - соответственно с первым и вторым входами блока буферной памяти, второй выход которого подключен к первому входу блока оперативной памяти, вторым входом соединенного с выходом счетчика адреса, группа входов которого подключена к выходам элементов И первой группы, первые входы которых соединены с первым выходом триггера, а вторые входы - с информационным входом устройства и первыми входами элементов И второй группы, выходами падключенными к группе входов блока буферной цамяти, отличающееся тем, что, с целью сокращения аппаратурных затрат, в блок управления устройства введены регистр сдвигов и элемент И, причем первые входы регистра сдвигов и элемента И соединены со входом синхронизации устройства, вторые входы регистра сдвигов и триггера подключены ко входу установки устройства, выход элемента И соединен со вторыми входами дешифратора признака начального адреса, дешифратора признаков командной информации, дешифратора признаков числовой информации, первым входом счетчика адреса и третьим входом регистра сдвигов, первый выход которого соединен со вторым входом элемента И, второй выход - со вторыми входами элементов И второй группы и третьими входами элементов И первой группы, а третий выход - с третьим входом триггера, первый вход и второй выход которого соединены соответственно со вторым входом счетчика адреса и третьими входами элементов И второй группы. Источники информации, принятые во внимание при экспертизе 1.Патент Франции № 2261568, кл. G 06 F 15/16, опублик. 1975. 2.Авторское свидетельство СССР № 641434, кл. G 06 F 3/04, 1976 (прототип).

Авторы

Даты

1981-02-28—Публикация

1979-05-16—Подача