S

Ё

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для тестового контроля цифровых блоков | 1986 |

|

SU1345199A2 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1425680A2 |

| Устройство для тестового контроля цифровых блоков | 1984 |

|

SU1251084A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1539782A2 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1430957A2 |

| Устройство для тестового контроля цифровых блоков | 1985 |

|

SU1312577A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1314344A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1545222A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при контроле цифровых блоков. Цель изобретения - повышение быстродействия. Устройство содержит блок 9 микропрограммного управления, блок обмена 10 с контролируемым блоком, счетчик 2 логических номеров, блок памяти 4, буферный блок памяти 5, регистр набора 3, выходной коммутатор 7, регистр сдвига 8, буферный регистр 1. 1 з.п. ф-лы, 8 ил.

СЛ СП

СО

со 1

оо

Изобретение относится к вычислительной технике и может быть использовано при диагностике цифровых блоков.

Цель изобретения - повышение быстродействия.

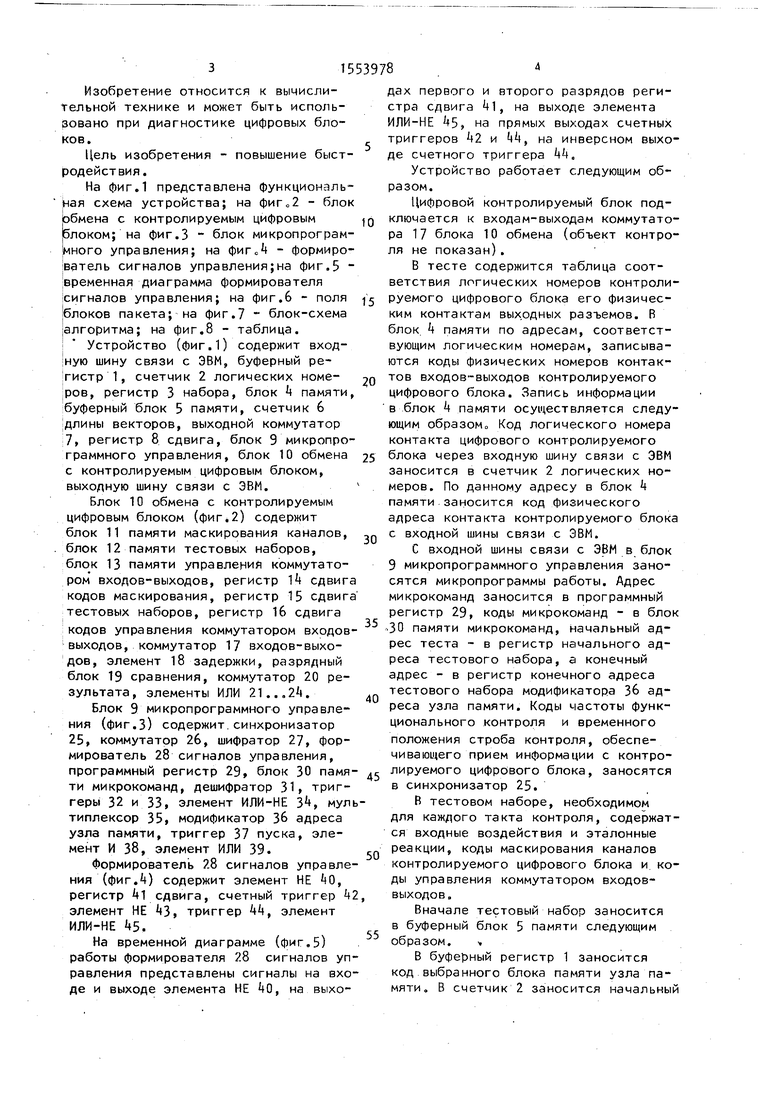

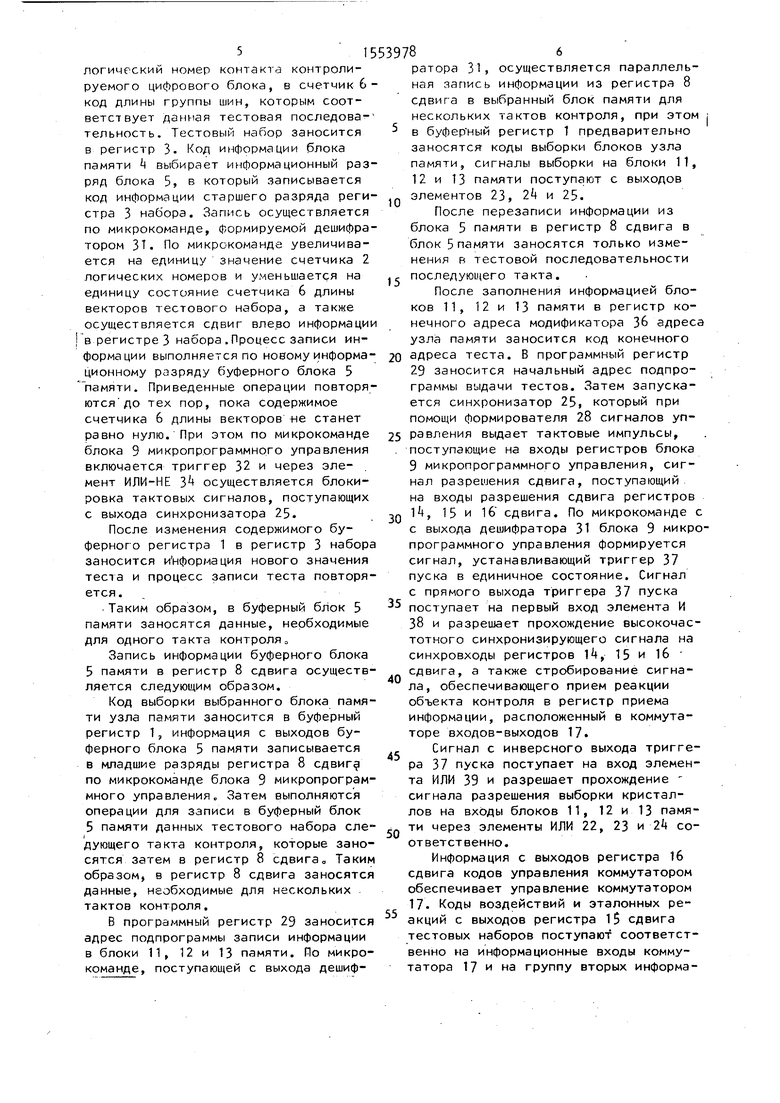

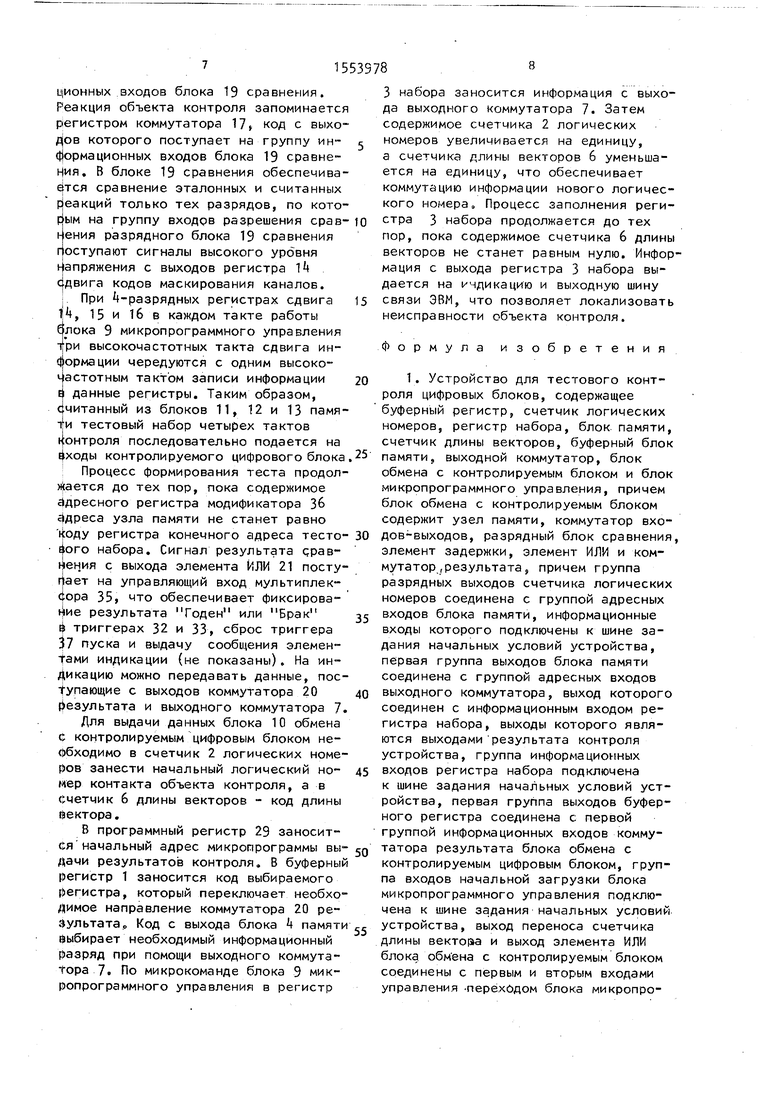

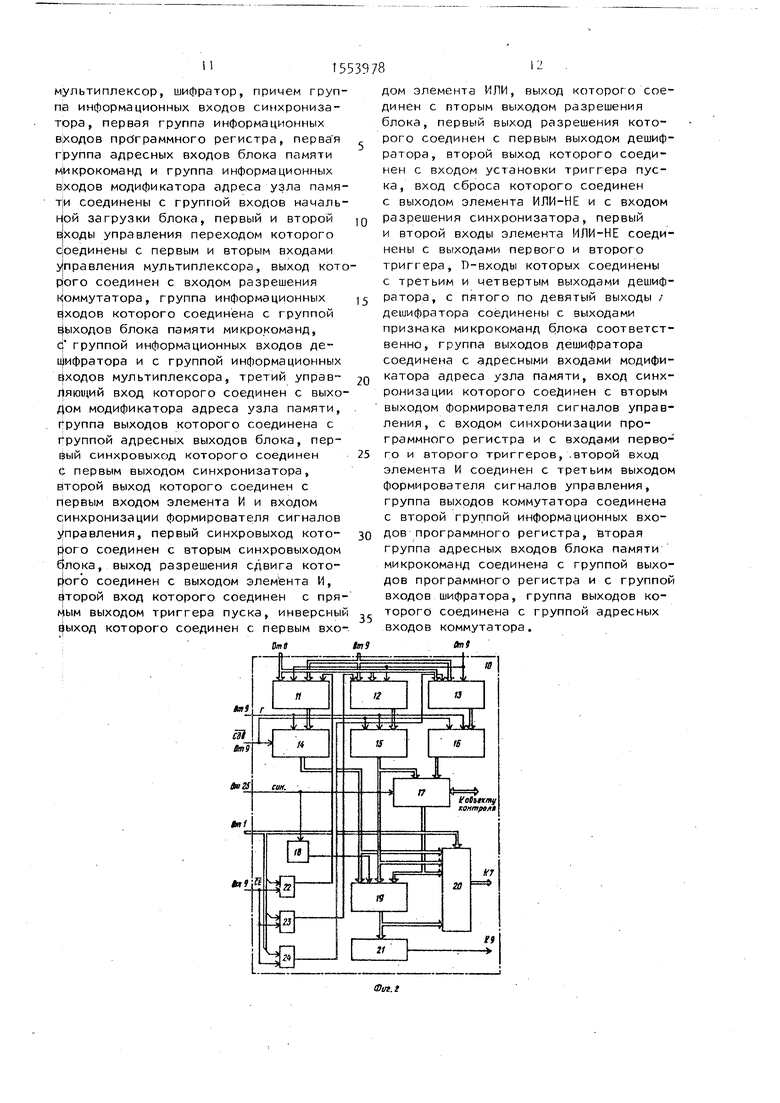

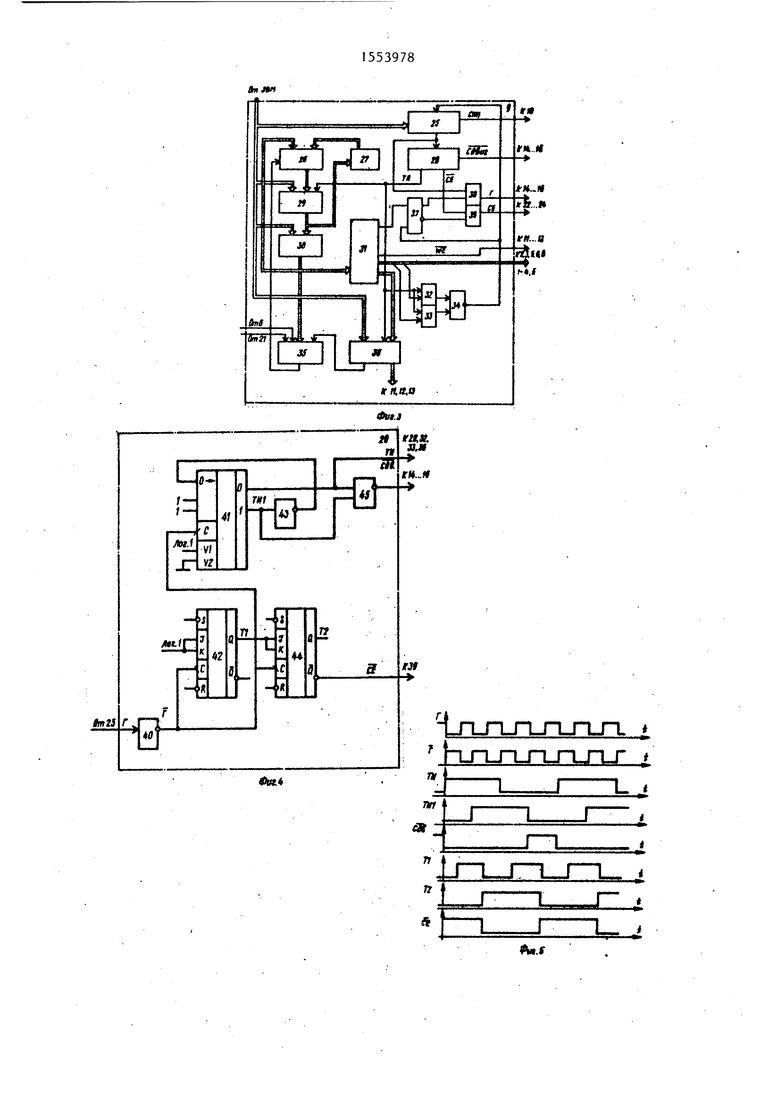

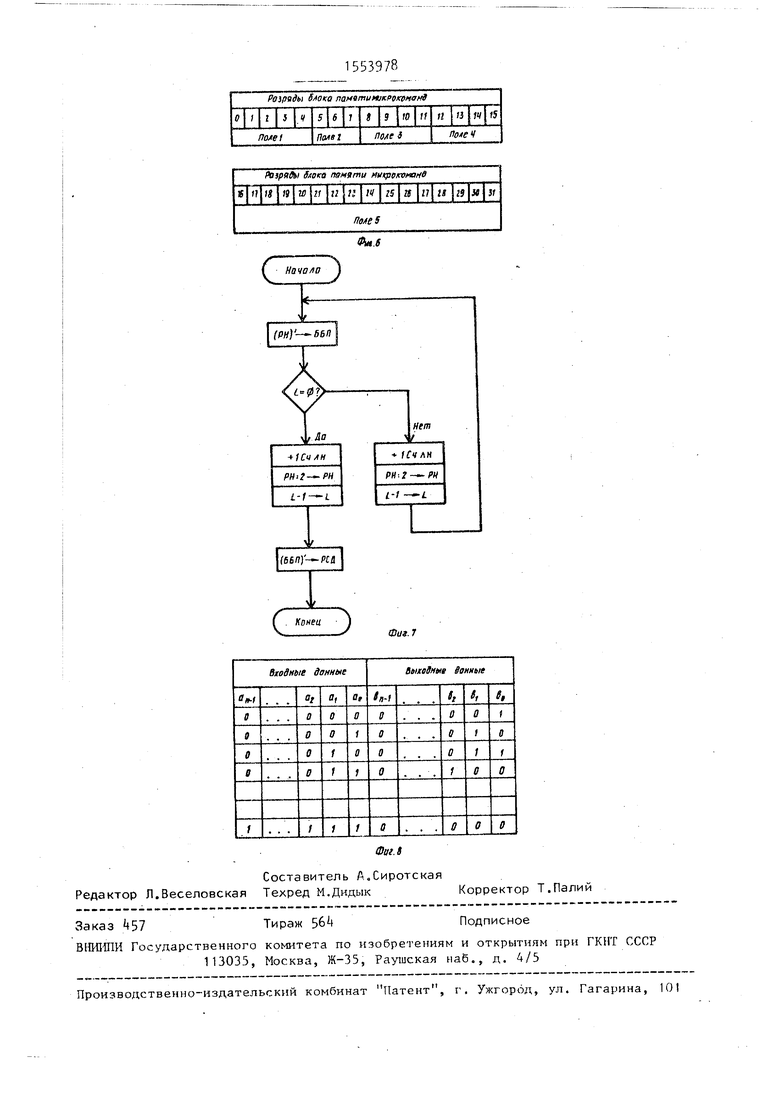

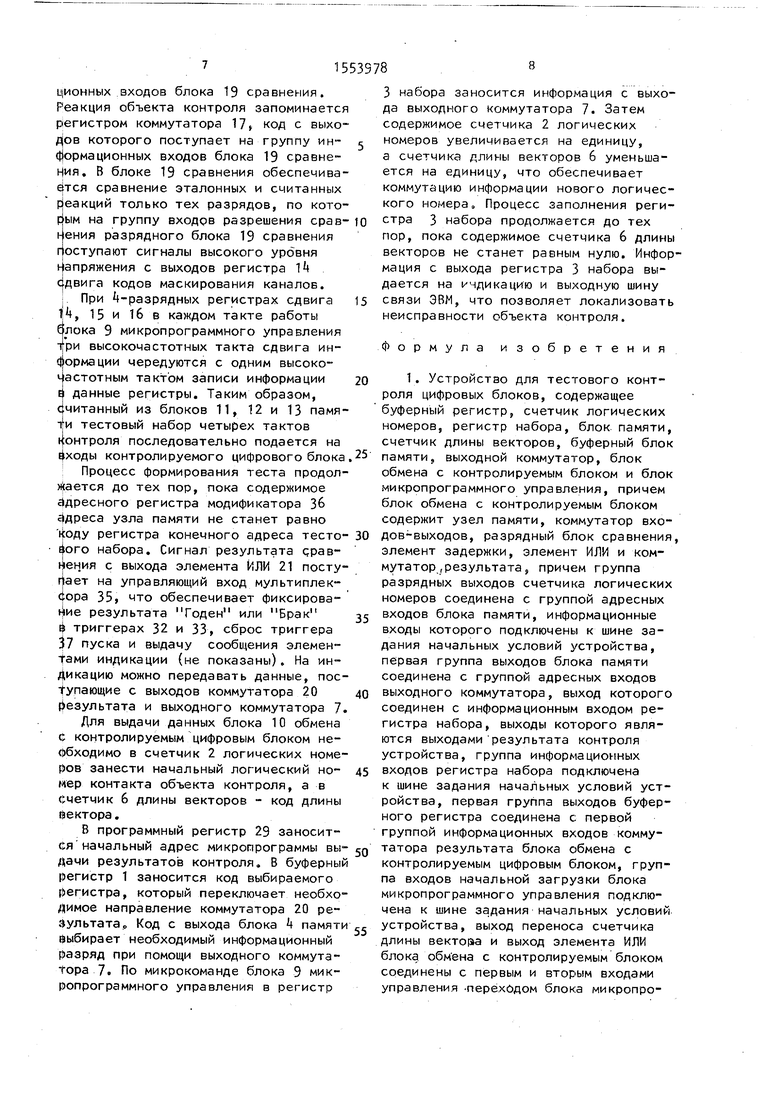

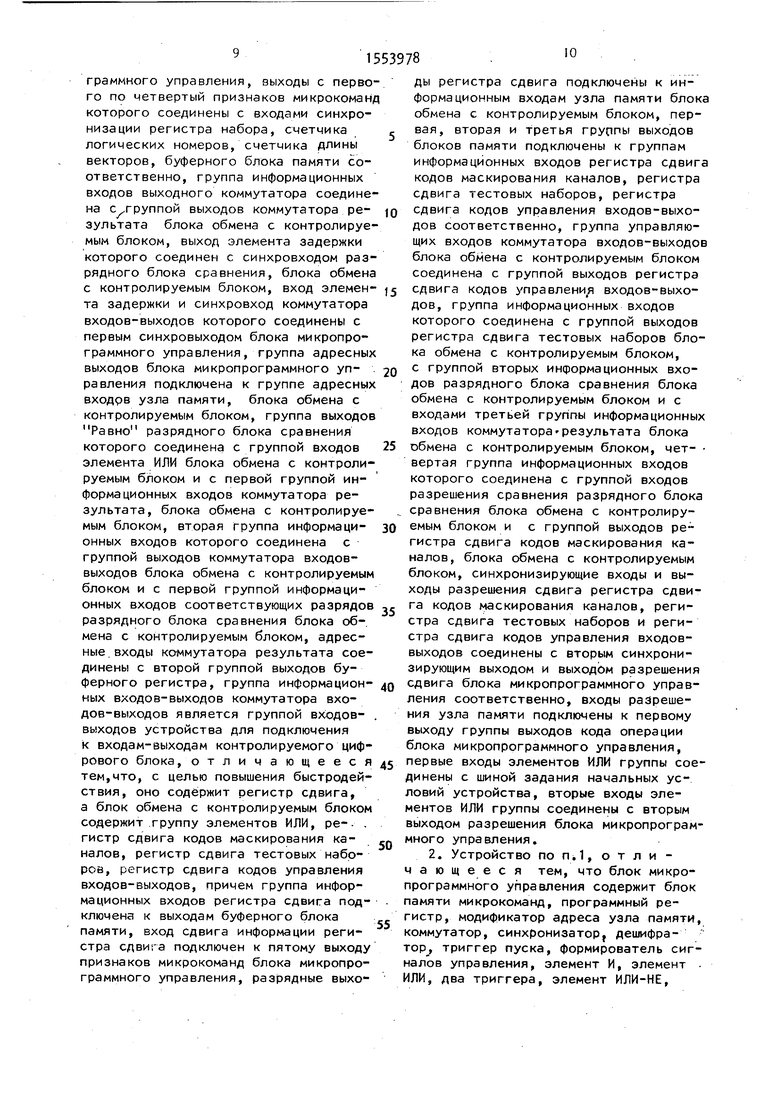

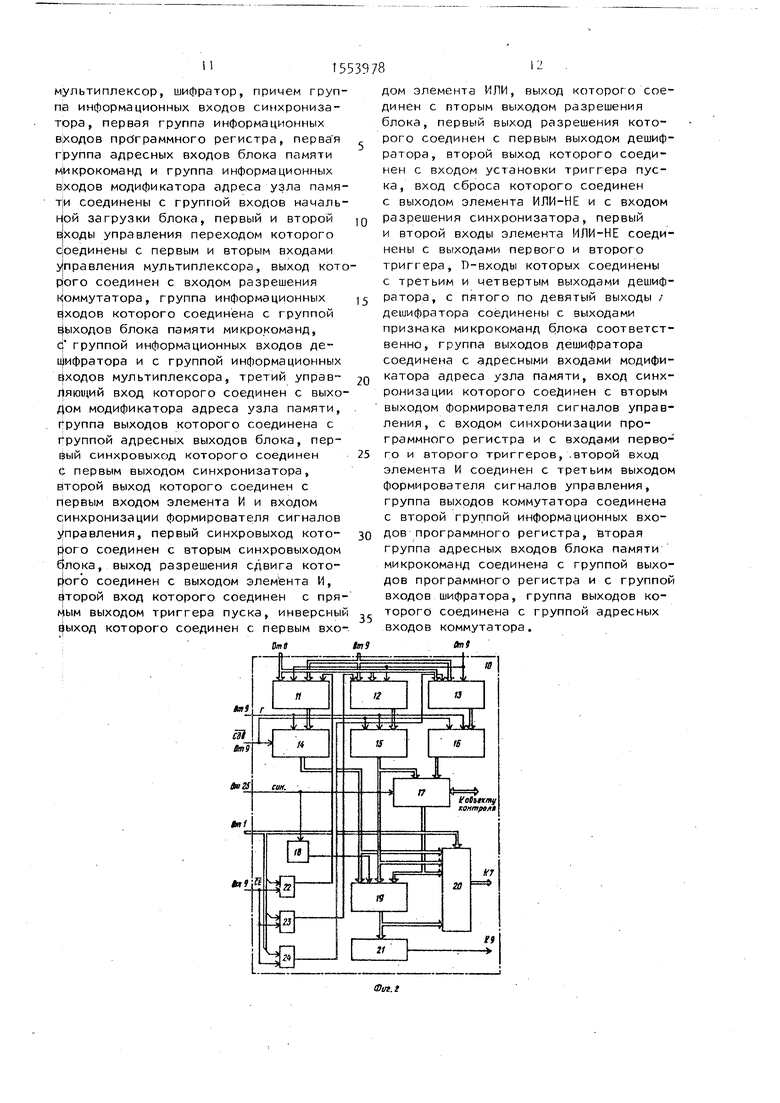

На фиг.1 представлена функциональная схема устройства; на фиг„2 - блок обмена с контролируемым цифровым блоком; на фиг.З - блок микропрограммного управления; на фиг04 - формирователь сигналов управления;на фиг.5 временная диаграмма формирователя сигналов управления; на фиг.6 - поля блоков пакета; на фиг.7 блок-схема лгоритма; на фиг.8 - таблица.

Устройство (фиг.1) содержит входную шину связи с ЭВМ, буферный регистр 1, счетчик 2 логических номеров, регистр 3 набора, блок 4 памяти, буферный блок 5 памяти, счетчик 6 длины векторов, выходной коммутатор 7, регистр 8 сдвига, блок 9 микропрограммного управления, блок 10 обмена с контролируемым цифровым блоком, выходную шину связи с ЭВМ.

Блок 10 обмена с контролируемым цифровым блоком (фиг.2) содержит блок 11 памяти маскирования каналов, блок 12 памяти тестовых наборов, блок 13 памяти управлений коммутатором входов-выходов, регистр 14 сдвига кодов маскирования, регистр 15 сдвига тестовых наборов, регистр 16 сдвига кодов управления коммутатором входов- выходов, коммутатор 17 входов-выходов, элемент 18 задержки, разрядный блок 19 сравнения, коммутатор 20 результата, элементы ИЛИ 21...24.

Блок 9 микропрограммного управления (фиг.З) содержит синхронизатор 25, коммутатор 26, шифратор 27, формирователь 28 сигналов управления, программный регистр 29, блок 30 памя- ти микрокоманд, дешифратор 31, триггеры 32 и 33, элемент ИЛИ-НЕ 34, мультиплексор 35, модификатор 36 адреса узла памяти, триггер 37 пуска, элемент И 38, элемент ИЛИ 39.

Формирователь 28 сигналов управления (фиг.4) содержит элемент НЕ 40, регистр 41 сдвига, счетный триггер 42 элемент НЕ 43, триггер 44, элемент ИЛИ-НЕ 45.

На временной диаграмме (фиг.5) работы формирователя 28 сигналов управления представлены сигналы на входе и выходе элемента НЕ 40, на выхо

0

0

25

45 50

,

30

35

40

55

дах первого и второго разрядов регистра сдвига 41, на выходе элемента ИЛИ-НЕ 45, на прямых выходах счетных триггеров 42 и 4, на инверсном выходе счетного триггера 44,

Устройство работает следующим образом.

Цифровой контролируемый блок подключается к входам-выходам коммутатора 17 блока 10 обмена (объект контроля не показан).

В тесте содержится таблица соответствия логических номеров контролируемого цифрового блока его физическим контактам выходных разъемов. В блок 4 памяти по адресам, соответствующим логическим номерам, записываются коды физических номеров контактов входов-выходов контролируемого цифрового блока. Запись информации в блок 4 памяти осуществляется следующим образом Код логического номера контакта цифрового контролируемого блока через входную шину связи с ЭВМ заносится в счетчик 2 логических номеров. По данному адресу в блок 4 памяти заносится код физического адреса контакта контролируемого блока с входной шины связи с ЭВМ.

С входной шины связи с ЭВМ в блок 9 микропрограммного управления заносятся микропрограммы работы. Адрес микрокоманд заносится в программный регистр 29, коды микрокоманд - в блок 30 памяти микрокоманд, начальный адрес теста - в регистр начального адреса тестового набора, а конечный адрес - в регистр конечного адреса тестового набора модификатора 36 адреса узла памяти. Коды частоты функционального контроля и временного положения строба контроля, обеспечивающего прием информации с контролируемого цифрового блока, заносятся в синхронизатор 25.

В тестовом наборе, необходимом для каждого такта контроля, содержатся входные воздействия и эталонные реакции, коды маскирования каналов контролируемого цифрового блока и коды управления коммутатором входов- выходов.

Вначале тестовый набор заносится в буферный блок 5 памяти следующим образом.

В буферный регистр 1 заносится код выбранного блока памяти узла памяти. В счетчик 2 заносится начальный

логический номер контакта контролируемого цифрового блока, в счетчик 6 - код длины группы шин, которым соответствует данная тестовая последова- тельность. Тестовый набор заносится в регистр 3. Код информации блока памяти 4 выбирает информационный разряд блока 5, в который записывается код информации старшего разряда регистра 3 набора. Запись осуществляется по микрокоманде, формируемой дешифратором 31. По микрокоманде увеличивается на единицу значение счетчика 2 логических номеров и уменьшается на единицу состояние счетчика 6 длины векторов тестового набора, а также осуществляется сдвиг влево информации в регистре 3 набора.Процесс записи информации выполняется по новому информационному разряду буферного блока 5 памяти. Приведенные операции повторяются до тех пор, пока содержимое счетчика 6 длины векторов +ie станет равно нулю. При этом по микрокоманде блока 9 микропрограммного управления включается триггер 32 и через элемент ИЛИ-НЕ 3 осуществляется блокировка тактовых сигналов, поступающих с выхода синхронизатора 25.

После изменения содержимого буферного регистра 1 в регистр 3 набора заносится информация нового значения теста и процесс записи теста повторяется .

Таким образом, в буферный блок 5 памяти заносятся данные, необходимые для одного такта контроля„

Запись информации буферного блока 5 памяти в регистр 8 сдвига осуществляется следующим образом.

Код выборки выбранного блока памяти узла памяти заносится в буферный регистр 1, информация с выходов буферного блока 5 памяти записывается в младшие разряды регистра 8 сдвига по микрокоманде блока 9 микропрограммного управления. Затем выполняются операции для записи в буферный блок

Сигнал с инверсного выхода триггера 37 пуска поступает на вход элемента ИЛИ 39 и разрешает прохождение - сигнала разрешения выборки кристаллов на входы блоков 11, 12 и 13 памя5 памяти данных тестового набора еле- 5Q ти через элементы ИЛИ 22, 23 и 2h coдующего такта контроля, которые заносятся затем в регистр 8 сдвига„ Таким образом в регистр 8 сдвига заносятся данные, необходимые для нескольких тактов контроля.

В программный регистр 29 заносится адрес подпрограммы записи информации в блоки 11, 12 и 13 памяти. По микрокоманде, поступающей с выхода дешифответственно.

Информация с выходов регистра 16 сдвига кодов управления коммутатором обеспечивает управление коммутатором 17. Коды воздействий и эталонных реакций с выходов регистра 15 сдвига тестовых наборов поступают соответственно на информационные входы коммутатора 17 и на группу вторых информа0

5

ратора 31, осуществляется параллельная запись информации из регистра 8 сдвига в выбранный блок памяти для нескольких тактов контроля, при этом i в буферный регистр 1 предварительно заносятся коды выборки блоков узла памяти, сигналы выборки на блоки 11, 12 и 13 памяти поступают с выходов элементов 23, 2k и 25.

После перезаписи информации из блока 5 памяти в регистр 8 сдвига в блок 5 памяти заносятся только изменения в тестовой последовательности последующего такта.

После заполнения информацией блоков 11, 12 и 13 памяти в регистр конечного адреса модификатора 3& адреса узла памяти заносится код конечного

0 адреса теста. В программный регистр 29 заносится начальный адрес подпрограммы выдачи тестов. Затем запускается синхронизатор 25, который при помощи формирователя 28 сигналов уп5 равления выдает тактовые импульсы, поступающие на входы регистров блока 9 микропрограммного управления, сигнал разрешения сдвига, поступающий на входы разрешения сдвига регистров 1, 15 и 16 сдвига. По микрокоманде с с выхода дешифратора 31 блока 9 микропрограммного управления формируется сигнал, устанавливающий триггер 37 пуска в единичное состояние. Сигнал с прямого выхода триггера 37 пуска поступает на первый вход элемента И 38 и разрешает прохождение высокочастотного синхронизирующего сигнала на синхровходы регистров 14, 15 и 16 сдвига, а также стробирование сигнала, обеспечивающего прием реакции объекта контроля в регистр приема информации, расположенный в коммутаторе входов-выходов 17.

Сигнал с инверсного выхода триггера 37 пуска поступает на вход элемента ИЛИ 39 и разрешает прохождение - сигнала разрешения выборки кристаллов на входы блоков 11, 12 и 13 памя0

5

0

5

Q ти через элементы ИЛИ 22, 23 и 2h coответственно.

Информация с выходов регистра 16 сдвига кодов управления коммутатором обеспечивает управление коммутатором 17. Коды воздействий и эталонных реакций с выходов регистра 15 сдвига тестовых наборов поступают соответственно на информационные входы коммутатора 17 и на группу вторых информационных входов блока 19 сравнения. Реакция объекта контроля запоминается регистром коммутатора 17 код с выходов которого поступает на группу ин формационных входов блока 19 сравнения. В блоке 19 сравнения обеспечивается сравнение эталонных и считанных реакций только тех разрядов, по которым на группу входов разрешения срав- i-ения разрядного блока 19 сравнения поступают сигналы высокого уровня Напряжения с выходов регистра Ik 4двига кодов маскирования каналов.

При 4-разрядных регистрах сдвига ik, 15 и 16 в каждом такте работы блока 9 микропрограммного управления т|ри высокочастотных такта сдвига информации чередуются с одним высоко- i-астотным тактом записи информации Е данные регистры. Таким образом, считанный из блоков 11, 12 и 13 памяти тестовый набор четырех тактов онтроля последовательно подается на Йходы контролируемого цифрового блока

Процесс формирования теста продолжается до тех пор, пока содержимое Адресного регистра модификатора 36 Адреса узла памяти не станет равно коду регистра конечного адреса тесто- ioro набора. Сигнал результата сравнения с выхода элемента ИЛИ 21 поступает на управляющий вход мультиплексора 35, что обеспечивает фиксирование результата Годен или Брак К триггерах 32 и 33, сброс триггера 37 пуска и выдачу сообщения элементами индикации (не показаны). На ин- Дикацию можно передавать данные, поступающие с выходов коммутатора 20 результата и выходного коммутатора 7.

Для выдачи данных блока 10 обмена С контролируемым цифровым блоком не- | бходимо в счетчик 2 логических номеров занести начальный логический но- мер контакта объекта контроля, а в Счетчик 6 длины векторов - код длины вектора.

В программный регистр 29 заносится начальный адрес микропрограммы вы- дачи результатов контроля. В буферный регистр 1 заносится код выбираемого регистра, который переключает необходимое направление коммутатора 20 ре™ : ультата„ Код с выхода блока k памяти выбирает необходимый информационный разряд при помощи выходного коммутатора 7. По микрокоманде блока 9 микропрограммного управления в регистр

3 набора заносится информация с выхода выходного коммутатора 7. Затем содержимое счетчика 2 логических номеров увеличивается на единицу, а счетчика длины векторов 6 уменьшается на единицу, что обеспечивает коммутацию информации нового логического номера. Процесс заполнения регистра 3 набора продолжается до тех пор, пока содержимое счетчика 6 длины векторов не станет равным нулю. Информация с выхода регистра 3 набора выдается на индикацию и выходную шину связи ЭВМ, что позволяет локализовать неисправности объекта контроля.

Формула изобретения

5

0

5

0

5

0

5

0

5

ды регистра сдвига подключены к информационным входам узла памяти блока обмена с контролируемым блоком, первая, вторая и третья группы выходов блоков памяти подключены к группам информационных входов регистра сдвига кодов маскирования каналов, регистра сдвига тестовых наборов, регистра сдвига кодов управления входов-выходов соответственно, группа управляющих входов коммутатора входов-выходов блока обмена с контролируемым блоком соединена с группой выходов регистра сдвига кодов управления входов-выходов, группа информационных входов которого соединена с группой выходов регистра сдвига тестовых наборов блока обмена с контролируемым блоком, с группой вторых информационных входов разрядного блока сравнения блока обмена с контролируемым блоком и с входами третьей группы информационных входов коммутатора результата блока обмена с контролируемым блоком, чет- вертая группа информационных входов которого соединена с группой входов разрешения сравнения разрядного блока сравнения блока обмена с контролируемым блоком и с группой выходов регистра сдвига кодов маскирования каналов, блока обмена с контролируемым блоком, синхронизирующие входы и выходы разрешения сдвига регистра сдвига кодов маскирования каналов, регистра сдвига тестовых наборов и регистра сдвига кодов управления входов- выходов соединены с вторым синхронизирующим выходом и выходом разрешения сдвига блока микропрограммного управления соответственно, входы разрешения узла памяти подключены к первому выходу группы выходов кода операции блока микропрограммного управления, первые входы элементов ИЛИ группы соединены с шиной задания начальных условий устройства, вторые входы элементов ИЛИ группы соединены с вторым выходом разрешения блока микропрограм- мног о уп ра вл ения.

мультиплексор, шифратор, причем группа информационных входов синхронизатора, первая группа информационных входов программного регистра, перва я группа адресных входов блока памяти микрокоманд и группа информационных входов модификатора адреса узла памяти соединены с группой входов начальной загрузки блока, первый и второй Е)ходы управления переходом которого Соединены с первым и вторым входами правления мультиплексора, выход которого соединен с входом разрешения Коммутатора, группа информационных уходов которого соединена с группой в ыходов блока памяти микрокоманд, d группой информационных входов де- Шифратора и с группой информационных Входов мультиплексора, третий управляющий вход которого соединен с выходом модификатора адреса узла памяти, группа выходов которого соединена с группой адресных выходов блока, первый синхровыход которого соединен С первым выходом синхронизатора, второй выход которого соединен с Первым входом элемента И и входом синхронизации формирователя сигналов управления, первый синхровыход которого соединен с вторым синхровыходом б;лока, выход разрешения сдвига которого соединен с выходом элемента И, второй вход которого соединен с прямым выходом триггера пуска, инверсный йыход которого соединен с первым вхоПтв

tali

т

О

5

S

0

5

0

35

дом элемента ИЛИ, выход которого соединен с вторым выходом разрешения блока, первый выход разрешения кото рого соединен с первым выходом дешифратора, второй выход которого соединен с входом установки триггера пуска, вход сброса которого соединен с выходом элемента ИЛИ-НЕ и с входом разрешения синхронизатора, первый и второй входы элемента ИЛИ-НЕ соединены с выходами первого и второго триггера, D-входы которых соединены с третьим и четвертым выходами дешифратора, с пятого по девятый выходы / дешифратора соединены с выходами признака микрокоманд блока соответственно, группа выходов дешифратора соединена с адресными входами модификатора адреса узла памяти, вход синхронизации которого соединен с вторым выходом формирователя сигналов управления, с входом синхронизации программного регистра и с входами первого и второго триггеров, второй вход элемента И соединен с третьим выходом формирователя сигналов управления, группа выходов коммутатора соединена с второй группой информационных входов программного регистра, вторая группа адресных входов блока памяти микрокоманд соединена с группой выходов программного регистра и с группой входов шифратора, группа выходов которого соединена с группой адресных входов коммутатора. «л

Г

Р0)ря0ы SAOKQ пвмяти Мифекотмв

1 I { IH 15

Фиг 7

| Устройство тестового контроля | 1982 |

|

SU1075265A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для тестового контроля цифровых блоков | 1984 |

|

SU1251084A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-03-30—Публикация

1987-10-06—Подача