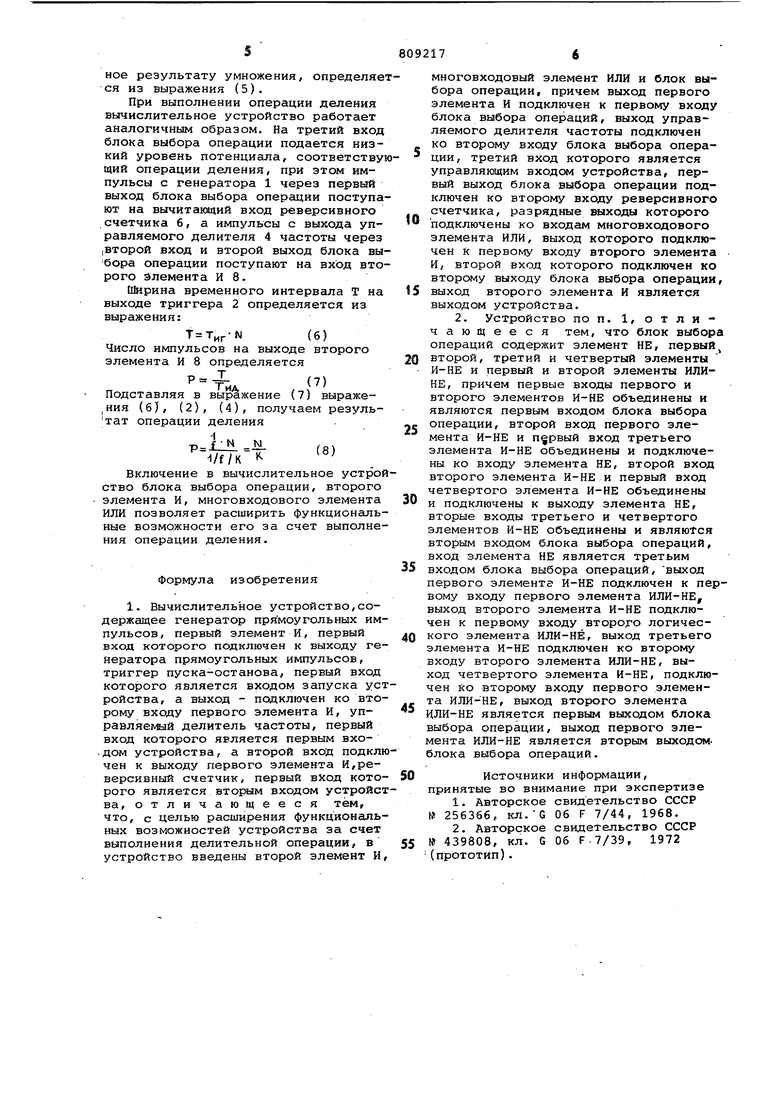

Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных при борах, устройствах для умножения чис ла импульсов на какое-либо число, в регуляторах с импульсными входами. Известно множительное устройство число-импульсйого типа, содержащее генератор прямоугольных импульсов, триггер, ynpaeiMtewtrt делитель частоты, счетчики, о знованиые на преобразовании исходного числа импульсов во временной интервал, длительность которого пропорциональна произведению исходного числа ИМПУЛЬСОВ на заданное число til. Недостатком устройства является то, что оно не обеспечивает операции деления числа импульсов на какое-либо число, т.е. имеет коэффициент умножейия с ограниченным диапазоном (от единицы и выше). Наиболее близким к предлаг.аемому является вычислительное устройство, содержащее генератор прямоугольных импульсов, первый элемент И, первый вход которого подключен к выходу генератсч а прямоугольных импульсов, 1триггер пуска-останова, первый вхсзд которого является входом запуска уст ройства, а выход подключен ко вто- , рому входу первого элемента И, управляемый делитель частоты, первый вход которого является первым входом устройства, а второй вход подключен к выходу первого элемента И, реверсивный счетчик, первый вход которого явлйется вторым входом устройства 121. Основным недостатком известного устройства является то, что при существующем наличии аппаратурных затрат оно позволяет выполнять только одну операцию - умножение исходного числа импульсов на какое-либо число, в то время, как для широкого круга задач возникает необходимость выполнения операций и умножения, н деления, т.е. - необходимость в устройстве с коэффициентом умножения, изменяющимся в диапазоне от нуля до бесконечности. Цепь изобретения - расширение функциональных возможностей устройства, за счет выполнения делительной операции. Поставленная цель достнгается тем, что в устройство введены второй , элемент И, многовходовый элемент ИЛИ и блок выбора операций,при-чем выход первого элейента И подключен к первому входу блока выбора операций, выход управляемого делителя частоты подключен ко второму входу блока выбора операции, третий вход которого является управляющим входом устройства, первый выход блока выбора операции подзшючен ко BTopof входу реверсивного счетчика, разрядные выходы которого подключены ко входам многовходового элемента ИЛИ, выход которого подключен к первому входу второго элемента И, второй вход которого подключен ко второму выходу блока выбора операции выход второго элемента И является выходом устройства. Блок выбора опера:ции содержит элемент НЕ, первый, вто;рой, третий и четвертый элементы И:НЕ и первый и второй элементы ИЛИНЕ, причем первые входы первого и второго элементов И-НЕ объединены и являются первым входом блока выбора операции, второй вход первого элемента И-ИЕ и первый вход третьего элемента И-НЕ объединены и полключевы ко входу элемента НЕ, второй вход второго элемента И-НЕ и первый вход четвертого элемента И-НЕ объединены и подключены к выходу элемента НЕ, вторые входы третьего и четвертого элементов И-НЕ объединены и являются вторым входом блока выбора операций, вход элемента НЕ является третьим входом блока выбора операций, выход первого элемента И-НЕ подключен кпервому входу первого элемента ИЯИ НЕ, ВЫХОД второго элемента И-НЕ подключен к первому входу второго логического элемента ИЛИ-НЕ, выход третьего элемента Й-НЕ подключен ко второму входу второго элемента ЙЛИНЕ, выход четвертого элемента И-НЕ подключен ко второму входу первого элемента ИЛИ-НЕ, выход .второго элемента ИЛИ-НЕ является первым выходом блока выбора операции, выход первого элемента является вторьш выходом блока выбора операции.

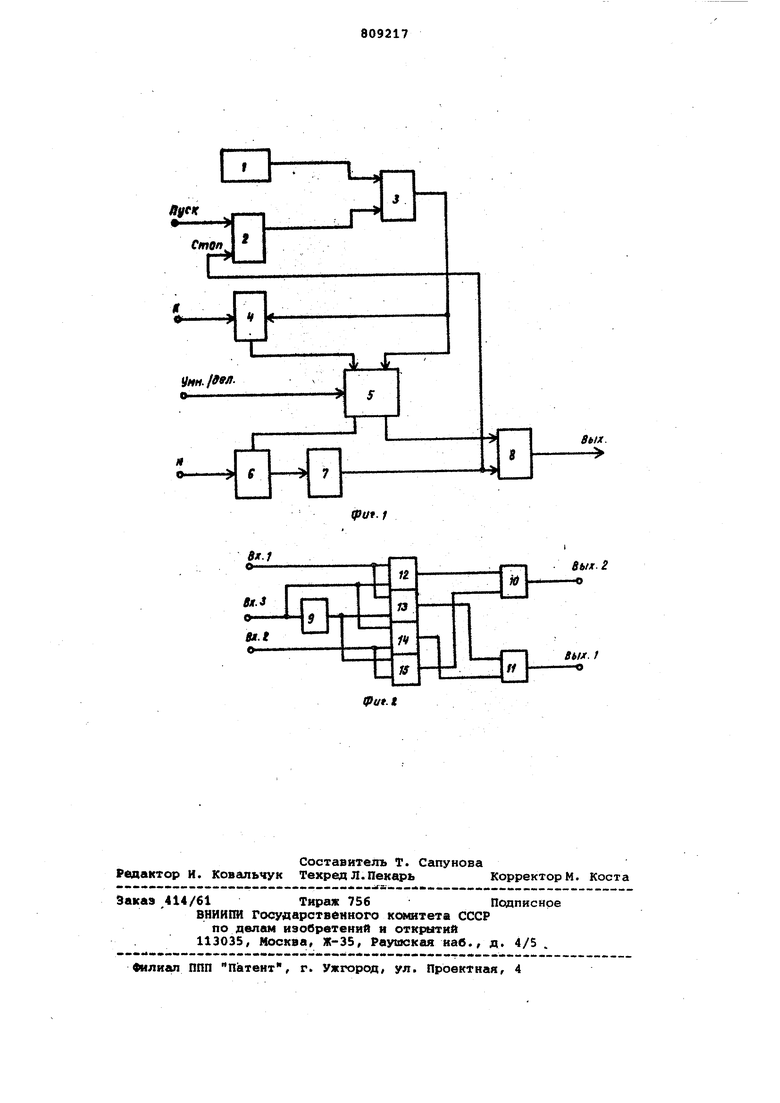

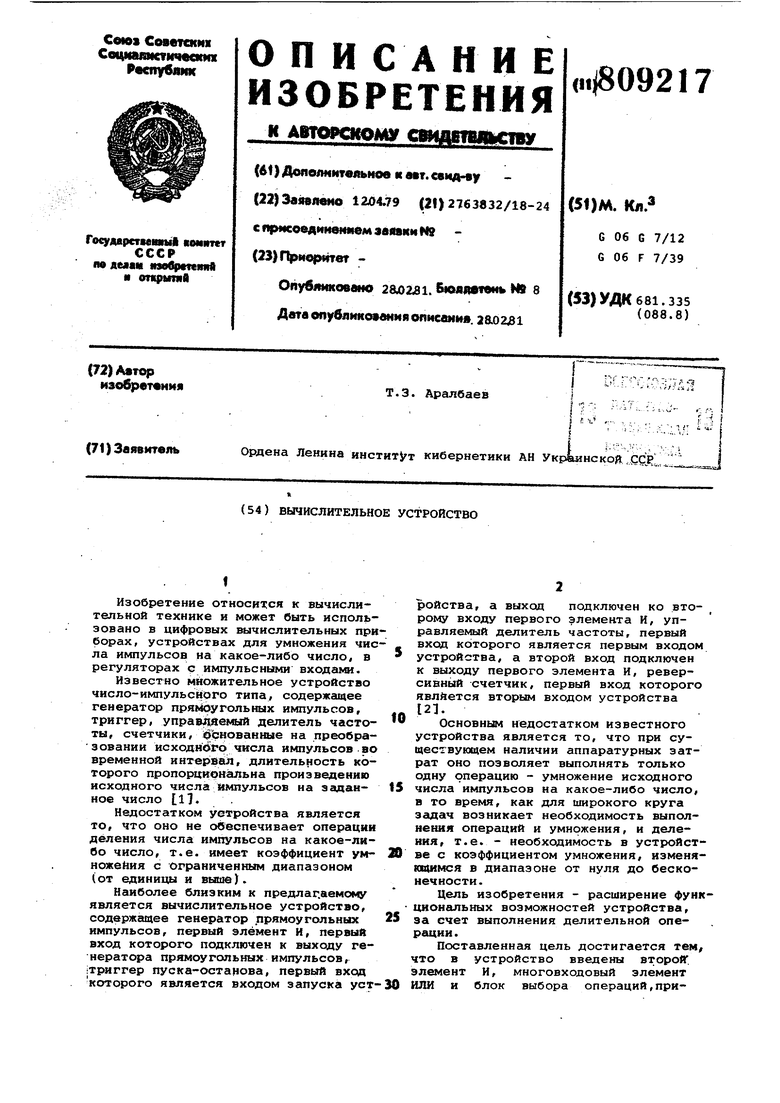

На фиг. 1 приведена блок-схема вычислительного ycтpoйcтвa на фиг. 2 - функциональная схема блока. Вычислительное устройство содержит генератор 1 прямоугольных импульсов , триггер 2 пуска-останова первый элемент И 3, управляемый делитель 4 частоты, блок 5 выбора операции, реверсивный счетчик б, многовходовой элемент ИЛИ 7, второй элемент И 8, Блок выбора операции содержит элемент НЕ 9, первый элемеит ИЛИНЕ 10, второй ИЛИ-НБ 11, первый элемент И-НЕ 12, второй элемент И-НЕ 13, элетвент 14 и четвертый элемент И-НЕ 15.

Вычислительное устройство работает следующим образом.

При выполнении операции умножения в реверсивный счетчий 6 первоначально записывается исходное число импульсов, а на управляемом делителе 4 частоты устанавливается множитель, при этом с выхода многовходового элемента ИЛИ 7 на управляемый вход вто„ рого элемента И 8, поступает сигнал, фиксируккций наличие исходного числа импульсов в реверсивном счетчике 6. При подаче команды Пуск триггер 2 раэр&вает прохождение импульсов с ге нератора 1 через первый элемент И 3 ® на вход управляемого делителя 4 частоты и первый вход блока 5 выбора операции. С выхода управляемого делителя 4 частоты импульсы с частотой, РАВНОЙ частоте генератора 1, поделен15 ной на коэффициент деления К, поступают на второй вход блока 5 выбора операции,,на третьем входе которого установлен высокий уровень потенциала, соответствукяций операции умноже2Q ния, разрешаквдий прохождение импульсов с генератора на вход второго элемента И 8 и импульсов с управляемого делителя 4 частоты на вычитакгций вход реверсивного, счетчика б. Импуль25 сы с частотой, равной частоте генератора 1 через второй элемент И 8 проходят на выход устройства. Их число определяется шириной временного интервала Т пропорционального исходноtfl числу импульсов. Ширина интервала Т определяется сигналами Пуск Стоп на входы триггера 2 и вычисляется по формуле

Т Тид N , (1) 35 исходное число импульсов,

ид период следования импульсов с выхода управляемого делителя частоты, величина которого определяется из спедунячего выражения: 0m -

Л 17 где К - коэффициент деления делителя (он же - один из сомножителей ).

f - частота импульсов генератора.

Число импульсов на выходе устроства определяется из выражения

Р - , (3) SO где Р - щ|сло импульсов на выходе

устройства,

Р - периоц следования импульсов генератора, равный

. (4)

Подставляя в выражение (3) выражени (1), (2), (4) получим

(5)

tQ При обнулении реверсивного счетчка б на второй вход второго элемент И 8 подается запрещающий сигнал, а на триггер пуска-останова - сигнал окончания операции. Число импульсов

45 на выходе второго элемента И 8, разное результату умножения, определяе ся из выражения (5). При выполнении операции деления вычислительное устройство работает аналогичным образом. На третий вход блока выбора операции подается низкий уровень потенциала, соответству щий операции деления, при этом импульсы с генератора 1 через первый выход блока выбора операции поступа ют на вычитакндий вход реверсивного счетчика б, а импульсы с выхода управляемого делителя 4 частоты через |Второй вход и второй выход блока вы бора операции поступают на вход вто рого элемента И 8. Ширина временного интервала Т на выходе триггера 2 определяется из выражения: Т т„г-м Число импульсов на выходе второго элемента И 8 определяется Т-ИА Подставляя в выражение (7) выраже|Ния (б), (2), (4), получаем результат операции деления -.к-Т «) Включение в вычислительное устрой ство блока выбора операции, второго элемента И, многовходового элемента ИЛИ позволяет расширить функциональные возможности его за счет выполнения операции деления. Формула изобретения 1. Вычислительное устройство,содержащее генератор прямоугольных импульсов , первый элемент И, первый вход которого подключен к выходу гейератора прямоугольных импульсов, триггер пуска-останова, первый вход которого является входом запуска уст ройства, а выход - подключен ко второму входу первого элемента И, управляелвлй делитель частоты, первый вход которого является первым вхо.дом устройства, а второй вход подклю чен к выходу первого элемента И,реверсивный счетчик, первый вход которого является вторым входом устройст ва, отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет выполнения делительной операции, в устройство введены второй элемент И многовходовый элемент ИЛИ и блок выбора операции, причем выход первого элемента И подключен к первому входу блока выбора операций, выход управляемого делителя частоты подключен ко второму входу блока выбора операции, третий вход которого является управлякяцим входсм устройства, первый выход блока выбора операции подключен ко второму входу реверсивного счетчика, разрядные выходы которого подключены ко входам многовходового элемента ИЛИ, выход которого подключен к первому входу второго элемента И, второй вход которого подключен ко второму выходу блока выбора операции, выход второго элемента И является выходом устройства. 2. Устройство по п. 1, отличающееся тем, что блок выбора операций содержит элемент НЕ, первый второй, третий и четвертый элементы И-НЕ и первый и второй элементы ИЛИНЕ, причем первые входы первого и второго элементов И-НЕ объединены и являются первым входом блока выбора операции, второй вход первого элемента И-НЕ и первый вход третьего элемента И-НЕ объединены и подключены ко входу элемента НЕ, второй вход второго элемента И-НЕ и первый вход четвертого элемента И-НЕ объединены и подключены к выходу элемента НЕ, вторые входы третьего и четвертого элементов И-НЕ объединены и являются вторым входом блока выбора операций, вход элемента НЕ является третьим входом блока выбора операций, выход первого элемента И-НЕ подключен к первому входу первого элемента ИЛИ-НЕ, выход второго элемента И-НЕ подключен к первому входу второго логического элемента ИЛИ-НЁ, выход третьего элемента И-НЕ подключен ко второму входу второго элемента ИЛИ-НЕ, выход четвертого элемента И-НЕ, подключен fto второму входу первого элемента ИЛИ-НЕ, выход второго элемента ИЛИ-НЕ является первым выходом блока выбора операции, выход первого элемента ИЛИ-НЕ являе ся вторым выходомблока выбора операций. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 256366, кл.С 06 F 7/44, 1968. 2.Авторское свидетельство СССР № 439808, кл. G Об F.7/39, 1972 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровое устройство для извлечения квадратного корня | 1979 |

|

SU860066A2 |

| Вычислительное устройство | 1982 |

|

SU1072044A1 |

| Умножитель частоты следования импульсов | 1981 |

|

SU966848A1 |

| Устройство для измерения механической скорости бурения | 1979 |

|

SU785467A1 |

| Устройство формирования систем двукратных производных кодовых дискретно-частотных сигналов | 2016 |

|

RU2626331C1 |

| Аналого-цифровое делительное устройство | 1979 |

|

SU886017A1 |

| Устройство для голосования | 1979 |

|

SU809271A1 |

| Преобразователь частоты в код | 1978 |

|

SU744974A1 |

| МНОГОМЕРНЫЙ СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР УСРЕДНЕННОЙ МОЩНОСТИ НЕСТАЦИОНАРНОЙ НАГРУЗКИ | 1992 |

|

RU2060542C1 |

| Устройство для контроля цифровыхОб'ЕКТОВ | 1978 |

|

SU798844A1 |

Авторы

Даты

1981-02-28—Публикация

1979-04-12—Подача