(54) АНАЛОГО-ЦИФРОВОЕ ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Множительно-делительное устройство | 1979 |

|

SU840942A1 |

| Множительно-делительное устройство | 1981 |

|

SU993278A2 |

| Аналого-цифровое делительное устройство | 1975 |

|

SU533943A1 |

| Делительное устройство | 1979 |

|

SU805342A1 |

| Устройство аналого-цифрового преобразования узкополосных сигналов | 1984 |

|

SU1225014A1 |

| Преобразователь сигналов датчиков переменного тока | 1986 |

|

SU1332531A1 |

| Система бесперебойного питания | 1990 |

|

SU1807546A1 |

| ИЗМЕРИТЕЛЬ ОТНОСИТЕЛЬНЫХ АМПЛИТУДНО-ЧАСТОТНЫХ ХАРАКТЕРИСТИК | 2007 |

|

RU2341807C1 |

| ПРЕОБРАЗОВАТЕЛЬ ИНЕРЦИАЛЬНОЙ ИНФОРМАЦИИ | 2006 |

|

RU2325620C2 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1156258A1 |

. . Изобретение относится к акалого1щфровой вычислительной технике и может быть использовано в различных комбинированных вычислительных комплексах, где требуется выполнение опера1щи деления аналоговых величин с получением результата в цифровом зиде Известны аналого-цифровые делитель ные устройства, построенные на основе аналого-цифровых преобразователей (АВД) с преобразователем код-напряжение ГПКН в цепи обратной связи ГЗ. Недостатки известных устройств состоят в низкой точности деления и сравнительно небольшом динамическом диапазоне входных сигналов. Наиболее близким по технической сущности к предлагаемому является аналого-цифровое делительное устройство, представляющее собой вычислительный аналого-цифровой преобразова тель АЦП с преобразователем код-на пряжение ПКН в цепи обратной связи в котором операция деления осуществляется подачей напряжений, соответствующих делимому, на вход схемы сравнения и напряжений, соответствующих делителю, на аналоговый вход преобразователя код-напряжение 2. Недостаток такого устройства заключается в сравнительно небольшом динамическом диапазоне входилх сигналов, соответственно, делимого и делителя. Операция деления невозможна совсем, если напряжение делимого больше напряжения делителя. Кроме того, при малых значениях напряжения делимого относительно напряжения делителя устройство обладает большой погрешностью. Цель изобретения - повышение точ ности делегая и расширение динамического диапазона входных сигналов аналого-цифрового делительного устройства. Поставленная цель достигается тем, что в аналого-цифровое делительное устройство, содержащее компаратор.

преобразователь кода в напряжение, выход которого подключен к первому входу компаратора, счетчик импульсов выходы которого подключены к управляющим входам преобразователя, кода в напряжение и являются первым выходом устройства, ключ, триггер управления и генератор импульсов, выход которого подключен к информационному входу ключа, управляющий вход ключа подключен к выходу триггера управления, выход ключа подключен ко входу счетчика, первый вход триггера управления подключен к выходу компаратора , введены масштабный блок делимого, информационный вход которого является входом делимого устройства, масштабный блок делителя, информационный вход которого является входом делителя устройства, источник опорного напряжения и блок управления, первый и второй входы которого подключены к выходам масштабных блоков делимого и делителя соответственно, третий вход блока управления подключен к выходу генератора импульсов, четвертый вход подключен к выходу источника опорного напряжения, первый и второй выходы блока управления подключены к управляющим входам масштабных блоков делимого и делителя соответственно третий выход блока управления подключен ко второму входу триггера управления, четвертый выход блока управления является вторым выходом устройства.

Кроме того, блок управления содержит четыре компаратора, два операционных усилителя, пять элементов И, четыре инвертора, два реверсивных счетчика, два дешифратора и один шифратор, первые входы первого и второго компараторов объединены и являются первым входом блока управления, второй вход первого компаратора, вход первого операционного усилителя и первые входы третьего и четвертого компараторов объединены и являются вторым входом блока управления, первые входы всех ключей объединены и являются третьим входом блока управления, второй вход третьего компаратора и вход второго операционного усилителя объединены и являются четвертым входом блока управления, выходы первого и второго операционных усилителей подключены ко вторым входам второго и четвертого компараторов соответственно, выход первого

компаратора подключен к первому входу первого элемента И, ко входу первого инвертора и к первому входу пятого элемента И, выход второго компаратора подключен ко второму входу первого элемента И и ко входу второго инвертора, выход третьего компаратора подключен к первому входу второго элемента И, ко входу третьего инвертора и ко второму входу пятого элемента И, выход четвертого компаратора подключен ко второму входу второго элемента И и ко входу четвертого инвертора, выход первого инвертора подключен к первому входу третьего элемента И, выход второго инвертора подключен ко второму входу третьего элемента И и к третьему входу пятого элемента И, выход третьего инвертора подключен к первому входу четвертого элемента И, выход четвертого инвертора подключен ко второму входу четвертого элемента И и к четвертому входу пятого элемента И, выходы первого, второго, третьего и четвертого элементов И подключены соответственно ко вторым входам первого, второго, третьего и четвертого ключей, выходы первого и второго ключей подключены соответственно к первому и второму входам первого реверсивного счетчика, выходы третьего и четвертого ключей подключены соответственно к первому и второму входам второго реверсивного счетчика, группа выходов первого реве1зсивного счетчика подключёиа ко входам первого дешифратора и к первой группе входов шифратора, группа выходов второго реверсивного

счетчика подключена ко входам второго дешифратора и ко второй группе входов шифратора, выходы первого дешифратора являются первым выходом блока управ- ления, выхо;:рз1 второго дешифратора

являются вторым выходом блока управления, выход пятого элемента И является третьим выходом блока управления, выходы шифратора являются четвертым выходом блока управления.

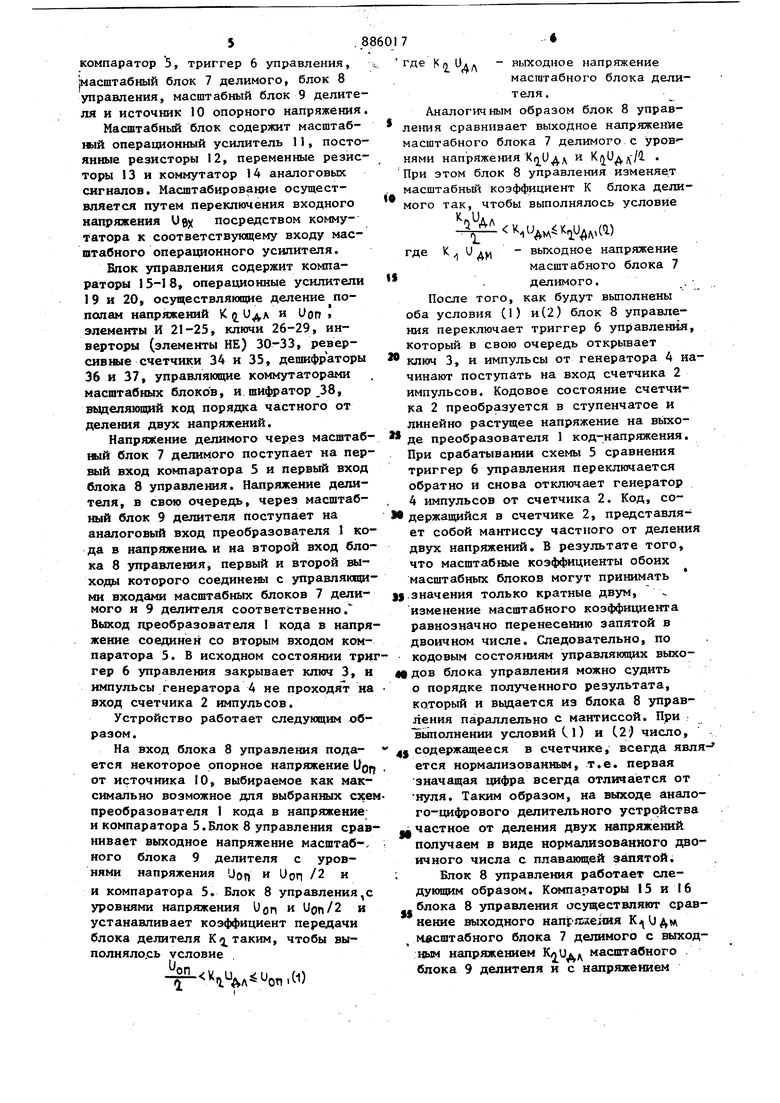

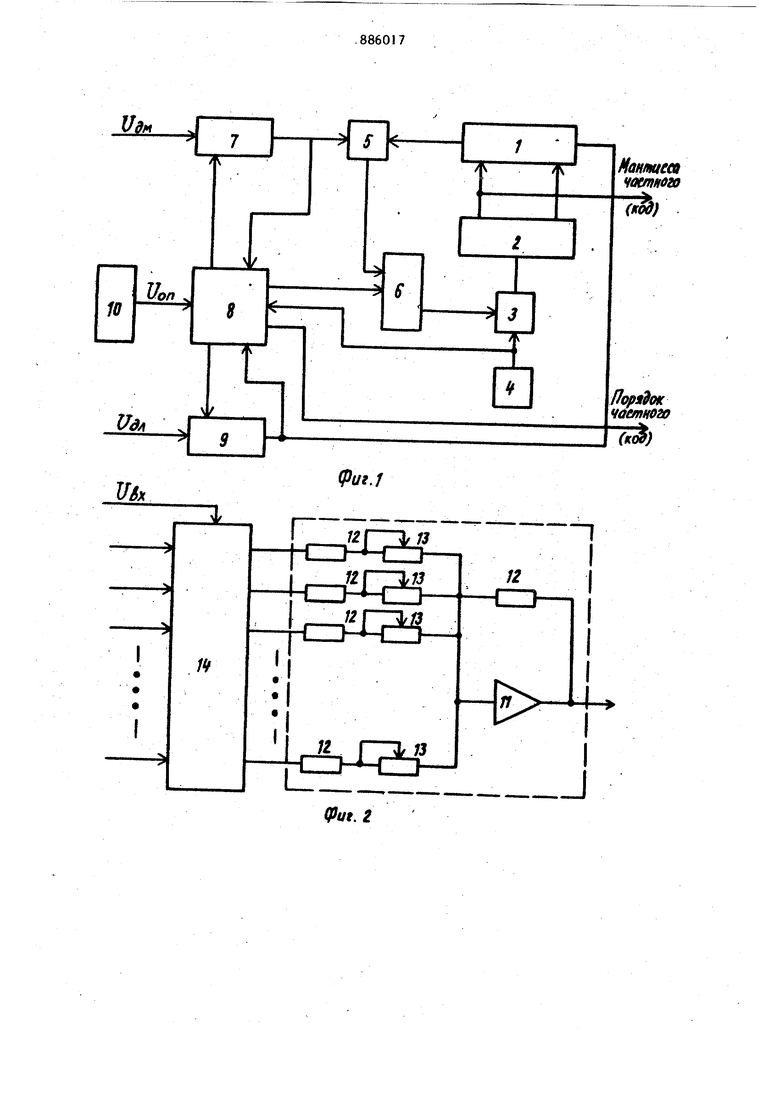

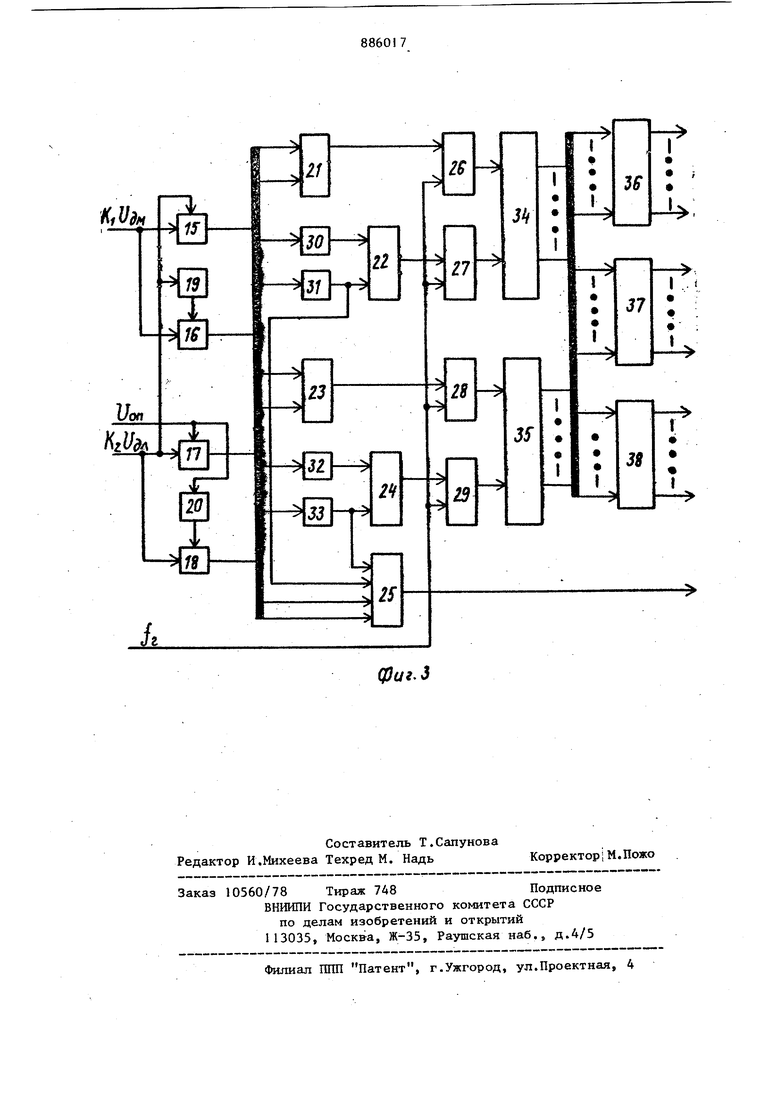

На фиг.1 приведена блок-схема аналого-цифрового делительного устройства; на фиг.2 - структурная схема масштабного блока, на фиг.З - структурная схема блока управления.

Аналого-цифровое делительное устройство содержит преобразователь 1 кода в напряжение, счетчик 2 импульсов, ключ 3, генератор 4 импульсов. компаратор 5, триггер 6 управления, масштабный блок 7 делимого, блок 8 управления, масштабный блок 9 делителя и источник 10 опорного напряжения Масштабный блок содержит масштабный операционный усилитель 11, постоянные резисторы 12, переменные резисторы 13 и коммутатор 14 аналоговых сигналов. Масштабирование осуществляется путем переключения входного напряжения Ug посредством коммутатора к соответствующему входу масштабного операционного усилителя. Блок управления содержит компараторы 15-18, операционные усилители 19 и 20, осуществляющие деление пополам напряжений К Q и Uon элементы И 21-25 ключи 26-29, инверторы (элементы НЕ) 30-33, реверсившле счетчики 34 и 35, дешифраторы 36 и 37, управляющие коммутаторами масштабных блоков, и шифратор ,38, вьщеляющий код порядка частного от деления двух напряжений. Напряжение делимого через масштаб ный блок 7 делимого поступает на пер вый вход компаратора 5 и первый вход блока 8 управления. Напряжение делителя, в свою очередь, через масштабный блок 9 делителя поступает на аналоговый вход преобразователя 1 ко да в напряжение и на второй вход бло ка 8 управления, первый и второй выхода которого соединен с управляющи ми входами масштабных блоков 7 делимого и 9 делителя соответственно. Выход преобразователя 1 кода в напря жение соединен со вторым входом компаратора 5. В исходном состоянии три гер 6 управления закрывает ключ 3, и импульсы генератора 4 не проходят на вход счетчика 2 импульсов. Устройство работает следующим образом. На вход блока 8 управления подается некоторое опорное напряжение Uof от источника 10, выбираемое как максимально возможное для выбранных схе преобразователя 1 кода в напряжение и компаратора 5.Блок 8 управления срав нивает выходное напряжение масштаб-. ного блока 9 делителя с уровнями напряжения JQ и Uon /2 и и компаратора 5. Блок 8 управления,с уровнями напряжения Uon и Uon/2 и устанавливает коэффициент передачи блока делителя К таким, чтобы выполняло.сь условие on .C1) где Ко D - выходное напряжение масгатабного блока делителя. Аналогичным образом блок 8 управления сравнивает выходное напряжение масштабного блока 7 делимого с уров нями напряжения , и . При этом блок 8 управления изменяет масштабный коэффициент К блока делимого так, чтобы выполнялось условие Kaj. ) где К. U - выходное напряжение масштабного блока 7 делимого. После того, как будут вьтолнены оба условия (1) и(2) блок 8 управле ния переключает триггер 6 управления, который в свою очередь открывает ключ 3, и импульсы от генератора 4 начинают поступать на вход счетчика 2 импульсов. Кодовое состояние счетчика 2 преобразуется в ступенчатое и линейно растущее напряжение на выходе преобразователя 1 код-напряжения. При срабатывании схемы 5 сравнения триггер 6 управления переключается обратно и снова отключает генератор 4 импульсов от счетчика 2. Код, содержащийся в счетчике 2, представляет собой мантиссу частного от деления двух напряжений. В результате того, что масштабные коэффициенты обоих масштабных блоков могут принимать .значения только кратные двум, изменение масштабного коэффициента равнозначно перенесению запятой в двоичном числе. Следовательно, по кодовым состояниям управляющих выходов блока управления можно судить о порядке полученного результата, который и вьщается из блока 8 управления параллельно с мантиссой. При выполнении условий Cl) и (2) число, содержащееся в счетчике, всегда явля- ется нормализованным, т.е. первая значащая 1Ц1фра всегда отличается от нуля. Таким образом, на выходе аналого-цифрового делительного устройства частное от деления двух напряжений получаем в виде нормализованного двоичного числа с плавающей 3 шятой. Блок 8 управления работает следующим образом. Компараторы 15 и 16 блока 8 управления осуществляют сравнение выходного напрп;хе;щя масштабного блока 7 делимого с выходным напряжением Клидд масштабного блока 9 делителя и с напряжением

, соответственно. Компараторы 17 и 18 блока 8 управления осуществляют сравнение вьпсодного напряжения масштабного блока 9 делителя с опорным напряжением fg и с напряжением UQI I/I соответственно. Совокупность элементов И 21, 22, ключей 26 и 27 и инверторов 30 и 31 обеспечивает управление реверсивным счетчиком 34, который через дешифратор 36 переключает коммутатор 14 масштабного блока 7 делимого. Логика работы блока управления предполагает для компараторов, что если уровень сравниваемого напряжения больше заданного, то на выходе компаратора появляется логический ноль, в противном случае логическая единица. По кодовому сочетанию выходных сигналов компараторов 15 и 16 вырабатываются сигналы управления реверсивным счетчиком 34 на счет в прямом либо обратном направлении и останов.

Так, при состоянии выходных сигналов компараторов 15 и 16 соответственно JI срабатывает элемент И 21 и через ключ 26 включает реверсивный счетчик 34 на счет в прямом направлении. На первые входы ключей 26, 27, 28 и 29 поступают импульсы fi от генератора 4 импульсов аналого-цифрового делительного устройства. При состоянии выходных: сигналов указанных компараторов 00, эти сигиалы инвертируются с помощью инверторов 30 и 31, срабатьшает элемент И 22 и через ключ 27 включает реверсивный счетчик 34 на счет в обратном направлении. При состоянии выходных сигналов компараторов 15 и,16 соответственно 10 ключи 26 и 27 закрыты и реверсивный счётчик 34 находится в состоянии покоя. Указанное состояние выходных сигналов компараторов имеет; место при вьтолнении условия (2).

Аналогичным образом работает и второй канал для управления масштабдам блоком делителя с компараторами 17 и 18, реверсивным счетчиком 35, управляювдм дешифратором 37, элеменами И 23, 24, ключами 2В к 29 и инерторами 32 и 33. Состояние выходых сигналов компараторов 17 и 18, оответственно, 10 имеет место при ыполнении условия (.1). Элемент И 5 вцделяет состояние компараторов 15, 16, 17 и 18 соответственно, 1010, оторое имеет место только при одноременном выполнении условий (. I ) и

(2, и запускает триггер 6 управления аналого-цифрового делительного устройства.

Для выделения кода порядка частного от деления двух напряжений служит шифратор 38, на .входы которого поступают выходы обоих реверсивных счетчиков 34.и 35. Принципиально шифратор 38 может быть вьтолнен как комбинационный двоичный сумматор в режиме вычитания.

Применение предлагаемого устройства по сравнению известными позволяет получить более высокую точность выполнения операции деления напряжений, так как в процессе работы устройства сравнение напгяже1тй на компараторе осуществляется на более высоком уровне по сравнению с

известным устройством, значительно расширить динамический диапазон входных сигналов, результат деления напряжений получать в виде нормализованного двоичного числа с плавающей запятой, что позволяет использовать его без дополнительных преобразований в цифровых вычислительных устройствах и системах.

IP

Формула изобретения

выход которого подключен к первому входу компаратора, счетчик импульсов, выходы которого подключены к управляющим входам преобразователя , кода в напряжение и являются первым

выходом устройства, ключ, триггер управления и генератор импульсов, выход которого подключен к информационному входу ключа, управляющий вход ключа подключен к выходу триггера управления, выход ключа подключен ко входу счетчика, первый вход триггера управления подключен к выходу компаратора, отличающее с Я тем, что, с целью повьш1ения

точности деления и расширения динамического диапазона входных сигналов, в него введены масштабный дели.мого, информационный вход которого , является входом делимого устройства, масштабный блок делителя,информационный вход которого является входом делителя устройства, источник опорного напряжения и блок управления, первый и второй входы

которого подключены к выходам масштабных блоков делимого и делителя соответственно, третий вход блока управления подключен к выходу генератора импульсов, четвертый вход подключен к выходу источника опорного напряжения, первый и второй выходы блока управления подключены к управляющим входам масштабных блоков делимого и делителя соответственно, третий выход блока управления подключен ко второму входу триггера управления, четвертый выход блока управления является вторым выходом устройства.

и ко второму входу пятого элемента И, выход четвертого компаратора подключен ко второму выходу второго эле-, мента И и ко входу четвертого инвертора, выход первого инвертора подключен к первому входу третьего элемента И, выход второго инвертора подключен ко второму входу третьего элемента И и к третьему входу пятого

элемента И,выход третьего инвертора подключен к первому входу четвертого элемента И,выход четвертого инвертора подключен ко второму входу четвертого элемента И и к четвертому входу пятого элемента И, выходы первого, второго, третьего и четвертого элементов-И подключены соответственно ко, вторым . входам первого, второго, третьего и

четвертого ключей, выходы первого и

второго ключей подключены соответственно к первому и второму входам первого реверсивного счетчика, выходы третьего и четвертого ключей подключены соответственно к первому и

) второму входам второго реверсивного счетчика, группа выходов первого реверсивного счетчика подключена ко входам первого дешифратора и к первой группе входов шифратора, группа выхо дов второго реверсивного счетчика подключена ко входам второго дешифратора и ко второй группе входов шифратора, выходы первого дешифратора являются первым выходом блока управления, выходы второго дешифратора явля. ются вторым выходом блока управления, выход пятого элемента И является третьим выходом блока управления, выходы шифратора являются четвертым

выходом блока управления.

Источники информации, принятые во внимание при экспертизе

№ 438999, кл. G Об J 3/00, 1972 (прототип) .

Uc

on

10

L

UdA

MoHimteai

/ частного

HoptioK частного

г/л

фиг.З

Авторы

Даты

1981-11-30—Публикация

1979-06-04—Подача