(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЦИФРОВЫХ ОБЪЕКТОВ

12

сравнения, дискриминатор, формирователь чисел, формирователь сигналов формирователь адреса и коммутатор, причем первый выход блока хранения программы соединен с первым входом формирователя чисел, выход которого подключен к первому входу дискриминатора и к первому входу коммутатора, выход которого подключен ко второму входу дискриминатора, второй выход блока хранения программы соединен с первым входом счетчика циклов, первый выход которого подключен к первому входу формирователя адреса, второй, вход которого соединен со вторЕлм входом блока сравнения и с первым выходом счетчика адреса, второй выход которого подключен к первому входу блока управления, первый выход которого соединен с первым входом счетчика адреса, второй вход которого подключен к третьему выходу блока хранения программы, четвертый выход которого соединен с первым входом формирователя сигналов, второй вход которого подключен к управляющему выходу блока управления, второй выход которого подключен к третьему входу дискриминатора, выход которого подключен ко второму входу блока управления, третий вход которого соединен со вторым выходом счетчика циклов , второй вход которого подключен к третьему выходу блока управления, четвертый выход которого подключен к первому входу блока хранения программы, пятый выход которого соединен с четвертым входами блока управления, шестой выход которого подключен к четвертому входу дискриминатора, выход формирователя сигналов подключен ко второму входу кол мутатора, третий вход которого подключен к выходу формирователя адреса, введены делитель частоты, счетчик и элемент ИЛИ, причем первый вход делителя частоты соединен с седьмьом выходом блока- хранения программы второй вход делителя частоты объединен с первым входом счетчика и с пятым выходом бл ка управления, пятый вход которого подключен к первому выходу, делителя частоты, второй выход которого подключен ко второму входу формирователя частоты и к первому входу элемента ИЛИ, третий вход формирователя частоты.объединен с выходом блока с-равнения, со вторым входом счетчика с третьим входом делителя частоты и подключен к шестому входу блока управления, седьмой вход которого подключен к третьему входу счетчика, вы.ход которого Соединен со вторым входом элемента ИЛИ и с четвертым входом формирователя чисел, выход элемента ИЛИ соединен с третьим входом формирователя адреса.

.Таким образом, за счет введения .указанных узлов и связей расширяются

возможности программирования и тем самым повышается качество контроля.

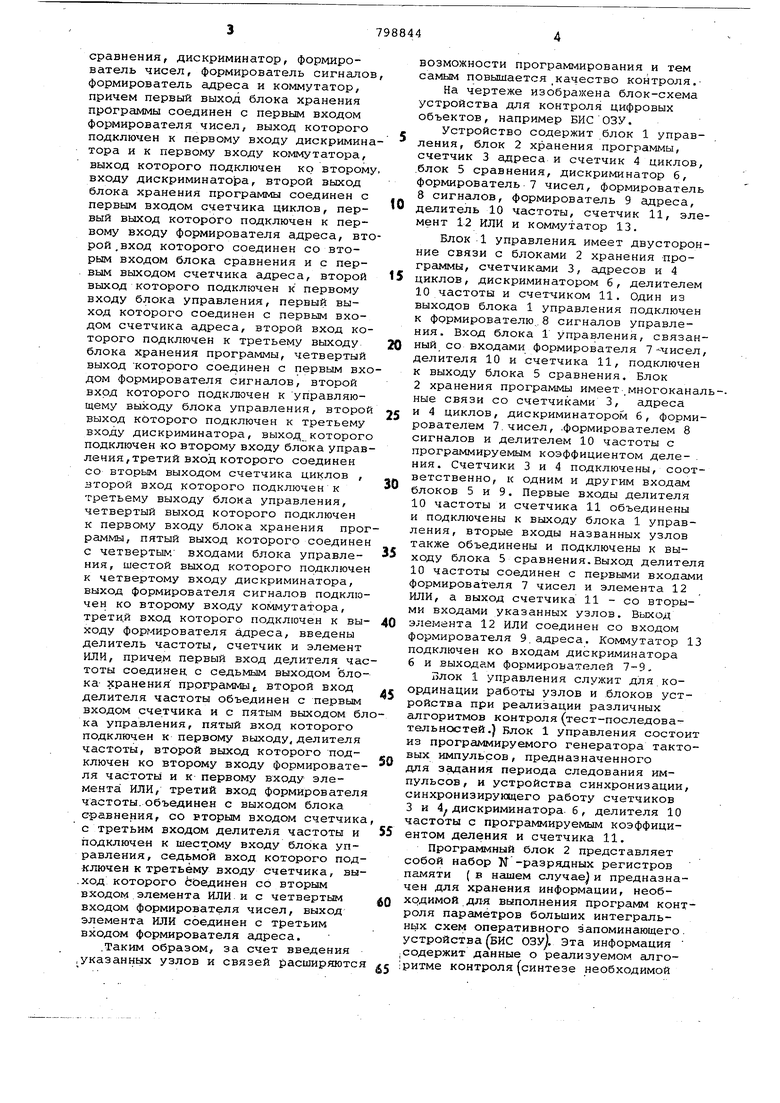

На чертеже изображена блок-схема устройства для контроля цифровых объектов, например БИС ОЗУ.

Устройство содержит блок 1 управления, блок 2 хранения программы, счетчик 3 адреса и счетчик 4 циклов, .блок 5 сравнения, дискриминатор 6, формирователь 7 чисел, формирователь 8 сигналов, формирователь 9 адреса, делитель 10 частоты, счетчик 11, элемент 12 ИЛИ и коммутатор 13.

Блок 1 управления, имеет двусторонние связи с блоками 2 хранения -программы, счетчиками 3, адресов и 4 циклов, дискриминатором 6, делителем 10 частоты и счетчиком 11. Один из выходов блока 1 управления подключен к формирователю.. 8 сигналов управления. Вход блока 1 Управления, связанный со входами формирователя 7--чисел делителя 10 и счетчика 11, подключен к выходу блока 5 сравнения. Блок

2хранения программы имеет.многокананые связи со счетчиками 3, адреса

и 4 циклов, дискриминатором б, формирователем 7.чисел, .формирователем 8 сигналов и делителем 10 частоты с программируемым коэффициентом деле- . ния. Счетчики 3 и 4 подключены, соответственно, к одним и другим входам блоков 5 и 9. Первые входы делителя 10 частоты и счетчика 11 объединены и подключены к выходу блока 1 управления, вторые входы названных узлов также объединены и подключены к выходу блока 5 сравнения.Выход делител 10 частоты соединен с первыми входам формирователя 7 чисел и элемента 12 ИЛИ, а выход счетчика 11 - со вторыми входами указанных узлов. Выход элемента 12 ИЛИ соединен со входом формирователя 9.адреса. Коммутатор 1 подключен ко входам дискриминатора 6 и выходам формирователей 7-9,

Блок 1 управления служит для координации работы узлов и блоков устройства при реализации различных алгоритмов контроля (тест-последовательностей.) Блок 1 управления состои из программируемого генератора тактовых импульсов, предназначенного для задания периода следования импульсов, и устройства синхронизации, синхронизирующего работу счетчиков

3и 4 дискриминатора. 6, делителя 10 частоты с программируемым коэффициентом деления и счетчика 11.

Программный блок 2 представляет собой набор Н -разрядных регистров памяти ( в нашем случае и предназначен для хранения информации, необходимой дл-я выполнения программ контроля параметров больших интегральных схем оперативного запоминающего, устройства (БИС ОЗУ). Эта информация Iсодержит данные о реализуемом алго;ритме контроля (синтезе необходимой

тест-последовательности) о размере контролируемой БИС ОЗУ (т. е. о количестве разрядов aдpeca) об области контроля, границами которого является начальный и конечный адрес .о длительности периода следования импульсов синхронизации; о величинах граничных значений считываемого сигнала О и 1 для дискриминатора 6 j о длител -ости управлягацихимпульсов .для блока 8 и их задержке относительно импульсов синхронизации;, о порядке прохождения информаци (прямой или инверсной на входы контролируемого БИС ОЗУ. Информация в программный блок 2 может быть занесена из электронной вычислительной машины (ЭВМ или с пульта управления/на чертеже не показаны}.

Счетчики 3 и 4 представляют собой N -разрядные двоичные счетчики(в нашем случае 16-разрядные счетчики}. Счетчик 3 адреса ,предназначен для выбора контролируемой ячейки памяти и формирования кода ее адреса, а счетчик 4 циклов-для подсчета количества циклов при реализации циклических сшгоритмов контроля, например бегущая 1 или О, а также для выбора формирования кода адреса П. -ячейки при реализации алгоритма контроля реверсивный скачок с переменным шагом.

Блок 5 сравнения циклов представляет собой набор цифровых компараторов (по числу разрядов счетчиков 3 и 4), предназначенных для поразрядного сравнения двоичных кодов, поступающих с выходов разрядов счетчиков 3 и 4 и формирования при равенстве этих кодов сигнала, разрешающего смену адреса п - ячейки.

Дискриминатор 6 представляет собой ва аналоговых компаратора с 4- входовыми логическими элементами И на выходе. Один из компараторов предназначен для сравнения амплитуды выходного уровняс заданным опорным уровнем О, а второй - с уровнем 1. Логические элементы И предназначены для фиксации момента сравнения.

Формирователь 7 чисел выполнен на Д-триггерах и логических элементах И и ИЛИ. Назначение формирователя 7-формирование числового кода для контролируемого БИС ОЗУ. .

Формиррватель 8 управЛякядих сигналов выполнен на регистре, двух цифровых компараторах и двух двоично-десятичных счетчиках. Он предназначен для формирования импульсов с заданной задержкой относительно импульса пуска и с заданной длительностью.

Формирователь 9 адреса представляет собой дешифратор, инверторы и двухканальный коммутатор. Блок 9 предназначен для выработки адреса сЪ

ответствующей ячейки контроля йогласно заданному алгоритму.

Делитель 10 частоты с программируемым коэффициентом деления пред- ставляет собой N -разрядный счетчик и предназначен для задания числа обращений от р -ячейки памяти к m -ячейке контролируемого БИС ОЗУ, причем число обращений равно 1 -1.

Счетчик. 11 представляет собой двоичный счетчик, предназначенный для формирования разрешения контроля п+ ячейки памяти.

Элемент 12 ИЛИ предназначен для пропускания сигналов управления в формирователь 9 адреса.

Коммутатор 13 для включения контролируемого объекта представляет собой релейную матрицу, обеспечивающую подключение выводов контролируемого БИС ОЗУ к соответствующим узлам.

Устройство работает следующим образом.

В коммутатор 13 помещают контролируемое БИС ОЗУ.

По сигналу Пуск от блока 2 хранения программ на реализацию требуемого алгоритма на выходах блока 1 управления устанавливаются следующие сигналы: сигнал разрешения на работу счетчика 3 адреса, разрешения формирования сигналов записи информации посредством формирователя 9 сигналов управления, запрещения прохождения тактовых импульсов на счетчик 4 -циклов, делитель 10 частоты и счетчик 11, и сигнал разрешения записи информации из блока 2 хранения программы в узлы и блоки устройства. По получении этого сигнала из блока 2 хранения программы заносится программа контроля в счетчики 3 и 4, в дискриминатор б, в формирователи 7-9 и в делитель 10 частоты с программируемым коэффициентом деления. После занесения программ контроля из блока 2 хранения програм в перечисленные узлы и блоки происхдит формирование адресов ячеек Пс1мяти контролируемой БИС ОЗУ согласно реализуемому алгоритму контроля.

При реализации алгоритма контроля шахматный порядок счетчик 3 адреса через формирователь 9 адреса производит выбор ячеек памяти контролируемого БИС ОЗУ. При этом формирователь 7 вы.рабатывает числовой код, который посредством формирователя 8 управляющих сигналов заносится в выбранную ячейку контроля, устройство переходит из режима записи в режим считывания информации со всего поля адресов контролируемого БИС ОЗУ.

При реализации алгоритма контроля бегущая 1 или О счетчик 3 адреса работает аналогичным образом, а счетчик 4 циклов осуществляет подсчет

количества циклов и формирует сигнал в двоичном коде, который поступает в блок 5 сравнения и сравниваетс я в нем с двоичными кодами счетчика 3 адреса.

При равенстве указанных кодов бло 5 сравнения вырабатывает сигнал для формирователя 7 чисел на изменение числовой информации .{прямой или инверсной), поступающей на контролируемое БИС ОЗУ. Этот же сигнал через блок 1 управления увеличивает содержимое счетчика 4 циклов на единицу При этом содержимое счетчика 3 адрес .не изменяется. Устройство переводится в режим записи информации,формирователь 7 чисел вырабатывает прямую информацию, записываемую вадрес начальной ячейки памяти, блок 1 управления разрешает работу счетчика 3 адреса, содержимое которого увеличив ется на единицу, блок 5 сравнения снова фиксирует равенство кодов счетчиков 3 и 4 по адресу второй ячейки памяти.

Аналогичным образом осуществляется запись инверсной информации во вторую ячейку, после чего устройство снова переводится в режим считывания Дальнейшая, работа устройства при реализации алгоритма контроля бегущая 1 или О осуществляется описанным образом до тех пор, пока на выходах счетчика 4 циклов не, установится код адреса конечной ячейки, что фиксируется блоком 5 сравнения, который формирует сигнал для блока 1 управления, по получении которого последний по окончании режима считывания формирует сигнал Окончание контроля.

Перед реализацией алгоритма контроля реверсивный скачок с переменным шагом посредством сигнала с блока 1 управления на установку ячеек памяти контролируемого БИС ОЗУ в одинаковое начальное состояние, ко входам ьоследне.го прикладывается определенная тест-последовательность, которая обеспечивает данную операцию, по око чании которой блок 1 управления разрешает независимую работу счетчиков 3 и 4. При этом счетчик 3 адреса обеспечивает выбор адресов п; ячеек памяти, а счетчик 4 циклов - ря ячеек памяти контролируемого БИС ОЗУ

Пусть, посредством счетчика 3 адресов выбран адрес nj -ячейки контроля, в которую посредством формирователей 7 и 8 в соответствии с программой контроля записывается информация. Делитель 10 частоты, коэффициент деления, которого, заданный программным блоком 2, определяет; число обращений Г(скачко между ,и №,j-ячейками контроля, формирует сигнал для формирователя 7 чисел, который, в свою очередь, обеспечивает смену информации в контролируемом объекте (при обращении от I7.j- ячейкам контроля )и в дискримина торе б. По окончании цикла обращения, равного 1, делитель 10 частоты вырабатывает сигнал для блока 1 управления, который увеличивает содежимое счетчика 4- циклов на единицу и тем самым обуславливает переход к -ячейке контроля.

По окончании цикла обращений между h, - и mi+t ячейками аналогичHbDvi образом осуществляется переход к m.j42. -ячейке, т. д.

Таким образом осуществляется проверка информационных свойств всего поля адресов контролируемого БИС ОЗУ относительно -ячейки контроля.

Описанный процесс происходит до тех пор, пока блоком 5 сравнения не зафиксируется равенство цифровых кодов счетчиков 3 и 4, что соответствует nj m, При этом блок 5 сравнения формирует сигнал для двоичного счетчика 11, который через блок 1 управления увеличивает содержимое счетчика 4 циклов на единицу и тем самым обуславливает переход к . ячейке контроля. Далее аналогичным образом осуществляется проверка информационных свойств всего поля адресов контролируемого БИС ОЗУ относительно П - ячейки контроля.

При реализации алгоритма контроля реверсивный скачок с переменным шаго выбор rtj ит -ячеек контроля произволен по всему полю адресов. Алгоритм контроля диагональный порядок является его частным случаем.

Предлагаемое устройство для контроля обеспечивает высокое качество контроля, полноту и достоверность; дает возможность осуществлять диагностику неисправностей при массовом производстве, например-БИС ОЗУ, и пр необходимости (в случае проявления стойкого отказа) изменять технологию изготовленияс целью устранения причины отказа.

Формула изобретения

Устройство для контроля цифров объектов, содержащее блок управления, блок хранения программы, счетчик адреса, счетчик циклов, блок сравнения, дискриминатор, формирователь чисел,формирователь сигналов формирователь адреса и коммутатор, причем первый выход блока хранения программы, соединен с первым входом формирователя чисел, выход которого подключен к первому входу дискриминатора и к первому входу коммутатора, выход которого подключен ко второму BJtpдy дискриминатора, второй выход блока хранения программы соединен с первым входом, счетчика циклов, первы выход которого подключен к первому входу блока сравнения и к первому /входу формирователя адреса, второй вход KOTuporo соединен со вторым вхо дом блока сравнения и с первым выходом счетчика адреса, второй выход которого подключен к первому входу блока управления, первый выход которого соединен с первым входом счетчика адреса, второй вход которого по ключей к третьему выходу блока хранения программы, четвертый выход которого соединен с первым вгьодом формирователя сигналов, второй вход которого подключен к .управляилдему в&хо ду блока управления,второй выход ко.торого подключен к третьему входу дискриминатора, .выход которого подключен ко второму входу блока управления, третий вход которого соединен е,о вторым выходом счетчикациклов, второй вход которого подключен к третьему выходу блока управления,чет вертый выход которого подключён к первому входу блока хранения программы, пятый выход которого соединен с четвертым входом блока управления, шестой выход которого подключен к четвертому входу дискриминатора, выход формирователя сигналов подключен ко. второму входу коммутатора, третий .вход которого подключен к выходу фор мирователя адреса, о т ли ч а ю щ е я тем, что, с целью повышения достоверности контроля, в устройство введены делитель частоты, счетчик и элемент ИЛИ, причем первый вход делителя частоты соединен с седьмым выходом блока хранения программы, второй вход делителя частоты объединен с первым входом счетчика и с пятым выходом блока управления, пятый вход которого подключен к первому ВЫХОДУ;делителя частоты, второй выход которого подключен ко второму входу формирователя частоты и к первому входу элемента ИЛИ, третий вход формирователя частоты объединен с выходом блока сравнения, со вторым входом счетчика, с третьим входом делителя частоты и подключен к шестому входу блока управления, седьмой вход которого подключен к третьему входу счетчика, выход которого соединей со вторьв входом элемента ИЛИ и с четверть входом формирователя чисел, выход элемента ИЛИ соединен с третьим входом формирователя адреса. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 546838, кл. G 06 Р 11/00, 1974. 2.Авторское свидетельство СССР,. 526954, кл. G 11 С 29/00, 1975. (прототип)„

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля оперативной памяти | 1981 |

|

SU957279A1 |

| Устройство функционального контроля интегральных схем с функцией памяти | 1978 |

|

SU748303A1 |

| Устройство для контроля цифровых объектов | 1983 |

|

SU1160373A1 |

| Устройство для автоматического контроля больших интегральных схем | 1984 |

|

SU1205083A1 |

| Устройство для задания тестов | 1985 |

|

SU1290265A1 |

| Устройство для контроля блоков памяти | 1978 |

|

SU717668A1 |

| Устройство для автоматического поиска дефектов в логических блоках | 1988 |

|

SU1681304A1 |

| Многоканальный программируемый генератор импульсов | 1979 |

|

SU860295A1 |

| Устройство для контроля полупроводниковой оперативной памяти | 1981 |

|

SU991516A1 |

| Система автоматического контроля параметров электронных схем | 1989 |

|

SU1700538A1 |

Авторы

Даты

1981-01-23—Публикация

1978-10-09—Подача