, Изобретение относится к импульсной

технике.

Известен умножитель частоты импульсов, солер 1 ащий формирователь импульсов, триггер, элементы И и ИЛИ, генератор опорных частот, делители частоты, переключатель, элементы задержки, мультиплексоры, элемент совпадения, формирователь коротких импульсов, счетчики, элемент сравнения, запоминающие блоки, секционированную линию задержки, блок переноса f1.

Данный умножитель не обеспечивает достаточного коэффициента умножения.

Наиболее близким по технической сущности к предложенному является умножитель, содержащий блок управления, подключенный через формирователь к входной шине, выходы которого соединены соответственно с входами блоков коррекции и умножения, входом блока коррекции ошибки и входом блока динамической коррекции, генератор опорных частот, выход которого сое динен с входами ключа, блока коррекции и входом блока динамической коррекции , выход которого соединен с входом ключа, второй вход которого соединен с выходом блока коррекции, а выход ключа - с входом блока умножения, выход которого соединен с одним из входов блока,коррекции ошибки, делитель частоты, соединенный с выходом генератора опорных ча10стот и с соотвеггствующими входами блока коррекции и блока умножения, а также элемент задержки, элементы И, ИЛИ и триггеры Г2}.

Однако данный умножитель отлича15ется недостаточным динамическим диапазоном изменений частоты и ощутимой динамической погрешностью.

Цель изобретения - расширение динамического диапазона изменений ча20стоты выходного сигнала и уменьшение динамической погрешности.

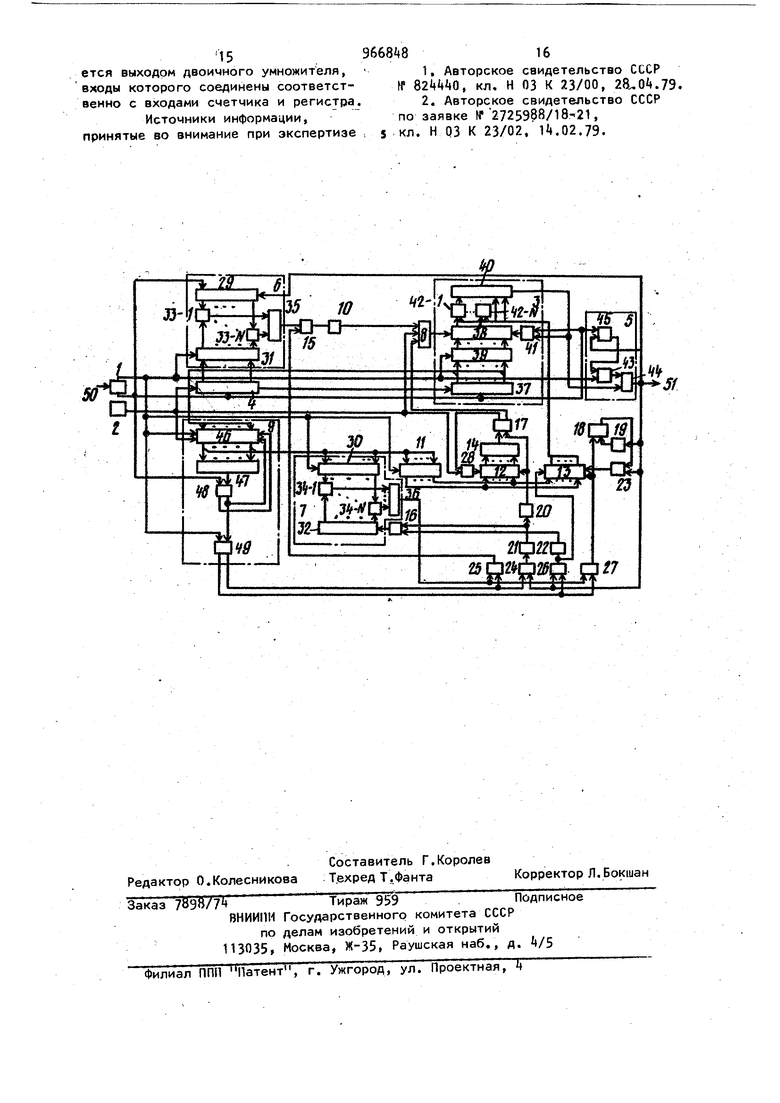

Поставленная цель достигается . тем, что в умножитель частоты следо396вания импульсов, содержащий бпек управления, вход которого соединен с входной шиной, первый выход соединен с первыми входами блока умножения и блока коррекции ошибки, а второй выход соединен с первым входом делителя частоты, вторым и третьим входами блока умножения и вторым вхо дом блока коррекции ошибки, третий вход которого соединен с выходом бло ка умножения, четвертый вход которого соединен с выходом делителя чаЬтоты, а пятый вход подключен к выходу ключа, первый вход которого .соединен с выходом генератрра qnopной частоты и вторым входом делителя частоты, счетчик, выходы которого поразрядно Соединены с входами миогойходового элемента И, реверсивный счетчик. Элемент ИЛИ, элемент за держки, триггер и три элемента двухвходовых И, введены регистр, три элемента задержки три элемента И, элемент ИЛИ, одновибратор, триггер, блок определения знака и кода приращений периода и два двоичных умножителя , первые входы которых соединены с первым выходом блока управления, первым и вторым входами блока опреде ления знака и кода приращений период и первым входом регистра, остальные входы которого соединены с разрядными выходами блока определения знака и кода приращений периода, а выходы регистра соединены поразрядно с входами счетчика и входами реверсивного счетчика, выходы которого поразрядно соединены с остальными входами блока умножения, выходы разрядов которого соединены с соответствующими входами разрядов блока определени знака и кода приращений периода, тре тий вход которого соединен с выходом генератора опорной частоты, четвертый вход подключен к второму выходу блока управления и второму входу пер вого двоичного умножителя, третий вход которого соединен с первыми вхо дами первого и второго двухвходовых элементов И, с входом первого элемен та задержки и выходом блока коррекции ошибки, рстальньГё входы первого двоичного умножителя подключены поразрядно к выходам делителя частот)-, а выход первого двоичного умножителя через последовательно соединенные первый элемент ИЛИ, второй вход кото рого соединен с выходом третьего элемента И, и одновибратор соединён С вторым входом ключа, третий вход которого соединен с первым выходом первого триггера, первый вход которого соединен ч; выходом многовходовпго элемента И, а второй вход соединен с первым входом счетчика и через последовательно соединенные второй и третий элементы задержки подключен к выходу второго элемента И, первый вход которого соединен с первым входом четвертого элемента И« выход которого соединен с первым входом реверсивного счетчика непосредственно и с первым входом второго элемента ИЛИ через четвертый элемент задержки, второй вход второго элемента ИЛИ соединен с выходом третьего элемента зйдержки, а выход второго элемента ИЛИ соединен с вторым входом второго двоичного умножителя, выход которого подключен к первым входам третьего и пятого элементов И, вторые входы которых соединены с вторыми входами сс тветственно второго и четвертого элементов И и с соответствующими выходами блока определения знака и кода приращений периода, причем .выход пятого элемента И соединен с вторым входом реверсивного счетчика и/ первым входом второго триггера, второй вход которого подключен к выходу первого элемента задержки, а вы- . ход соединен с вторым входом первого элемента И, выход -которого соединен с третьим входом реверсивного счетчика, при этом второй вход счетчика соединен с выяодом шестого элемента И, входы которого соединены с выходом генератора опорной частоты и вторым выходом первого триггера. Блок определения знака и кода приращений периода содержит поразрядно соединенные реверсивный счетчик и многовходовый элемент И, и два триггера, входы первого из которых соединены с выходом многовходового элемента И и четвертым входом блока определения знака и кода прира1цения пе риода, а первый выход соединен с первым входом второго триггера и первым входом реверсивного счетчика, второй вход которого подключен к второму выходу первого триггера, а третий и четвертый входц реверсивного счетчика соединены соответственно с первым и третьим входами блока определения знака и кода приращений периода, второй вход которого соединен с вторым входом второго триггера, выходы которого подключены к выходам блока определения знака и кода приращений периода. Каждый двоичный умножитель содержит счетиик и регистр, выходы ко торых поразрядно соединены с входам элементов И, выходы которых соединены с входами элемента ИЛИ, выход которого является выходом двоичного умножителя, входы которого соеди нены соответственно с входами счетчика и регистра. На чертеже приведена структурная электрическая схема умножителя. Умножитель- сЬдержит блок 1 управления, генератор 2 опорной чаcaiTMj блок 3 умножения, делитель k частоты, блок 5 коррекции ошибки, двоичные умножители 6, 7, ключ 8, блок 9 определения знака и кода при ращения периода,одновибратор 10, ре гистр 11, счетчик 12 реверсивный счетчик 13, многовходовый элемент И И элементы 15, 16 ИЛИ, триггеры 17, 1В, элементы 19...22 задержки, элементы 23...28 И. Первый и второй двоичные умножители содержат соответственно счетчи ки 29 и 30, регистры 31 и 32; эпе мемты 33-1...33-N и ...34-N И, элементы 35 и Зб ИЛИ. Блок умножения содержит счетчики 37, 38, запоминающий регистр 39,многовходовый элемент 0 И, элемент 1 ИЛИ, элементы 42-1 .. . И. Блок ошибки содержит элемент k3 И, элемент ИЛИ, триггер kS. Блок опред ления знака и кода приращений состо ит из реверсивного счетчика 6, мно повходового элемента 7 И и триггеров и 49. Выходной сигнал пода на входную шину 50. Входной сигнал снимается с выходной шины 51. Принцип работы умножителя заключается в следующем. Импульсы от генератора 2 частоты fg поступают на вход делителя k, коэффициент деления которого равен коэффициенту умножения устройства, и на реверсивный счетчик 6 блока 9 в который сигналом с выхода блока 1 переписан код N.,, зафиксированный в делителе Ц и первом счетчике 37 блока 3 после первого периода f . Реверсивный счетчик 6 включен для работы в режиме вычитания импульсов Импульсы с выхода делителя k, частота следования которых равна fp/K поступают на вход счетчика 37 блока 3. За период Ъ. входного сигнала Вч формируемый блоком 1, в : счетчике 37 зафиксируется число импульсов N равное целой части от деления N/K, в делителе k зафиксируется остаток импульсов uN N-NK, а в реверсивном счетчике б зафиксируется код Ngy 8X2.) равный разности кодов, полученных в первом и во втором периоде, В конце периода ЙХа с блока 1 сначала переписывает полученные значения кодов UN из делителя k в регистр 31 умножителя 6, N из счетчика 37 в регистр 39, ДМх( из реверсивного счетчика в регистр умножителя 7 и в регистр 11. В регистр умножителя 7, разрядность которого равна разрядности делителя k частоты, переписывается содержимсе 4лaдшиx разрядов кода ЛЩ , а в регистр 11 - старших, и код N из делителя и счетчика 37 в реверсивный счетчик 46, затем с задержкой наi; , второй сигнал с блока -. О 1 через элемент ч1 переписывает код из запоминаю1цего регистра 39-в счетчйк ЗВ блока 3 и сбрасывает в нуль делитель k и счетчик 37, подготавливая последние к новому заполнению в следующий период Т, Если период J от периода,к периоду не изменяется, т.е. д , то коррекция.динамической погрешности расстановки выходных импульсов в устройстве не осуществляется, при этом на входах элементов 2-N и на входе ключа 8 присутствуют уровни сигналов, которые свободно пропускают сигналы с младших разрядов второго счетчика 38 на вход элемента 39 и не запрещают прохождение импульсов от генератора 2 через ключ 8. Выходные импульсы блока 3 появляются на выходе элемента Q каждый раз, как только счетчик 38 переходит в нулевое состояние, на вычитакхчий вход которого через ключ 8. подаются импульсы от генератора .2. Каждым выходным импульсом блока 3 код N переписывается из регистра 39 в счетчик 38 и процесс вычитания повторяется. Выходные импульсы расставляются равномерно только при N кратном К, т.е. прйДМ 0. При элементы 33-N закрыты и частота сигнала на выходе умножителя 6 (выход элемента 35) равна нулю, так как часто-. та на выходе умножителя 6 определяется соотношение г - f AV о вых частота сигнала на выходе умножителя 6, значение кода в регистре частота, подаваемая на вхо счетчика 29, разрядность счетчика 29. При этом одновибратор 10 не вырабатывает запрещающий импульс и импульсы с генератора 2 свободно посту пают через ключ 8 на вход счетчика 38. При &N(.,0 для повышения точности умножения умножитель 6 осуществляет коррекцию расстановки выходных импульсов блока 3 по времени периода 7р. Необходимо осуществить коррекцию периода следования AN импульсов на выходе устройства. Причем эта кор рекция должна осуществляться равномерно за время Т. Если, например, величина коэффициента умножения и , то коррекции подлежит каждый восьмой импульс на выходе устрой ства. Коррекция заключается в увеличении периода следования каждого вос мого импульса на величину Т.. Счетчи or, т1 D 29 и регистр 31 имеют разрядность такую же как и делитель 4, поэтому при поступлении на, вход счетчика 29 К импульсов на выходе умножителя мируется AN импульсов (при и это 4-й, 12-й, 20-й,..., бО-й импульсы). Каждый из импульсов с выхода умножителя b запускает одновиб, ратор 10, который выдает единичный импульс длительностью Т, запрещая прохождение через ключ 8 очередного импульса с генератора 2 на вход второго счетчика 38 блока 3, что приводит к увеличению периода следования выходных импульсов на выходе умножителя на величину TQ. В результате смещение реально существующих импульсов относительно идеально расставленных не превысит величины J, Сброс счетчика 29, также как и делителя 4, осуществляется со второг выхода блока 1 управления. Выходные импульсы расставлены равномерно только при . Если пе риод ( 0) то р устройстве осуществляется коррекция динамической погрешности расстановки выходных импульсов внутри периода Tg. Коррек ция производится следующим образом. Если ТА ГРУ , то реверсивный счетчик t6 блока 9 успеет обнулиться и, сигнал с выхода элемента установит в единичное состояние триггер В блока 9, переключив тем самым реверсивный счетчик k( для работы в режиме слежения. За оставшийся промежуток времени в реверсивном счетчике 46 зафиксируется код д Ёcли Т Тр), JP обнуления не про- исходит, триггер остается в исходном состоянии, а в реверсивном счетчике i«6 остается код дМ g. По окончании периода дМ указанным образом пОсигналу с первого выхода блока 1 управления переписы- . веется в регистр умножителя 7 и в регистр 11. По этому же сигналу состояние триггера 48 запоминается на триггере 49. Таким образом, знак приращения входного периода определяет состояние триггера 49, выходные уровни которого используются для управления коррекцией динамической погрешности расстановки выходных импульсов. Сигналом с второго выхода блока 1 триггер 48 сбрасывается в исходное состояние и схема готова для i. i., ., i -г «««числения ,J. Таким , блок 9 определяет код приращения периода AN/i и его знак. /Для уменьшения динамической погрешности умножения частоты необходиМО осуществить равномерную за время коррекцию периодов следования , импульсов на выходе устройства в зависимости от UN. Если/ AM, I К, то такую коррекцию можно осуществить с помощью двоичного умножителя. При этом при положительном знаке лМ, что соответствует увеличению периода IW/i коррекция заключается в увеличении периода следования выходных импульсов на величину TQ при отрицательном знаке дН (Т.,.Т-„) коррекция заключается в уменьшении периода следования bN выходных импульсов на величину Tj,. Если f Д Н, (К то, очевидно, коррекции в зависимости от знака uN на величину +Т необходимо подвергать каждый период К выходных импульсов устройства. Если , гдеm l,2,3... то каждый период К выходных импульсов ycfpoйcтвa также в зависимости от знака AN-i необходимо корректировать на . Если , имеет промежуточные значения шК (т+1)К, то коррекцию можно представи/ь в виде двух составляю1цих:

постоянной коррекции, осуществляющей увеличение или уменьшение в зависимости от знака ДМ каждого из К выходных периодов умножителя за время Т„ на постоянную величину тТо , и переменной коррекции, осу1чествля10щей равномерную за время Тр51. коррекцию периодов следования /д1,-| -тК импульсов на выходе устройства на величину Т в зависимости от знака ЬЦ . Если, например, ,7 то коррекции на постоянную величину Тд, так как m«t подлежит каждый выходной импульс на выходе устройства, а переменной коррекции подлежит выходных импульсов. При этом корректирование должно происходить равномерно за время т.е. корректироваться должен каждый восьмой импульс на выходе .устройства,

Переменная коррекция в устройстве осуществляется при помощи умножителя 7, в регистр записывается код из младших разрядов реверсивного счетчика 6, соответствующий числу . Постоянная коррекция осуществляется при помощи регистра 11, в который записывается код из старших разрядов реверсивного счетчика , соответствую1чий числу т. Если вуи то на прямом и инверсном выходах триггера 9 блока 9 устанавливаются уровни, соответственно открывающие элементы 2k, 25 и закрывающие элементы 2б, 27. Импу-льсы с выхода устройства проходят через элемент 2k, 21 и 16 на вход умножителя 7, на выходе которого формируется AN -тК импульсов (при АК, и , это -й, 12-й, 20-й,...60-й импульсы). Эти импульсы через открытый элемент 25 и 15 поступают на вход одновибратора 10, который выдает единичный импульс длительностью TQ запрещая прохождение через ключ. 8 одного импульса с генератора 2 на вход счетчика 38 блока 3, что приводит к увеличению периода следования выходного импульса устройства на величину TO. Время задержки элемента 21 выбирается таким образом, чтобы переменная коррекция по динамике осуществлялась после осуществления коррекции по остатку ДН.

Импульсы-с элемента 21 через элемент 20 поступают на синхровход счетчика 2, переписывая в него код из регистра 11, соответствующий числу т, и на второй вход триггера 17, который

переключается и по прямому выходу закрывает ключ 8, а по инверсному выходу открывает элемент 28, через который на вычитакнций вхдд счетчика 12 поступают импульсы с генератора 2. При обнулении счетчика 12, которое нас:тупит через время тТ на выходе элемента 14 появится импульс, который вернет триггер 17 в исходное состояние, при котором ключ 8 откроется, а элемент 28 закроется, не проуская на вход счетчика 12 импульсы опорной частоты. Таким образом, ключ: 8 по каждому выходному импульсу устройства закрывается на время птТ , апрещая прохождение на счетчик 38

импульсов опорной частоты, что приведет к увеличению периода следования

каждого выходного импульса устройст- ; ва на постоянную величину тТ, так как на вторых входах элементов 42-N присутствуют разрешаю1чие уровни с азрядных выходов реверсивного счетчика 13. Время задержки элемента 20

выбирается таким образом, чтобы постоянная коррекция по динамике осуествлялась после переменной коррекции.Если то триггер Э блока 9 закрывсэет элементы 2k и 25 и открывает элементы 26 и 27. Импульсы с выхода устройства проходят через элемент 26 на синхровходреверсиВного счетчика, переписывая в него код из регистра 11, соответствующий числу т, и через элемент 22 и элемент 16 на счетный вход умножителя 7. Если А N, , то на выходе, умножителя 7 частота сигнала равна нулю и на выходе элемента 27 импульсов нет. Следовательно, к коду реверсивного счетчика 13 единица не прибавляется и не вычитается, так как на суммирующий вход счетчика 12 импульсы не поступают, а триггер 18 находится в исходном состоянии и закрывает элемент 23, не пропуская на вычитащий вход реверсивного счетчика 13 выходные импульсы устройства.

В соответствии с кодом числа m в реверсивном счетчике 13 закрыты соответствующие элементы , запреая прохо)|(дение сигналов с соответствую1чих младших разрядов счетчика 38 блока 3 В результате импульс на выходе элемента kQ появится ранье на величину тТо. Так как за пеиод умножения m не меняется, то пе-1 риод следования каждого выходного импульса устройства уменьшен на постоянную величину тТр. Если то на выходе умножителя 7 сформируется ANj,-mK импульсов при поступлении на его вход К выходных импуль сов yctportcTsa, Каждый выходной импульс через элемент И 27 прибавляется к коду реверсивного счетчика 13, увеличивая его на единицу, и переключает триггер 18, который открывает элемент 23. При появлении выходного импульса устройства через открытый элемент 23 из кода реверсив ного счетчика 13 вычитается единица, после чего через некоторое аремя, определяемое временем задер ки элемента 19, триггер 18 вернется в исходное состояние, закрывая элемент 23. Таким образом, при появлении импульса на выходе умножителя 7, код в реверсивном счетчике 13 соответствует числу рц-1 , а при отсутствии импульса - числу т. При коде пн-1 закрыты соответствующие элементы 42-N, в результате чего период следования выходного импульса устройства уменьшен на величину {m+DTc Таким образом в устройстве осуществляется постоянная и переменная коррекция. Устройство осуи ествляет кусочнолинейную экстраполяцию периода, откорректированное значение периода f определяется выражением Toy .T4)U+( ) Допустимое изменение uT, не ограничено величиной I (К-1) То( -что не ограничивает динамический диапазон изменения частоты входного сигнала. Коррекция динамической погрешности расстановки выходных импульсов осущестрзляется равномерно за определенный в результате экстраполяции период Tgy,, . В результате ди намическая составляющая погрешности расстановки выходных импульсов не превышает величины ГО}), что уменьшает динамическую погрешность умножения частоты. Сочетание двух коррек ций, по остатку jCiN и noukN, учитывающее динамическое изменение частоты входного сигнала, в устройст дает максимальное смещение реально следующих на выходе устройства импульсов относительно идеально расста вленных не более, чем на I2То( в пре делах периода Т, АбсЛэлютная погрешность определения периода J равна Atg,Tg,-T,y, Т ц -2Те-,+Т и ьТбт 5гЛТвх. При превышёнии /лtgy l величины Т на выходе устройства может быть потерян один последний импульс в конце периодагенерации или может сгенерирозаться два рядом стоящих импульса, что умен1. шает точность умножения. Для ис Л о-чения этого пдложения в устройстве предназначен блок 5 коррекции ошибки который работает следующим образом Выходные импульсы блока 3 с выхода элемента 0 проходят через элемент 44 на выход устройства и на счетный вход триггера 5, установленного Е нулевое состояние импульсом со второго выхода блока 1 управления в начале периода -. Если к концу периода Tjjy на выход, устройства пройдег четное (нечетное) количестес .;.;пуг;.; сов при четном (нечетном) коэгИ - т енте умножения, то нулевой cHrrsiji ;,; прямого (инверсного) выхода триггерй 5 закроет элемент k3 и не пропустит ригнал с первого выхода блока 1 на выход устройства. В противном случает элемент 3 открыт единичным сиг™ налом с триггера 5 и в выходную последовательность импульсов вставится дополнительный импульс с первого выхода блока 1 управления нй место потерянного в результате уменьшенмя периода периода к периоду на величину, превышающую Т. Таким образом, описанное техничес кое решение позволяет расширить динамический диапазон изменения частоты входного сигнала и уменьшить динзмическую погрешность умножения частоты . Формула изобретения 1. Умножитель частоты следования импульсов, содержащий блок управления, вход которого соединен с входной шиной, первый выход соединен с первыми входами блока умножения и блока коррекции ошибки, а втО|.. ку ход соединен с первым входом де;лите ля частоты, вторым и третьим входами блока умножения и вторым входом блока коррекции ошибки, третий вход которого соединен с выходом блока умножения, четвертый вход которого соединен с выходом делителя частоты,а пятый вход подключен к выходу ключа,, первый вход которого соединен с выходом генератора опорной частоты и вто рым входом делителя частоты, счетчик выходы которого поразрядно соейинень; с входами многовходового элемента И, реверсивный счетчик, элемент ИЛИ, элемент задержки, триггер и три двух входовых элемента И, о т.л и ч а ю 14 и и с я тем, Mto, с целью расширения динамического диапазона изме нений частоты выходного сигнала и уменьшения динамической погрешности, в него введены регистр, три элемента задержки, три элемента И, элемент ИЛИ, одновибратор, триггер, блок определения знака и кода приращений пе риода и два двоичных умножителя, пер вые входы которых соединены с первым выходом блокЭуправления, первым и вторым входами блока определения зна ка и кода приращений периода и первы входом регистра, остальные входы которого соединены с разрядными выхода ми блока определения знака и кода пр ращений периода а выходы регистра соединены поразрядно с входами счетчика и входами ре&ерсивного счетчика выходы которого поразрядно соединены с остальныгИ входами блока умножения, выходы разрядов которого соединены с соответствухнчими входами разрядов блока определения знака и кода приращений периода, третий вход которого соединен с выходом генератора опорной частоты, четвертый вход подключен к второму выходу блока управления и второму входу первого двоичного умножителя, третий вход которого соединён с первыми входами первого и второго двухвходовых элементов И, с входом первого элемента задержки и выходом блока коррекции ошибки, остальные первого двоичного умножителя подключены поразрядно j выходам делителя частоты, а выход первого двоичного умножителя через последовательно соединенные первый элемент ИЛИ, второй вход которого сое :динен с выходом третьего элемента И, и одноёибратор соединен с вторьй входом ключа, третий вход которого соединен с первым выходом первого триггера, первый вход которого соединен с выходом многовходового элемента И, а второй вход соединен с первым входом счетчика и через после довательно соединенные второй и третий элементы задержки подключен к вы :ходу второго,элемента И, первый вход которого соединен с первым входом четвертого элемента И, выход которого соединен с первым входом реверсивного счетчика непосредственно и с первым входом второго элемента ИЛИ через четвертый элемент задержки, второй вход второго элемента ИЛИ соединен с выходом третьего элемента за.держки, а выход второго элемента ИЛИ соединен с вторым входом второго двоичного умножителя, выход которого подключен к первым входам третьего и пятого элементов И, вторые входы которых соединены с вторыми входами соответственно второго и четвертого элементов И и с cooTBefствующими выхр--i дами блока определения знака и кода приращений периода, причем выход пятого элемента И соединен с вторым , входом реверсивного счетчика и n pBhiM входом второго триггера, второй вход которого подключен к выходу первого элемента задержки, а выход соединен с вторым входом первого элемента И, ВЫХОД которого соединен с третьим входом реверсивного счетчика, при этом второй вход счетчика соединен с выходом шестого элемента И, входы которого соединены с выходом генера-; тора опорной.частоты и вторым выходом первого триггера. 2.Умножитель по п. 1, о т л и 4 а ющ и и с я тем,, что блок определения знака и кода приращений периода содержит поразрядно соединенные реверсивный счетчик и многовходовой элемент И, и два триггера, входы первого из которых соединены с выходом многовходового элемента И и четбертым входом блока определения знака и койа приращений период, а первый выход соединен с первым входом второго триггера и первым входом реверсивного счетчика, второй вход которого подключен к второму выходу первого триггера, а третий и четвертый входы реверсивного счетчика соединены соответственно с первым и третьим входами блока определения знака и кода приращений пери ода, второй вход которого соединен свторым входом второго триггера, выходы которого подключены к выходам блока определения знака и кода приращений периода. 3.Умножитель по п. 1, отличающийся тем, что каждый двоичный умножитель содержит,счетчик и регистр, выходы которых поразрядно соединены с входами элементов И, выходы которых соединены с входами элемента ИЛИ, выход которого явля.|59668 816

ется выходом двоичного умножителя, 1, Авторское свидетельство СССР входы которого соединены соответст- № 82lt i 0, кл, Н 03 К 23/00, .79. венно с входами счетчика и регистра. 2. Авторское свидетельство СССР

Источники информации, по заявке № 2725988/l8-21, принятые во внимание при экспертизе , $ кл. Н Q3 К 23/02, 1,02.79.

| название | год | авторы | номер документа |

|---|---|---|---|

| Следящий умножитель частоты | 1979 |

|

SU832556A1 |

| Экстраполирующий умножитель частоты | 1987 |

|

SU1497706A1 |

| Умножитель частоты импульсов | 1978 |

|

SU780175A1 |

| Умножитель частоты | 1985 |

|

SU1305822A1 |

| Устройство для измерения нестабильности частоты | 1987 |

|

SU1442928A1 |

| Цифровой многоточечный измерительный мост | 1980 |

|

SU938164A1 |

| Цифровой умножитель частоты | 1983 |

|

SU1164857A1 |

| Самонастраивающееся устройство управления | 1983 |

|

SU1130830A1 |

| Интегратор азимутных импульсов | 1977 |

|

SU732907A1 |

| Манипулятор частоты без разрыва фазы | 1987 |

|

SU1515384A1 |

Авторы

Даты

1982-10-15—Публикация

1981-03-03—Подача