1

Изобретение относится к запоминающим устройствам.

Известно устройство/ позволяющее контролировать такой процесс сдвига информации, при котором осуществляется автоматическая коррекция оТиибок срабатывания триггерных элементов, обусловленных сбоем, а также вырабатывается специальный сигнал в случае отказа в работе триггеров 1

Недостатком этого устройства является то, что коррекция сдвигов, относящаяся только к одному регистру, не позволяет осуществлять функционально надежную работу всего устройства.

Наиболее близким техническим решением к предлагаемому изобретению является запоминающее устройство, содержащее регистры сдвига, одни входы которых подключены к соответствуюишм полусумматорам, а выходы к логической схеме, дополнительный регистр, входы которого подключены к управляющим шинам устройства, тригер, входы которого подсоединены к первой управляющей шине и к выходу дополнительного регистра, а выход - к одному из входов элемента И, другой вход которого подключен

ко второй управляквдей шине, а выход - к другим входам регистров сдвига 1.21.

Однако в этом запоминающем устройстве не предусматривается коррекция относительного смещения информации в регистрах сдвига (например, в случае относительного сдвига информации в двух и более регистрах

0 исправление относительного смещения невозможно) . Кроме того,устройство непозволяет осуществлять совмещение периодической диагностики накопителя и хранение в нем информации. Указанные недостатки снижают надежность устройства.

Цель изобретения - повышение надежности устройства.

Поставленная цель достигается тем, что в запоминакячее устройство с коррекцией ошибок , содержащее входной и выходной регистры числа, регистры сдвига, две группы элементов И, адресный блок, генератор сдвигающих импульсов и первый блок местного управления, причем первые входы элементов И первой группы, подключены к выходам входного регистра числа, вторые входы - к одним 0 из выходов адресного блока, другой.

ыход которого соединен с первыми правляющими входами элементов И торой группы, выходы которых подлючены ко входам выходного региста числа, выходы первого блока местного управления соединены соответственно с первым входом адресного блока и входом генератора сдвигающих импульсов, введены генератор маркерных импульсов, регистр маркера, группу элементов ИЛИ, второй блок местного управления и элемент ИЛИ, причем первые входы элементов ИЛИ подключены к выходу генера-, тора маркерных импульсов, вторые и третьи входы элементов ИЛИ группы соединены соответственно с выходами элементов И первой группы и регистров сдвига, информационные входы которых соединены с выходами элементов ИЛИ группы, второй вход элемента ИЛИ подключен.к выходу регистра маркера, информационный вход которого соединен с выходом элемента ИЛИ, выходы регистров сдвига подключены к информационным входам элементов И второй группы, входы второго блока местного управЛения подключены соответственно к выходу генератора сдвигающих импульсов и выходам регистров сдвига, а-выходы - ко второму входу адресного блока, управляющим входам регистров сдвига и регистра маркера, вторым управляющим входам элементов И второй группы и входу генератора маркерных импульсов.

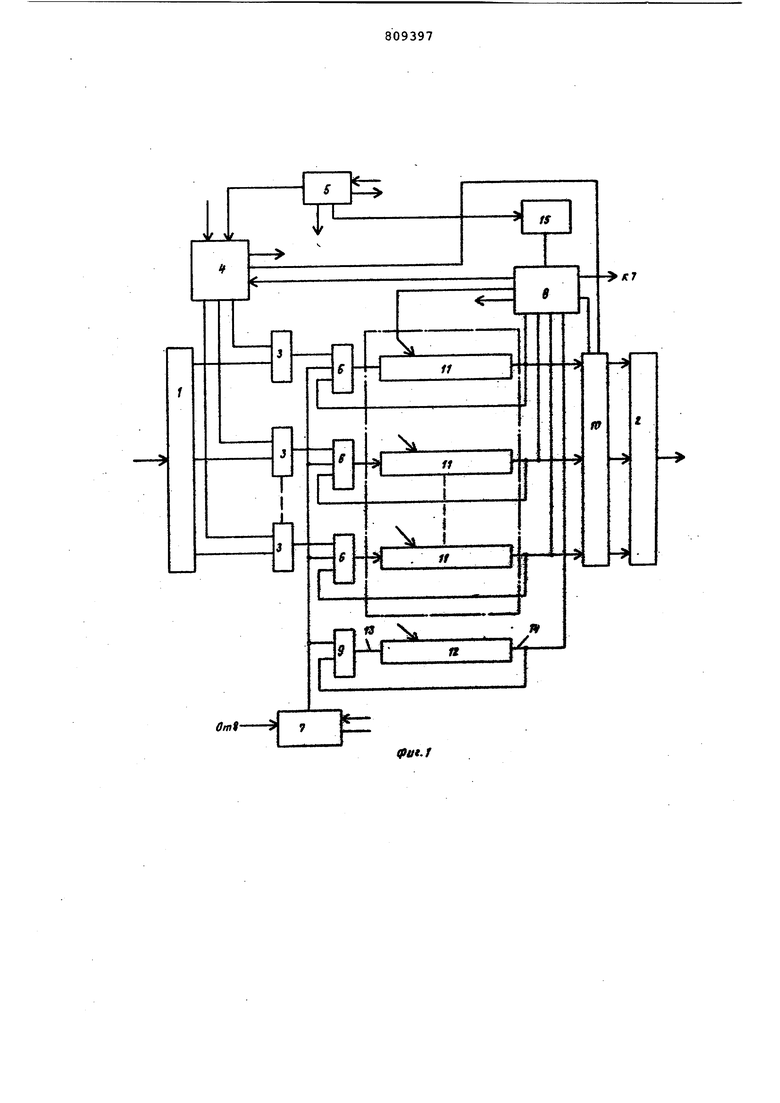

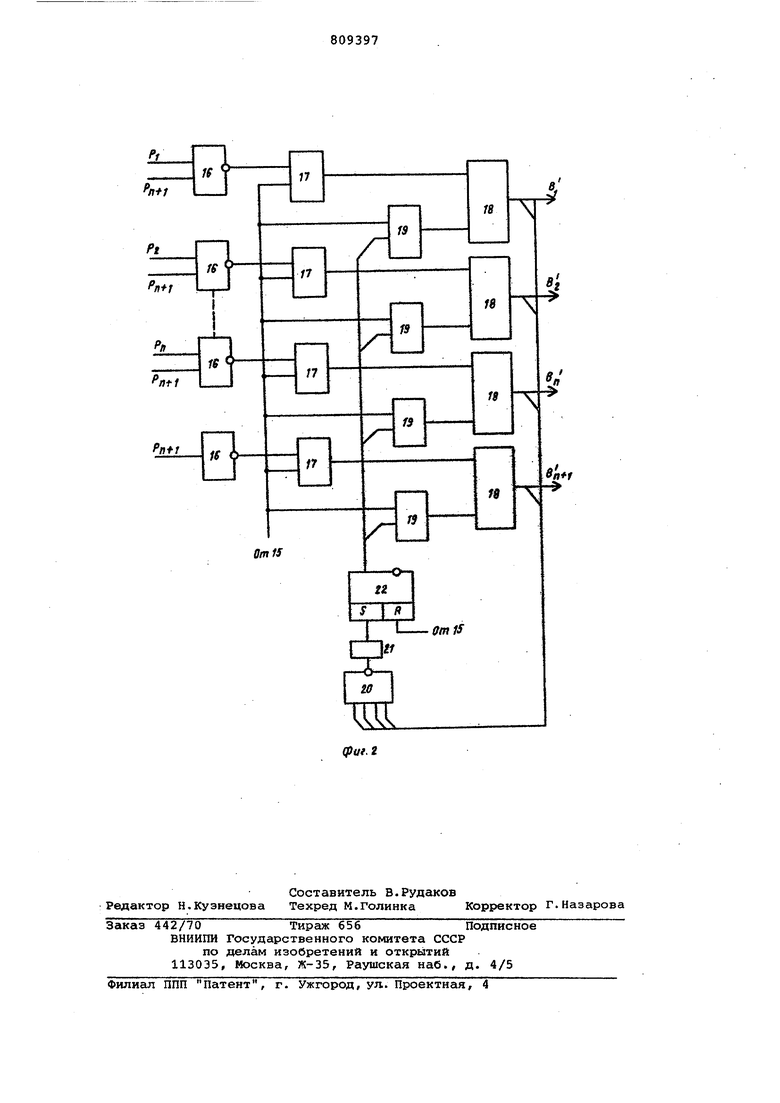

При этом второй блок местного управления целесообразно выполнить в виде блока, содержащего элементы И-НЕ, две группы элементов И, элемент ИЛИ-HR, элемент задержки, триггер и элементы ИЛИ, причем первые входы элементов И первой группы подключены к выходам элементов И-НЕ, а выходы к одним из входов элементов ИЛИ, другие входы которых подключены к выходам элементов И второй группы,- первые входы которых соединены с выходом триггера, первый вход которого через элемент задержки соединен с выходом элемента ИЛИ-НЕ, входы которого подключены к выходам элементов ИЛИ, входы элементов И-НЕ, вторые входы элементов И И триггера подключены ко входам второго блока местного управления, выходы которого соединены с выходами элементов ИЛИ. На фиг. 1 изображена структурная схема запоминающего устройства (ЗУ) с коррекцией ошибок; на фиг. 2 структурная схема второго блока управления.

Устройство содержит (фиг. 1) входной 1 и выходной 2 регистры числа, первую группу элементов 3 И, адресный блок 4, первый блок 5 местного управления, группу элементов 6 ИЛИ, генератор 7 маркерных импульсов.

второй блок 8 местного управления, элемент 9 ИЛИ, вторую группу элементов 10 И, регистры 11 сдвига, регистр 12 маркера, имеющий информационный вход 13 и выход 14, генератор 15 сдвигающих импульсов.

Первые входы элементов 3 И перво

группы подключены к выходам регистра 1, вторые входы - к одним из выходов адресного блока 5, другой выход которого соединен с первыми управляющими входами элементов 10 И второй группы, выходы которых подключены ко входам регистра 2, выходы первого блока 5 местного управления соединены-соответственно с первым входом адресного блока 4 и входом генератора 15 сдвигающих импульсов.

Первые входы элементов ИЛИ 6 и 9 подключены к выходу генератора маркернык 7 импульсов, вторые и третьи входы элементов б ИЛИ соединенысоответственно с выходами элементов 3 И и регистров 11 сдвига, информационные входы которых соединены с выходами элементов 6 ИЛИ, второй вход элемента 9 ИЛИ подключен к выходу регистра 12, информационный вход которого.-соединен с выходом элемента 9 ИЛИ, выходы регистров 11 сдвига подключены к информационным входам элементов 10 И, входы второго блока 8 местного управления подключены соответственно к выходу генератора 15 сдвигающих импульсов, и выходам регистров 11 сдвига, а выходы- ко второму входу адресного блока 4, управлятачим входам регистров 11 сдвига и маркерного регистра 12, вторым управляющим входам элементов 10 И и входу генератора 7 маркерных импульсов.

Второй блок 8 местного управлени (фиг. 2) содержит элементы 16 И-НЕ первую группу элементов 17 И, элементы 18 ИЛИ, вторую группу элементов 19 И, элемент 20 ИЛИ-НЕ, элемент 21 задержки, триггер 22.

Первые входы элементов 17 И подключены к выходам элементов 16 И-НЕ а выходы к одним из входов элементо 18 ИЛИ, другие входы которых подключены к выходам элементов 19 И, перв входы которых соединены с выходом триггера 22, первый вход которого через элемент 21 задержки соединен с выходом элемента 20 ИЛИ, входы которого подключены к выходам элементов 18 ИЛИ.

Входы элементов 16 И-НЕ, вторые входай элементов И 17 и 19 и триггера 22 подключены ко входам второго блока 15 местного управления, выход которого соединены с выходами элеметов 18 ИЛИ.

Предлагаемое ЗУ с коррекцией ошибок работает следующим образом. При обращении к ЗУ на вход блок 4 подается код адреса. При записи на вход регистра 1 по ступает информационное слово. С вых да регистра 1 информационный код по ступает (при наличии разрешающего сигнала на.выходе блока 4) через элементы 3 И и элементы б ИЛИ на вх ды регистров 11. По окончании запис всей информации в регистрах 11 и 12 происходит запись маркерных сигналов. Это осу ;ествляется генератором 7 соответственно через элементы ИЛИ 6 и 9. В качестве контрольных импульсов, записываемых в регистр 12, может использоваться определенная последовательность двоич ных цифр, например 111...11. Сдвиг информации в каждом регистре 11 осу ществляется отдельно с помощью сдви говых импульсов, поступающих с блок 8, который управляет поступлением синхроимпульсов с генератора 15 на каждый из регистров 11 и 12. В режиме хранения информация в регистрах 11 и 12 постоянно циркули рует по замкнутой цепи, связывающе1й выход каждого регистра с одним из входов элементов И 6 и 9. Допустим, что в регистре 11 сдви га произошел сбой при сдвиге информации. В этом случае в работе одного из п регистров 11, например i-ro (), блок 8 блокирует сдвиг информации во всех регистрс1Х, кроме i-ro. В блоке 8 осуществляется срав нение содержимого каждого разряда регистра 11 сдвига с содержимым ре-:гистра 12 и осуществляется выравнивание взаимного сдвига информации. При сравнении приоритет принадлежит регистру 12. Блок 8 управления сдвиговыми импульсами работает следующим образом (фиг. 2). Для i-го разряда в блоке В в информационном слове возможны следующие варианты1.Р, 0, где Р - сигнал на входе блока 8. Это означает, что сдвига информации в I-том регистре не имеется. На i-м выходе блока 8 имеется сдвиговый импульс В, осуществляющий сдвиг содержимого i-ro разряда. 2. . Данный набор свидетельствует, о сбое в i-м регистре 11. Предполагаем, что контрольный регистр работает без сбоя (это предположение не влияет на порядок общего функционирования. ЗУ). Как и в случае 1, выполнени условия P 0 и вызывает появление импульсов сдвига на 1-том регист ре. 3.Р) 1, Данный случай фактически соответствует случаю, когда отсутствует проверка на сдвиг. При этом производится выдача импульса В блоком 8. 4.. Р,,, Такой случай предполагает режим контроля работы ЗУ на сбой. При этом элементы 16 И-НЕ и элементы 17 И закрыты. На выходе элементов 18 ИЛИ нет сигнала Bt. На выходе элемента 20 ИЛИ-НЕ имеется сигнал, который после некоторой задержки (t задержки t такта сдвига) в элементе задержки 21 устанавливается триггер 22 в единичное состояние. Элемент 19 И открывается и на выходе блока 8 появляются сдвиговые импульсы. Так блок 8 работает до тех пор, пока не пройдут все контрольные единичные импульсы в регистре 12. При чтении информации в случае отсутствия взаимного сдвига код с выхода регистров 23 поступает на элементы 10 И и при наличии разрешающего сигнала с блока 4 (при отсутствии взаимного сдвига) с блока 8 осуществляется считывание достоверной информации в регистр 2. Чтение при ошибочном сдвиге информации осуществляется следующим образом. От генератора 15, управляемого блоком 8, подается сигнал, по которому происходит сдвиг на один разряд в том регистре 11, где произошел сбой. А в остальных регистрах 11 сдвиг в это время не происходит. Это позволяет осуществить выравнивание взаимного сдвига информации и темх:амым осуществить надежное хранение информации. Таким образом, предлагаемое устройство позволяет исправлять влияние ошибок, вызванных взаимным сдвигом информации в регистрах, т.е. обладает повышенной надежностью по сравнению с известным ЗУ. Формула изобретения 1. Запоминающее устройство с коррекией ошибок, содержащеевходной и ыходной регистры числа, регистры двига, две группы элементов И, адресый блок, генератор сдвигающих имульсов и первый блок местного упавления, причем первые входы элеменов И первой группы подключены к выодам входного регистра числа, втоые входы - к одним из выходов адесного блока, другой выход которого оединен с первыми управляющими вхоами элементов И второй группы, выхоы которых подключены ко входам выходого регистра числа, выходы первого лока местного управления соединены оответственно с первым входом адрес- ого блока и входом генератора сдвигакячих импульсов, отличающееся тем, что, с целью повышения надежности устройства, оно содер.жит генератор маркерных импульсов, регистр маркера, группу элементов ИЛИ, второй блок местного управления и элемент ИЛИ, причем первые входы элементов ИЛИ подключены к выходу генератора маркерных импульсов, вторые и третьи входы элементов ИЛИ группы соединены соответственно с выходами элементов И первой группы и регистров сдвига, информационные входы которых соединены с выходами элементов ИЛИ группы, второй вход элемента ИЛИ подключен к выходу регистра маркера информационный вход которого соединен- с выходом элемента ИЛИ, выходы регистров сдвига подключены к информационным входам элементов И второй группы, входы второго блока местного управления подключены соответственно к выходу генератора сдвигающих импульсов и выходам регистров сдвига, а выходы/- ко второму входу адресного блока, управляющим входам регистров сдвига и регистра маркера, вторым управляющим входам элементов И второй группы и входу генератора маркерных импульсов.

2. Устройство по п. 1, отличающееся тем, что второй блок местного управления содержит элементы И-НЕ, две группы элементов -И, элементы ИЛИ-НЕ, элемент задержки, триггер и элементы ИЛИ, причем первые входы элементов И первой группы подключены к выходам элементов И-НЕ, а выходы к одним из входов элементов ИЛИ, другие входы которых подключены к выходам элементов И второй группы, первые входы которых соединены с выходом триггера, первый вход которого через элемент задержки соединен с выходом элемента ИЛИ-НЕ, входы которого подключены к выходам элементов ИЛИ, входы элементов И-НЕ, вторые входы элементов И и триггера подключены ко входс1М второго блока местного управления, выходы которого соединены с выходами элементов ИЛИ.

Источники информации, принятые во внимание при экспертизе

1.Авторскоесвидетельство СССР 258736, кл. G06 F 9/00, 1968.

2.Авторскоесвидетельство СССР 428454, кл. G11 С 19/00, 1972 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Ассоциативное запоминающее устройство | 1979 |

|

SU826421A1 |

| Устройство для сопряжения ЦВМ с внешними устройствами | 1989 |

|

SU1784840A1 |

| Устройство микропрограммного управления | 1982 |

|

SU1086431A1 |

| Устройство для отображения информации на экране телевизионного приемника | 1984 |

|

SU1265834A1 |

| Имитатор абонентов | 1986 |

|

SU1325490A2 |

| Имитатор абонентов | 1983 |

|

SU1291987A1 |

| Устройство для ввода информации | 1986 |

|

SU1352479A1 |

| Способ магнитной записи асинхронных потоков цифровой информации и устройство для его осуществления | 1990 |

|

SU1788520A1 |

| Способ многодорожечной цифровой магнитной записи и устройство для его осуществления | 1990 |

|

SU1732380A1 |

| Устройство для обработки запросов | 1989 |

|

SU1688248A1 |

Авторы

Даты

1981-02-28—Публикация

1979-05-14—Подача