Изобретение относится к автоматике и вычислительной технике, в частности к средствам анализа и обработки прерываний в ЭВМ и системах, и может быть использовано для динамического распределения ресурсов процессора ЭВМ или системы, работающих в режиме разделения времени.

Цель изобретения - расширение области применения устройства путем динамического распределения времени обслуживания задания в режиме разделения времени.

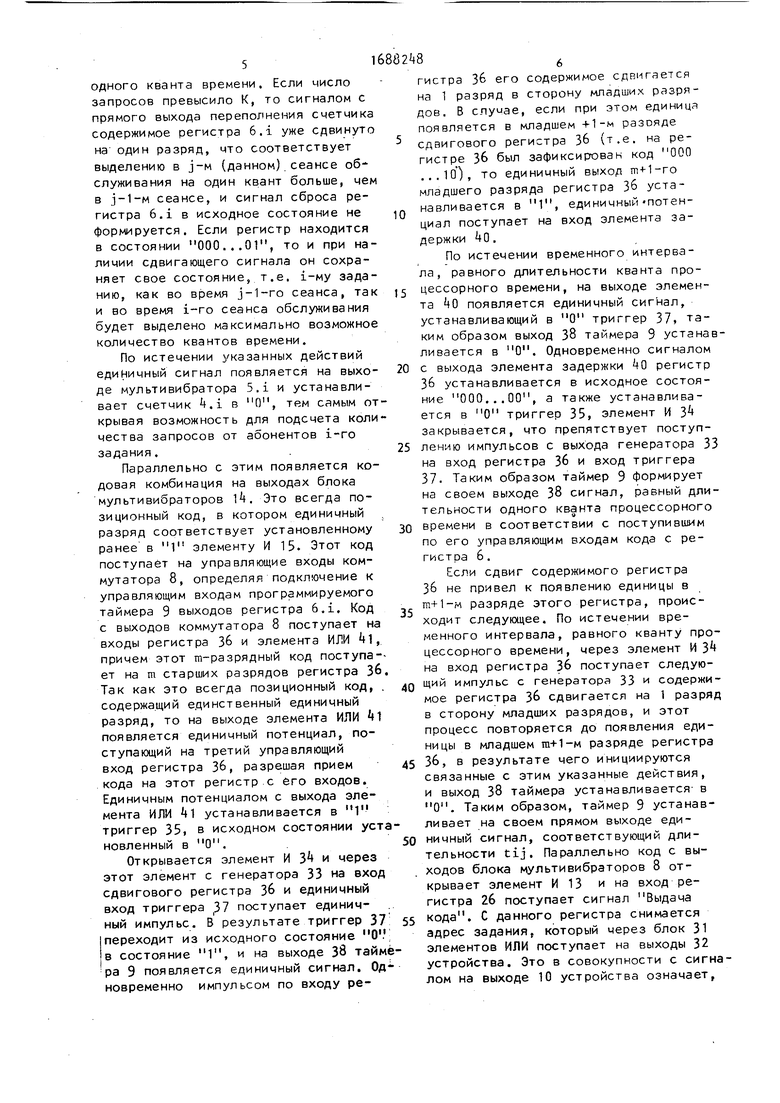

На фиг.1 представлена блок-схема устройства для обработки запросов;

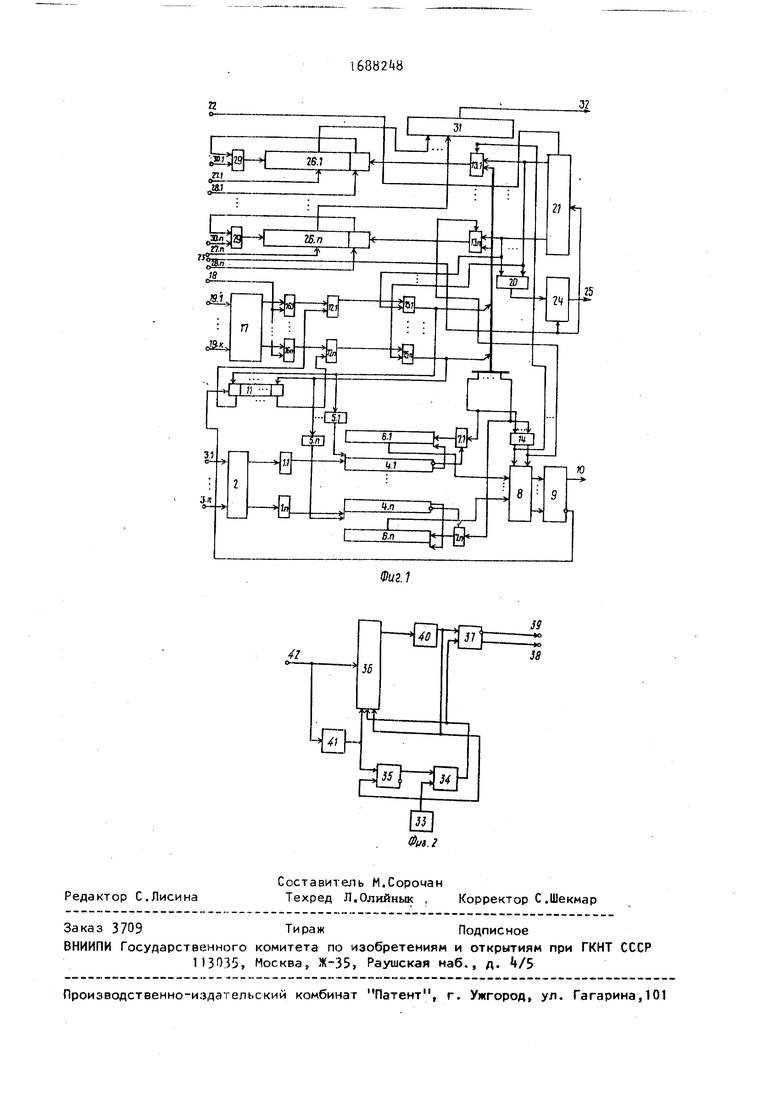

на фиг. 2 - блок-схема программируемого таймера.

Устройство содержит блок мультит- вибраторов 1.1 (i 1,гО, дешифра- тор 2, группу 5.1, , k, k Iog4n Гзапросных входов устройства, группу счетчиков 4.1, блок мультивибраторов 5.1, группу сдвиговых регистров 6.1, блок элементов И 7.1, коммутатор 8, программируемый таймер 9, сигнальный выход 10 устройства, регистр 11 сброса, группу триггеров 12.1, блок элементов И 13.1, блок мультивибраторов 14, блок элементов И 15.1, блок элементов И 16.1, дешифаоо оо to

4

оо

ратор 17, вход 18 сопровождения адреса устройства, группу входов 19Д признака готовности задания устройства, элемент ИЛИ-НЕ 20, дешифратор 21, вход 22 чтения устройства, группу адресных входов 23 устройства, блок элементе И 24, выход 25 устройства, группу регистров 26.1„ группу 27.1, входов кода адреса устройства, группу 28.1 входов установки маркера устройства, блок элементов И 2Э.1, группу 30.1 входов записи адреса устройства, блок элементов ИЛИ 319 группу выходов 32 устройства..

Программируемый таймер (фиг.2) содержит генератор 33 импульсов, эле- мент И 34, триггер 35, выход регистра 36 сдвига, триггер 37, выходы 38, элемент задержки 40, элемент ИЛИ 41, группу входов 42.

Устройство работает следующим образом.

Обрабатываемые системой в режиме разделения времени задания коллектив- но г о пользования получают запросы от абонентов на обслуживание. Эти запросы поступают на первую группу запросных входов 3 устройства и через дешифратор 2 и мультивибраторы 1 на входы счетчиков 4,

Рассмотрим счетчик 4.1, соответствующий i-му заданию, На его вход поступает импульс, вследствие чего его содержимое увеличивается на единицу. В начале работы устройства счетчики 4 установлены в 000...00,, и регистры 6 установлены в состояние 100...00. По превышении определенного числа поступивших запросов счет- чик 4.1 выдает сигнал переполнения и на вход сдвигового регистра 6.1 поступает сигнал . Состояние переполнения счетчика фиксируется до поступления управляющего сигнала сбро- са на вход счетчика 4.1, который формируется непосредственно перед началом обслуживания 1-го задания системой. Состояние регистра 6.1 определяет количество квантов времени, ко- торое будет выделено i-му заданию в следующем сеансе обслуживания его системой при условии, что на входе этого регистра 6.: . не будет сформирован сигнал сброса. Так, например, состояние ЮО.о.ОО регистра на момент f начала обслуживания определяет, что в случае, если в этот момент 1-ое задание начинает обслуживаться, то ему будет выделен один квант процессорного времени; состояние 0100...00 определяет, что 1-му заданию будет выделено 2 кванта времени и т.д.

Разрядность регистра 6 определяется исходя из конкретных условий организации вычислительного процесса - мощности процессора, максимального числа заданий в системе и т.д. Находясь в системе, задания выставляют сигнал готовности к обслуживани При поступлении на группу входов 19 признака готовности 1-го задания и наличии сигнала сопровождения адреса поступающего в устройство по входу 18, сигнал с выхода дешифратора 17 через соответствующий элемент И 16 переводит соответствующий триггер 12 в единичное состояние. Процессор ЭВМ работая в режиме разделения времени, генерирует адрес зоны или раздела памяти, обслуживающей соответствующее задание. Этот адрес по операции Чтение, сигнал с которой поступает ко входу 22 устройства, обеспечивает блокировку в данном режиме по цепи дешифратор 21, элемент ИЛИ-НЕ 20 и блок элементов И 24 доступа к операционной памяти, где ооычно хранится таблица состояний заданий. Вместо этого анализируется состояние выходов элементов И 15.

Единичный сигнал на выходе элемента И 15 свидетельствует о том, что задание, адрес зоны памяти которого сгенерирован процессором в данном такте, готово к обслуживанию. Едничный сигнал с выхода элемента И 15 устанавливает в 1 соответствующий разряд регистра 11 сброса, а также поступает на вход блока мультивибраторов 14. Кроме того, этот сигнал поступает на вход мультивибратора 5.1, а также на второй вход элемента И 7.

В случае, если на первом входе элмента И 7 имеется единичный сигнал с инверсного выхода счетчика 4, что свидетельствует о том, что в течение временного интервала между j-1-м и данным (j-м) сеансом обслуживания 1-го задания количество запросов от абонентов не превышало константу К, на выходе элемента И 7.1 появляется единичный сигнал, сбрасывающий сдвиговый регистр в состояние 100...00 что соответствует выделению заданию

одного кванта времени. Если число запросов превысило К, то сигналом с прямого выхода переполнения счетчика содержимое регистра 6.1 уже сдвинуто на один разряд, что соответствует выделению в j-м (данном) сеансе обслуживания на один квант больше, чем в j-1-м сеансе, и сигнал сброса регистра 6.1 в исходное состояние не формируется. Если регистр находится в состоянии 000...01, то и при наличии сдвигающего сигнала он сохраняет свое состояние, т.е. i-му заданию, как во время j-1-го сеанса, так и во время 1-го сеанса обслуживания будет выделено максимально возможное количество квантов времени.

По истечении указанных действий единичный сигнал появляется на выходе мультивибратора 5.i и устанавливает счетчик 4. i в О, тем самым открывая возможность для подсчета количества запросов от абонентов 1-го задания.

Параллельно с этим появляется кодовая комбинация на выходах блока мультивибраторов И. Это всегда позиционный код, в котором единичный разряд соответствует установленному ранее в 1 элементу И 15. Этот код поступает на управляющие входы коммутатора 8, определяя подключение к управляющим входам программируемого таймера 9 выходов регистра 6.1. Код с выходов коммутатора 8 поступает на входы регистра 36 и элемента ИЛИ 1, причем этот го-разрядный код поступает на m старших разрядов регистра 3& Так как это всегда позиционный код, . содержащий единственный единичный разряд, то на выходе элемента ИЛИ Н появляется единичный потенциал, поступающий на третий управляющий вход регистра 36, разрешая прием кода на этот регистр с его входов. Единичным потенциалом с выхода элемента ИЛИ 41 устанавливается в 1 триггер 35, в исходном состоянии устновленный в О.

Открывается элемент И 3 и через этот элемент с генератора 33 на вход сдвигового регистра 36 и единичный вход триггера 37 поступает единичный импульс. В результате триггер 37 переходит из исходного состояние О1.1 в состояние 1, и на выходе 38 таймра 9 появляется единичный сигнал. Одновременно импульсом по входу ре

5

гистра 36 его содержимое сдвигается на 1 разряд в сторону младших разрядов. В случае, если при этом единица появляется в младшем +1-м разояде сдвигового регистра 36 (т.е. на регистре 36 был зафиксирован, код 000 ...10), то единичный выход т-И-го младшего разряда регистра 36 устанавливается в 1, единичный-потенциал поступает на вход элемента задержки 0.

По истечении временного интервала, равного длительности кванта процессорного времени, на выходе элемента 40 появляется единичный сигнал, устанавливающий в О триггер 37, таким образом выход 38 таймера 9 устанавливается в О. Одновременно сигналом

0

0

5

0

5

0

5

с выхода элемента задержки 0 регистр 36 устанавливается в исходное состояние 000...00, а также устанавливается в О триггер 35, элемент И 3 закрывается, что препятствует поступ- 5 лению импульсов с выхода генератора 33 на вход регистра 36 и вход триггера 37. Таким образом таймер 9 формирует на своем выходе 38 сигнал, равный длительности одного кванта процессорного времени в соответствии с поступившим по его управляющим входам кода с ре- гистоа 6.

Если сдвиг содержимого регистра 36 не привел к появлению единицы в ip.+ 1-м разряде этого регистра, происходит следующее. По истечении временного интервала, равного кванту процессорного времени, через элемент И 3 на вход регистра 36 поступает следующий импульс с генератора 33 и содержимое регистра 36 сдвигается на 1 разряд в сторону младших разрядов, и этот процесс повторяется до появления единицы в младшем rn+1-м разряде регистра 36, в результате чего инициируются связанные с этим указанные действия, и выход 38 таймера устанавливается в О. Таким образом, таймер 9 устанавливает на своем прямом выходе единичный сигнал, соответствующий длительности tij. Параллельно код с выходов блока мультивибраторов 8 открывает элемент И 13 и на вход регистра 26 поступает сигнал Выдача кода. С данного регистра снимается адрес задания, который через блок 31 элементов ИЛИ поступает на выходы 32 устройства. Это в совокупности с сигналом на выходе 10 устройства означает,

что L-e задание включено а работу сие 1емь и ему выделяется определенное количество KBSHTOEI времени.

В регистрах 26 хранятся адреса заданий, обрабатываемых в текущий момент времени системой в режиме разделения времени. По заЕ1ершении задания с номером i, на Eixope 28. i генерируется сигнал, устанавливающий в 1 маркерный младший разряд регистра 26,1, Тем самым открывается элемент И 29 и по поступлении н второй вход этого элемента сипнама по входу ЗОЛ на выходе элемента И 9 появляется единичный сигнал, разрешающий запись в регистр 26.1 адреса ноыого задания принимаемого системой к обслуживанию, Код адреса поступает на регистр 26,1 по входам 27, при этом младший, дополнительный бит код адреса устанавливает в О младший рагфяд регистра 26.1.

При считывании с регистра 26. i младший разряд -южет игнорироваться. О11 в младшем разряде регистра 26,1 запрещает запись информации в регистр 26, при этом осуществляется хранение на регистре 26 Л адреса задания или выдача этого адреса на информационные выходы регистра 26 Л, Запись первых адресэв производится следующим образом; генерируются сигналь последовательно на входз; 27 и 30.1, после чегона регистр 26.1 поступает коп.

Запись адреса нового задания на регистр 26.L может производиться сразу же после завершения 1-го задания. При этом процесс записи адреса нового задания на регистр 26 Л не влияет на текущее состояние остальных элементов устройства.

По истечении времени j-ro сеансе обслуживания единичной сигнал формируется на инверсном выходе таймера 5 и сигнал Выдача кода поступает ье вход регистра 11 сброса,, Код с его выходов восстанавливает исходное (ну левое) состояние триггера 2,1. Процессор переходит к анализу состояния следующего за „

Если задание че оыпс готово, то указанные процессы не происходят, про цессор не выделяем времени этому зада нию и тут же переходит к анализу состояния следующего задания. Формула изобретении

1. Устройство для обработки запросов, содержащее .цва дешифратора, бпок

0

5

0

5

0

35

4Г

50

5

элементов ИЛИ, три блока элементов И, элемент ИЛИ-НЕ, N регистров, группу из N триггеров (где N - число заданий), причем вход признака готовности задания устройства соединен с входом первого дешифратора, выход которого соединен с первым входом первого блока элементов И, второй вход и группа выходов которого соединены соответственно с входом сопровождения адреса устройства и единичными входами триггеров группы, выходы которых соединены с первой группой входов второго блока элементов И, выходы второго дешифратора соединены с входами элемента ИЛИ-НЕ, выход которого соединен с первым входом третьего блока элементов И, адресный вход устройства соединен с вторым входом третьего блока элементов И и информационным входом второго дешифратора, стробирующий вход которого соединен с входом чтения устройства, выходы старших разрядов регистров группы соединены с группой входов блока элементов ИЛИ, группа выходов которого является группой выходов адреса задания устройс аа, группа выходов третьего блока элементов И является адресной группой выходов устройства, отличающееся тем, что, с целью расширения области применения устройства за счет динамического распределения времени обслуживания заданий в режиме разделения времени, в него введены третий дешифратор, группа из N счетчиков, группа из N сдвиговых регистров, регистр сброса, коммутатор, программируемый таймер, с третьего по пятый блоки элементов И, с первого по третий блоки мультивибраторов, причем запросный вход устройства соединен с входом третьего дешифратора, выход которого соединен с входом первого блока мультивибраторов, группа выходов которого соединена соответственно с суммирующими входами счетчиков группы, прямые входы переполнения которых соединены с входа мм сдвига соответствующих сдвиговых регистров, выходы которых соединены с группой информационных вхо дов коммутатора, группа входов которого соединена с группой входов программируемого таймера, прямой выход которого является сигнальным выходом устройства, а инверсный соединен с входом сброса регистра сброса,

группа выходов которого соединена с входами сброса соответствующих триггеров группы, группа входов записи адреса устройства соединена с первой группой входов четвертого блока элементов И, группа выходов которого соединена с входами управления записью регистров группы, выходы младших разрядов которых соединены с второй группой входов четвертого (блока элементов И, группа входов кода адреса устройства соединена с информационными входами старших разрядов регистров группы, входы установки младших разрядов которых являются группой входов установки маркера устройства, выходы второго дешифратора соединены с второй группой входов второго блока элементов И и первой группой входов пятого блока элементов И, группа выходов которого соединена с входами управления чтением соответствующих регистров группы, выходы второго блока элементов И соединены с единичными входами регистра сброса, первыми входами шестого блока элементов И, вторыми входами пятого блока элементов И и входами второго и третьего блоков мультивибраторов, выход которого соединен с управляющим входом коммутатора и третьим входом пятого блока элемен

тов И, группа выходов второго блока мультивибраторов соединена соответственно с входами сброса счетчиков группы, инверсные выходы переполнения которых соединены с вторыми входами шестого блока элементов И соответственно, группа выходов которого соединена с входами сброса сдвиговых

j регистров группы.

2. Устройство по п. 1, о т л и - чающееся тем, что программируемый таймер содержит генератор импульсов, регистр сдвига, два тригге5 ра элементы ИЛИ, И задержки, причем группа входов программируемого таймера соединена с группой информационных входов регистра сдвига и группой входов элемента ИЛИ, выход которого соQ единен с входом записи регистра сдвига и единичным входом первого триггера, выход которого соединен с вторым входом элемента И, второй вход и выход которого соединены соответственно

5 с выходом генератора импульсов и вхо- дами установки второго триггера и сдвига регистра сдвига, выход которого через элемент задержки соединен с входами сброса первого и второго

Q триггеров и регистра сдвига, прямой и инверсный выходы второго триггера являются прямым и инверсным выходами программируемого таймера.

и

- зл

I an -{«-

| название | год | авторы | номер документа |

|---|---|---|---|

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

| Устройство для обслуживания запросов | 1988 |

|

SU1571588A1 |

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1993 |

|

RU2079876C1 |

| Устройство контроля и управления технологическим комплексом для намотки изделий | 1989 |

|

SU1661721A1 |

| Многоканальный коммутатор | 1989 |

|

SU1661986A1 |

| Устройство для сопряжения ЦВМ с внешними устройствами | 1989 |

|

SU1784840A1 |

| Устройство для отсчета времени | 1990 |

|

SU1784959A1 |

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

| УСТРОЙСТВО ДЛЯ ОТСЧЕТА ВРЕМЕНИ | 1990 |

|

RU2024920C1 |

| Устройство для программного управления намоточным станком | 1989 |

|

SU1725184A1 |

Изобретение относится к автоматике и вычислительной технике, в том числе к средствам анализа и обработки прерываний в ЭВМ и системах, и может быть использовано для динамического распределения ресурсов процессора в ЭВМ и системах, работающих в режиме разделения времени. Цель изобретения - расширение области применения устройства за счет динамического распределения времени обслуживания заданий в режиме разделения времени. Устройство для обработки запросов содержит группу регистров, группу счетчиков, три дешифратора, регистр сброса, коммутатор, программируемый таймер, шесдь блоков элементов И, три блока мультивибраторов, группу сдвиговых регистров, блок элементов ИЛИ, элемент ИЛИ-НЕ, группу триггеров. Основным принципом работы устройства является динамический анализ уровней активности заданий и выделения каждому заданию в режиме времени сеанса обслуживания соответствующей длительности, пропорциональной уровню активности данного задания. 1 з.п.ф-лы, 2 ил. S Л

| Устройство для обработки прерываний | 1979 |

|

SU873243A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для обработки запросов | 1982 |

|

SU1119013A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

Авторы

Даты

1991-10-30—Публикация

1989-08-22—Подача