ния, оно содержит (п +1) -ю, (п + 2) -ю группы элементов И, второй, третий и четвертый элементы И, элемент И-НЕ первый, второй и третий элементы задержки, одновибратор, элемент ИЛИ, элемент НЕ, причем первьй выход блок синхронизации через первый элемент задержки соединен с единичным входом первого триггера управления единичный выход которого соединен с вторым входом первого элемента И и управляющим входом управляющего регистра сдвига, первый выход управляющего регистра сдвига соединен с первым входом второго элемента И, выходы управляющего регистра сдвига с второго по (4+1)-и соединены с входами элемента И-НЕ, выход которого соединен с вторым входом второго элемента И, первым вводом третьего элемента И, через элемент НЕ - с первыми входами элементов И (п+О-й группы, а через одновибратор - с нулевым входом первого триггера управления и установочньм входом счетчика, выход первого элемента И соединен с первым входом четвертого элемента И, нулевым входом второго триггера управления, а через второй элемент задержки с входом синхронизации управляющего регистра сдвига, входом третьего элемента задержки и единичным пходом второго триггера управления, выход которого соединен с управляющими входами с первого по m-и информационных регистров сдвига, выходы кода управления блока памяти микрокоманд соединены с входами элемента ИЛИ, выход которого соединен с (1с+1)-м информационным входом управляющего регистра сдвига, выход второго элемента И соединен с первыми входами элементов И (п+2)-й группы и вторым входом четвертого элемент§ И, выход которого соединен с счетным входом счетчика, выход третьего элемента задержки соединен с вторым входом третьего.элемента И, выход которого соединен с синхронизирующими входами с первого по т-й информационных регистров сдвига, выходы элементов ИЛИ группы соединены с вторыми входами элементов И (ги-2)-й группы, выходы которы соединены с информационными входами с первого по т-й информационных регистров сдвига, выходы которых соединены со вторыми входами элементов И (п+1)-й группы, выходы которых соединены с выходами микроопераций устройства, а первый выход устройства соединен с вторым входом блока синхронизации.

2, Устройство по П.1, отличающееся тем, что блок синхронизации содеря ит триггер пуска, первый и второй генераторы импульсов, причем первый и второй входы блока соединены соответственно с единичным и нулевым входами триггера пуска, единичный выход которого соединен с уп{)авляющими входами первого и второго генератора импульсов, выходы которых подключены к первому и второму выходам блока соответственно.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство для управления обменом управляющей информацией в распределенной системе | 1986 |

|

SU1325477A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1130863A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1108448A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1319029A1 |

| Устройство для обмена данными в распределенной вычислительной системе | 1988 |

|

SU1580382A1 |

| Микропрограммный процессор | 1985 |

|

SU1275457A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1092505A1 |

| Микропрограммное устройство управления модуля вычислительной системы | 1983 |

|

SU1108447A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1030801A1 |

| Перестраиваемый микропрограммный процессор | 1981 |

|

SU983713A1 |

1. УСТРОЙСТВО МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ, содержащее формирователь адреса,-регистр адреса, первый и второй дешифраторы, блок памяти микрокоманд, буферный регистр, регистр операционных микрот команд, управляющий регистр сдвига т информационных регистров сдвига (т - число разрядов в зоне микрокоманд) п групп элементов И (п число информационных полей микрокоманды), блок синхронизации, первый и второй триггеры управления,счетчик, группу элементов ИЛИ, первый элемент И, причем входы логических условий устройства, первая и вторая группы адресных выходов буферного регистра соеди«ены соответственно с первым - третьим входами формирователя адреса, выходы которого соединены с первой группой информационных входов регистра адреса, входы кода операции устройства и третья группа адресных выходов буферного регистра соединены соответственно с второй и третьей группами информационных входов регистра адреса, выходы которого соединены с входами первого дешифратора, первый выход блока синхронизации и выходы первого дешифратора соединены соответственно .с управляющим и адресным входами блока памяти микрокоманд, выходы кода управления которого сбединены соответственно с первым - 1 -м информационным входом управляющего регистра сдвига (k-число зон в микрокоманде адресные выходы - с ° информационнюш входами буферного регистра, а выходы операционных микр команд - с информационными входами регистра операционных микрокоманд, группы выходов с первой по п-ю регистра операционных микрокоманд соединены с первыми входами элементов И соответственно с первой по п-ю группы, выходы которых сочинены с 00 входами элементов ШШ группы, вход а пуска устройства подключен к первону 4: входу блока синхронизации, первый са выход которого соединен с входами синхронизации регистра адреса, буферного регистра и регистра операционных микрокоманд, второй выход блока синхронизации соединен с первым входом первого элемента И, выходы счетчика соединены с входами Второго дешифратора, выходы с первого по п -и которого соединены со вторыми входами элементов И соответственно с первой по п-ю группы, отличающееся тем, что, с цепью сокращения объема оборудова

Изобретение относится к области автоматики и вычислительной техники и может быть использЬвано при разработке управляющих устройств для систем передачи и обработки данных с микропрогра№1ным управлением. . . Известны устройства микропрограммного управления, содержащие блок памяти микрокоманд, регистры, дешифраторы, счетчик, генератор импульсов, формирователь адреса, элементы задержки, элементы И, НЕ 11 и 2. Недостатком таких устройств является большой объем оборудования, которьй обусловлен существенной информационной избыточностью блока памяти микрокоманд, а также отсутствием средств сжатия информации и ее декодирования. Известно устро.йство микропрограммного управления, содержащее блок памяти микрокоманд, формирователь адреса, регистры, дешифраторы, генератор тактовых импульсов,триггеры управления, элементы И, элементы задержки 3.

Недостатком указанного устройства является также большая избыточность блока памяти.

В этом устройстве имеются средства, позволяющие хранить информацию в сжатом виде. Вместо полного множества кодов операционных микрокоманд в блоке памяти устройства хранятся только базовые коды, которые затем в соответствии с управляющей информацией преобразуются в требуемые коды микрокоманд. При этом осуществляется сжатие информации по числу хранимый кодов - вертикальное сжатие. Однако такая дисциплина функционирования приводит к расширению формата микрокоманд.

Кроме того, в этом случае не peaлизуется потенциальная возможность сжатия информации по числу разрядов кодов микрокоманд (горизонтальное сжатие). Существование такой возможности обусловлено малым числом единиц в кодах микрокоманд и возможностью их группирования по зонам.

Наиболее близким к предлагаемому устройству по достигаемому положительному эффекту и технической сущности является устройство микропрограммного управления, содержащее формирователь адреса, регистр адреса, первый и второй дешифраторы, блок памяти микрокоманд,, буферный регистр регистр операционных микрокоманд,управляюпщй регистр сдвига,т информационных регистров сдвига, п блоков элементов И, блок,синхронизации, первый и второй триггеры управления, счетчик, блок элементов ШШ, элемент И, причем вход логических условий устройства, первый и второй адресные входы буферного регистра соединены соответственно с первым третьим входами формирователя адре.са, выход которого соединен с первым информационным входом регистра адреса, вход кода операции устройства и третий адресный выход буферного регистра соединены соответственно с вторым и третьим информационными входами регистра адреса, выход которого соединен с входом первого . дешифратора, первый выход блока синхронизации и выход дешифратора соединены соответственно с управляющим и адресным входами блока памяти

микрокоманд, выходы кода управления которого соединены соответственно с первым - V. -м информационными входами управляющего регистра сдвига, адресные выходы - с информационными входами буферного регистра, а выход операционных микрокоманд со входом регистра операционных микрокоманд, группы выходов с перво по «г-ю регистра операционных микрокоманд соединены с информационными входами соответственно с первого по п-й блоков элементов И, выходы которых соединены с входами блока элементов ИЛИ, вход пуска устройства является первым управлякярт входом блока синхронизации, второй выход которого соединен с первым входом первого элемента И, выход счетчика соединен с входом дешифратора,первый - h -и выходы которого соединены с управляющими входами соответственно первого - п - го блоков элементов И С4 2.

Недостатком известного устройства является большой объем оборудования блока памяти микрокоманд.

Цель изoбpeteния - сокращение объема оборудования устройства микропрограммного управления.

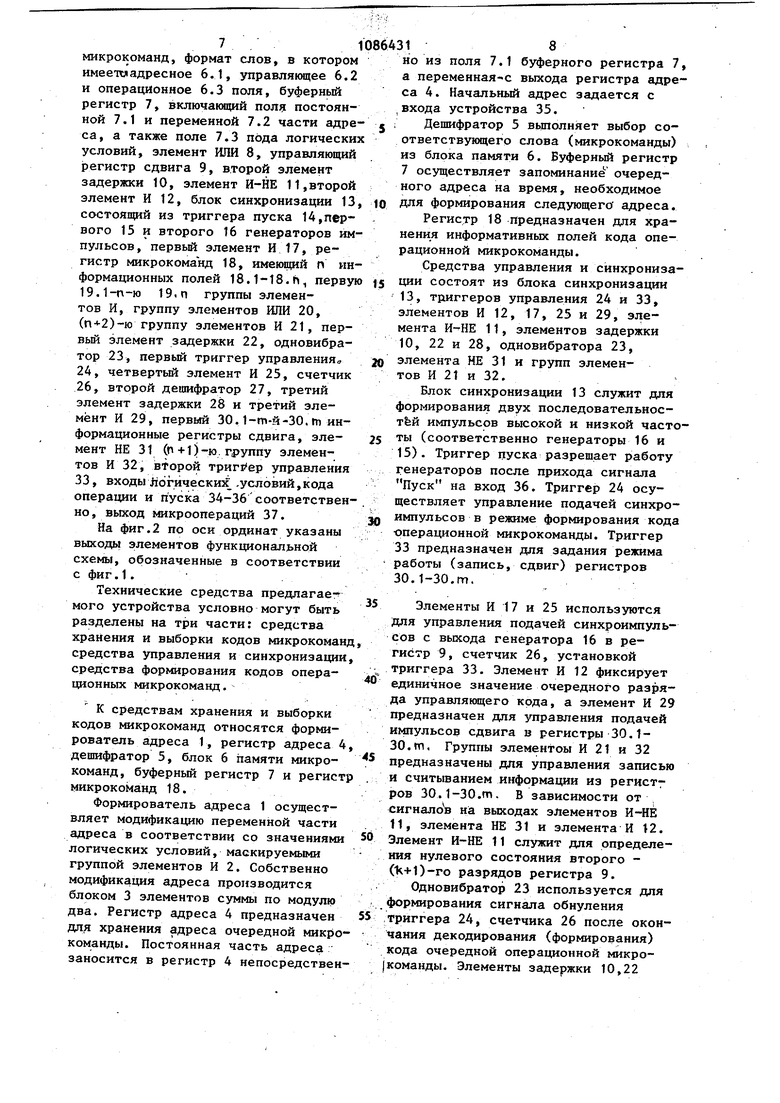

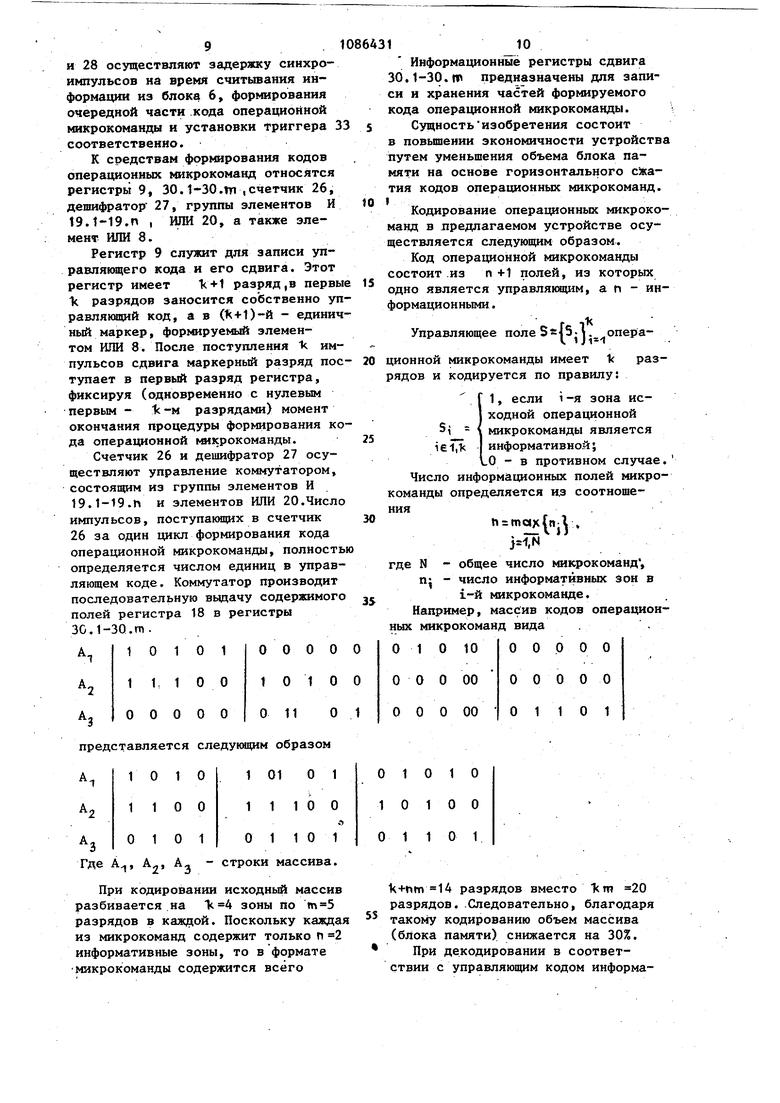

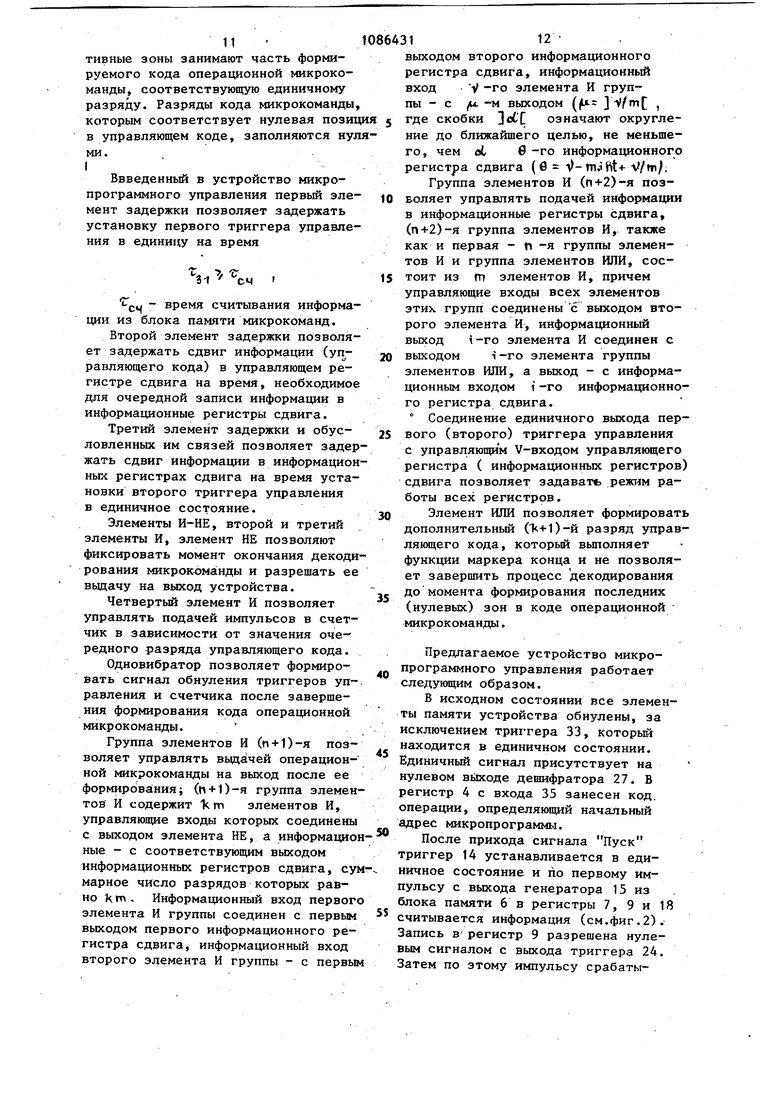

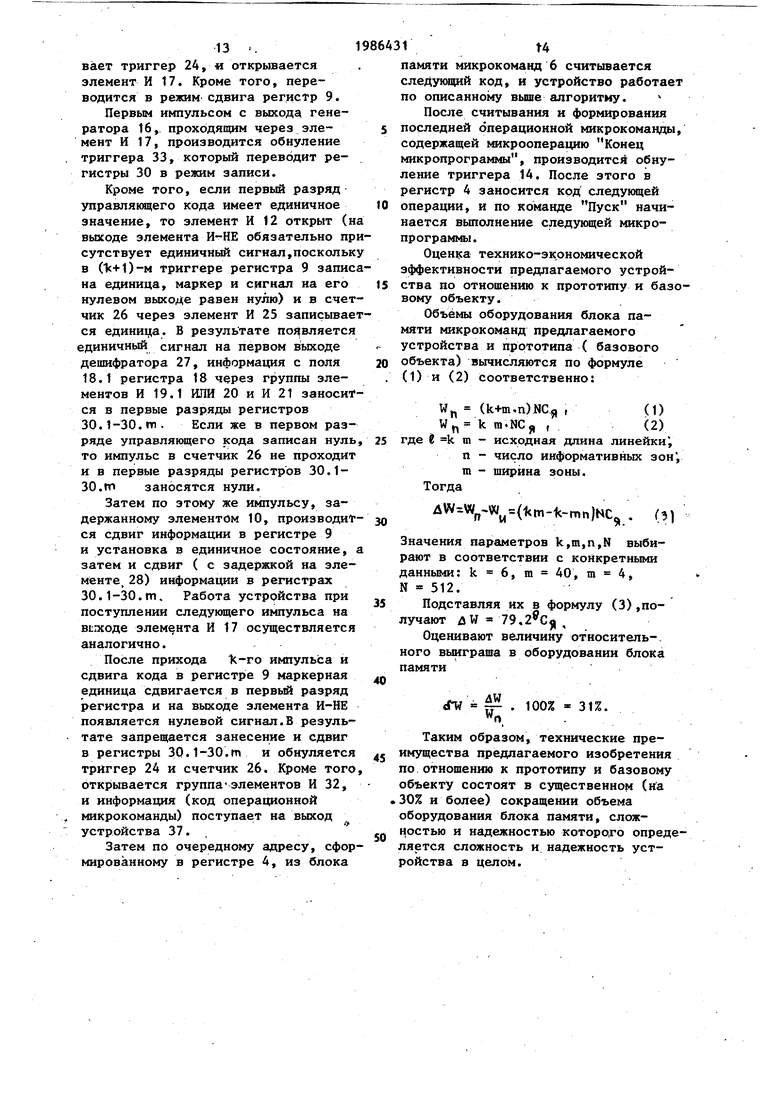

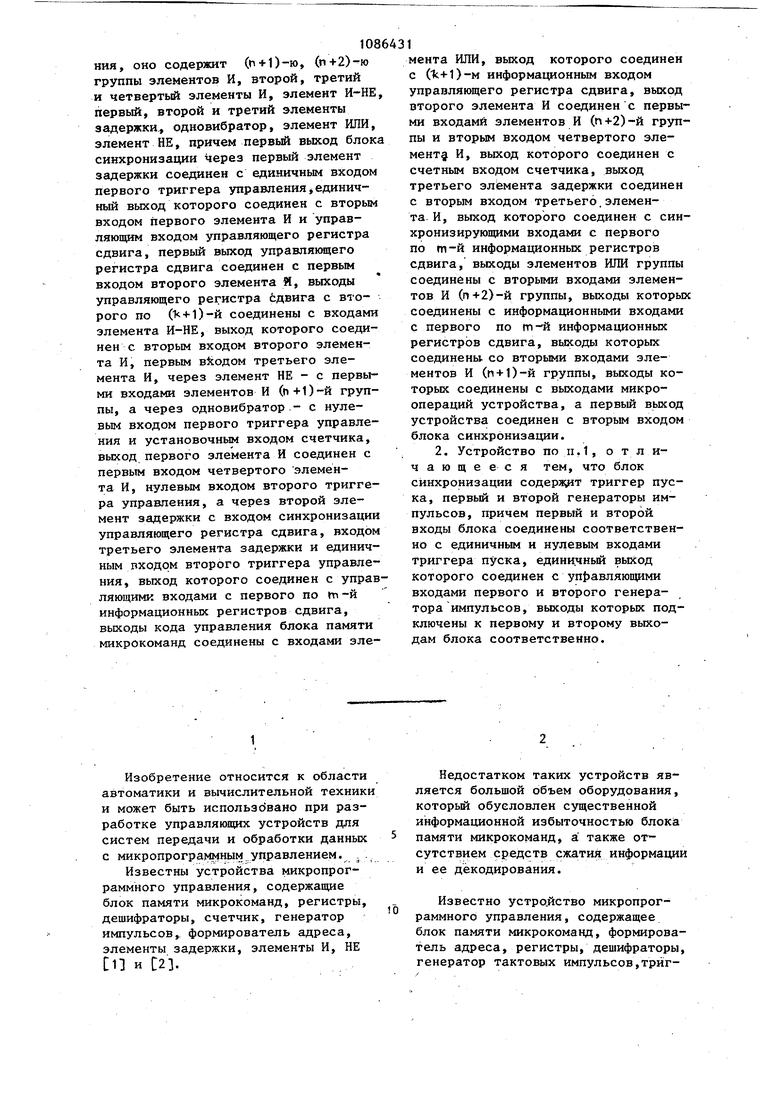

Поставленная цель достиг;ается тем, что устройство микропрограммного управления, содержащее формирователь адреса, регистр адреса, первый и второй дешифраторы,блок памяти микрокоманд, буферный регистр, регистр операционных микрокоманд, управлякщий регистр сдвига, fn информационных регистров сдвига (т- число разрядов в зоне микрокоманд) h групп элементов И (п число информационных полей микрокоманды) , блок синхронизации,первый и второй триггеры управления, счеГчик ГРУППЫ элементов ИЛИ, первый элемент И, причем входы логических условий устройства, первая и вторая группы адресных выходов буферного регистра соединены соответственно с первым - третьим входами формирователя адреса, выходы которого соединены с первой группой Информационных входов регистра адреса, входы кода операции устройства и третья группа адресных выходов буферного регистра соединены соответственно с второй и третьей группами информационных входов регистра адреса, выходы которого соединены с входами первого дешифратор а, первый выхо блока синхронизации и выходы первог дешифратора соединены соответственно с управляющим и адресными входами блока памяти микрокоманд,выходы кода управления которого соединены с первыми k -ми информационны ми входами управляющего регистра сдвига ( число зон в микрокоманде), адресные выходы - с информационными входами буферного регистра а выходы операционных микрокоманд с информационными входами регистра операционных микрокоманд, группы выходов с первой по и-ю регистра операционных микрокоманд соединены первыми входами элементов И соответ ственно с первой по п-ю группы, вы ходы которых соединены с входами эл ментов ИЛИ группы, вход пуска устрой ства подключён к первому входу блока синхронизации, первый выход которого соединен с входами синхронизации регистра адреса, буферного регистра и регистра операционных микро команд, второй выход блока синхронизации соединен с первым входом первого элемента И, выходы счетчика соединены с входами второго дешифратора , выходы с первого по п-и которого соединены с первыми входами элементов И Соответственно с первой по п-ю группы, дополнительно содержит (п + 1)-ю, (п+2)-ю группы элементов И, второй, третий и четвертый элементы И, элемент И-НЕ,первый, второй и третий элементы задержки, одновибратор, элемент ИЛИ, элемент Н причем первый выход блока синхронизации через первый элемент задержки соединен с единичным входом первого триггера управления, единичный выход которого соединен с вторым входом первого элемента И и управляющим входом управляющего регистра сдвига, первый выход управляющего регистра сдвига соединен с первым входом второго элемента И, выходы управляющ го регистра сдвига с второго по (1 + 1)-й соединены с входами элемента И-НЕ, выход которого соединен с вторым входом второго элемента И, первым входом третьего элемента И, через элемент НЕ - с первь1ми входами элементов И (п+1)-й группы, а через одновибратор - с нулевым входом первого триггера управления и ус тановочным входом счетчика, выход первого элемента И соединен с первым входом четвертого элемента И, нулевым входом второго триггера управления, а через второй элемент задержки - с входом синхронизации управляющего регистра сдвига, входом третьего элемента задержки и единичным входом второго триггера управления, выход которого соединен с управляющими входами с первого по m-й информационных регистров сдвига, выходы кода управления блока памяти микрокоманд соединены с входами элемента ШШ, выход которого соединен с (k + O-M информационным входом управляющего регистра сдвига, выхо; второго элемента И соединен с первыми входами элементов И (п+2)-й группы и вторым входом четвертого элемента И, выход которого соединен с счетным входом счетчика, выход третьего элемента задержки соединен с вторым входом третьего элемента И, выход которого соединен с синхрони.чирующими входами с первого т-й инФормационных регистров сдвига, выходы элементов ИЛИ гру11пы соединены с вторыми входами элементов И (п+2)-й группы, выходы которых соединены с информационными входами с первого по m-и информационных регистров сдвига, выходы которых соединены с вторыми входами элементов И (h+1)-H группы, выходы которых соединены с выходами микроопераций устройства, а первый выход устройства соединен с вторым входом блока синхронизации. Кроме того, блок синхронизации содержит триггер пуска, первый и второй генераторы импульсов,причем первьй и второй входы блока соединены соответственно с единичным и нулевым входами триггера пуска,единичный выход которого соединен с управляющими входами первого и второго генератора импульсов, выходы которых подключены к первому и второму выходам блока соответственно. На фиг.1 приведена функциональная схема предлагаемого устройства микророграммного управления;на фиг.2 рагмент временной диаграммы работы стройства. Функциональная схема устройства (фиг.1) содержит формирователь адеса 1, состоящий из группы элеменов И 2, группы 3 элементов суммы о модулю два, регистр адреса 4, ервый дешифратор 5, блок 6 памяти микрокоманд, формат слов, в котором имеете адресное 6.1, управлякнцее 6.2 и операционное 6.3 поля, буферньй регистр 7, включающий поля постоянной 7.1 и переменной 7.2 части адре са, а также поле 7.3 пода логически условий, элемент ШШ 8, управляющий регистр сдвига 9, второй элемент задержки 10, элемент И-НЕ 11,второй элемент И 12, блок синхронизации 13 состоящий из триггера пуска 14,первого 15 и второго 16 генераторов им пульсов, первый элемент И 17, регистр микрокоманд 18, имеющий п ин формационных полей 18.1-l8.h, перву 19.1-п-ю 19.П группы элементов И, группу элементов ИЛИ 20, ()-ю группу элементов И 21, первый элемент задержки 22, одновибратор 23, первый триггер управления 24, четвертый элемент И 25, счетчик 26, второй дешифратор 27, третий элемент задержки 28 и третий элемент И 29, первый 30.1-т-й-30.m информационные регистры сдвига, элемент НЕ 31 (п+1)-ю. группу элементов И 32, второй тригрер управления 33, входы йогических .условий,кода операции и пуска 34-36 соответствен но, выход микроопераций 37. На фиг.2 по оси ординат указаны выходь элементов функциональной схемы, обозначенные в соответствии с фиг.1. Технические средства предлагает мого устройства условно могут быть разделены на три части: средства хранения и выборки кодов микрокоманд средства управления и синхронизации средства формирования кодов операционных микрокоманд. К средствам хранения и выборки кодов микрокоманд относятся формирователь адреса 1, регистр адреса 4 дешифратор 5, блок 6 памяти микрокоманд, буферный регистр 7 и регист микрокоманд 18. Формирователь адреса 1 осуществляет модификацию переменной части адреса в соответствии со значениями логических условий, маскируемыми группой элементов И 2. Собственно модификация адреса производится блоком 3 элементов суммы по модулю два. Регистр адреса 4 предназначен для хранения адреса очередной микрокоманды. Постоянная часть адреса заносится в регистр 4 непосредствен 1 но из ПОЛЯ 7.1 буферного регистра 7, а переменная-С выхода регистра адреса 4. Начальный адрес задается с входа устройства 35. Дешифратор 5 выполняет выбор соответствующего слова (микрокоманды) из блока памяти 6. Буферньй регистр 7 осуществляет запоминание очередного адреса на время, необходимое для формирования след тощего адреса. Регистр 18 предназначен для хранения информативных полей кода операционной микрокоманды. Средства управления и синхронизации состоят из блока синхронизации 13, триггеров управления 24 и 33, элементов И 12, 17, 25 и 29, элемента 11, элементов задержки 10,22 и 28, одновибратора 23, элемента НЕ 31 и групп элементов И 21 и 32. Блок синхронизации 13 служит для формирования двух последовательностей импульсов высокой и низкой частоты (соответственно генераторы 16 и 15). Триггер пуска разрешает работу генераторйв после прихода сигнала Пуск на вход 36. Триггер 24 осуществляет управление подачей синхроимпульсов в режиме формирования кода операционной микрокоманды. Триггер 33 предназначен для задания режима работы (запись, сдвиг) регистров 30.1-30.т. Элементы И 17 и 25 используются для управления подачей синхроимпульсов с выхода генератора 16 в регистр 9, счетчик 26, установкой триггера 33. Элемент И 12 фиксирует единичное значение очередного разряда управляющего кода, а элемент И 29 предназначен для управления подачей и lпyльcoв сдвига в регистры 30.130.т, Группы элементоы И 21 и 32 предназначены для управления записью и считыванием информации из регистр ров 30.1-30.т. В зависимости от , сигналов на выходах элементов И-НЁ 11,элемента НЕ 31 и элемента И 12. Элемент И-НЕ 11 служит для определения нулевого состояния второго (k+D-ro разрядов регистра 9. Одновибратор 23 используется для формирования сигнала обнуления триггера 24, счетчика 26 после окончания декодирования (формирования) кода очередной операционной микрокоманды. Элементы задержки 10,22 и 28 осуществляют задержку синхроимпульсов на время считывания информации из блока 6, формирования очередной части .кода операционной микрокомандам и установки триггера 3 соответственно. К средствам формирования кодов операционных микрокоманд относятся регистры 9, 30.1-30.tn,счетчик 26, дешифратор 27, группы элементов И t9.t-19.n , ИЛИ 20, а также элемент ШШ 8. Регистр 9 служит для записи управляющего кода и его сдвига. Этот регистр имеет V+l разряд,в первы k разрядов заносится собственно уп равлякщий код, а в ()-й - единич ный маркер, формируемый элементом ИЛИ В. После поступления 1 импульсов сдвига маркерный разряд пос- 20 тупает в первый разряд регистра, фиксируя (одновременно с нулевым первым - 1с -м разрядами) момент окончания процедуры формирования кода операционной ьткрокоманды. 25 Счетчик 26 и дешифратор 27 осуществляют управление коммутатором, состоящим из группы элементов И 19.1-19.П и элементов ИЛИ 20.Число импульсов, поступающих в счетчик зо 26 за один цикл формирования кода операционной микрокоманды, полностью определяется числом единиц в управляющем коде. Коммутатор производит последовательную вьщачу содержимого jj полей регистра 18 в регистры 30.1-30.т.

00000

0101 10100 1,1 00 О 11 01 0000

представляется следую1цим образом

01 О 1

1100

1 101

Где А, А

-, А,. - строки массива.

О

При кодировании исходный массив разбивается на зоны По разрядов в каждой. Поскольку каждая из микрокоманд содержит только п 2 информативные зоны, то в формате микрокоманды содержится всего

00000

О 00 00

01101

14 разрядов вместо km 20 разрядов. .Следовательно, благодаря такому кодированию объем массива (блока памяти) снижается на 30%. При декодировании в соответствии с управляющим кодом информаИнформационныё регистры сдвига 36.1-3p.tf предназначены для записи и хранения частей формируемого кода операционной микрокоманды. Сущностьизобретения состоит в повышении экономичности устройства путем уменьшения объема блока памяти на основе горизонтального сжатия кодов операционных микрокоманд. Кодирование операционных микрокоманд в предлагаемом устройстве осуществляется следующим образом. Код операционной микрокоманды состоит .из п +1 полей, из которых одно является управляияцим, an- информационными. Управляющее поле5«|5.. опера k ционной микрокоманды имеет 1 разрядов и кодируется по правилу: 1, если i-я зона исходной операционной микрокоманды является информативной; 0 - в противном случае. Число информационных полей микрокоманды определяется и.з соотношения. hrmojij ti-y, где N - общее число микрокоманд, п - число информативных зон в i-й микрокоманде. Например, массив кодов операционных микрокоманд вида .. тивные зоны занимают часть формируемого кода операционной микрокоманды, соответствующую единичному разряду. Разряды кода микрокоманды, которым соответствует нулевая позиц в управляющем коде, заполняются нул ми. I Ввведенный в устройство микропрограммного управления первый элемент задержки позволяет задержать установку первого триггера управления в единицу на время время считывания информации из блока памяти микрокоманд. Второй элемент задержки позволяет задержать сдвиг информации (управляющего кода) в управляющем регистре сдвига на время, необходимое для очередной записи информации в информационные регистры сдвига. Третий элемент задержки и обусловленных им связей позволяет задер жать сдвиг информации в информацион ных регистрах сдвига на время установки второго триггера управления в единичное состояние. Элементы И-НЕ, второй и третий элементы И, элемент НЕ позволяют фиксировать момент окончания декоди рования микрокоманды и разрешать ее выдачу на выход устройства. Четвертый элемент И позволяет управлять подачей импульсов в счетчик в зависимости от значения очередного разряда управляющего кода. Одновибратор позволяет формировать сигнал обнуления триггеров управления и счетчика после завершения формирования кода операционной микрокоманды. Группа элементов И (п+1)-я позволяет управлять вьщачей операционной микрокоманды на выход после ее формирования; (п+1)-я группа элемен тов И содержит m элементов И, управляющие входы которых соединены с выходом элемента НЕ, а информацио ные - с соответствующим выходом информационных регистров сдвига, су марное число разрядов которых равно Кп - Информационный вход первог элемента И группы соединен с первым выходом первого информационного регистра сдвига, информационный вход второго элемента И группы - с первы 1 вькодом второго информахщонного регистра сдвига, информационный вход V -го элемента И группы - с /U. -м выходом (jUi j V/m , где скобки 3otC означают округление до ближайшего целью, не меньшего, чем el б -го информационного регистра сдвига (б V-m.iftt-«- V/№. Группа элементов И (п+2)-я позволяет управлять подачей информации в информационные регистры сдвига, (п+2)-я группа элементов И, также как и первая - п -я группы элементов И и группа элементов ИЛИ, состоит из m элементов И, причем управляющие входы всех элементов этих групп соединены с выходом второго элемента И, информационный выход i-го элемента И соединен с выходом i-го элемента группы элементов ИЛИ, а выход - с информационным входом i-го информационного регистра сдвига. ° Соединение единичного выхода первого (второго) триггера управления с управляющим V-входом управляющего регистра ( информационньк регистров) сдвига позволяет задавать режим работы всех регистров. Элемент ИЛИ позволяет формировать дополнительный (К+О-й разряд управляющего кода, которьпн вьшолняет функции маркера конца и не позволяет завершить процесс декодирования до момента формирования последних (нулевых) зон в коде операционной микрокоманды. Предлагаемое устройство микропрограммного управления работает следующим образом. В исходном состоянии все элементы памяти устройства обнулены, за исключением триггера 33, которьй находится в единичном состоянии. Единичный сигнал присутствует на нулевом выходе депшфратора 27. В регистр 4 с входа 35 занесен код. операции, определяющий начальный адрес микропрограммы. После прихода сигнала Пуск триггер 14 устанавливается в единичное состояние и по первому имульсу с выхода генератора 15 из блока памяти 6 в регистры 7, 9 и 18 читывается информация (см.фиг.2). Запись в регистр 9 разрешена нулеым сигналом с выхода триггера 24. атем по этому импульсу срабатывает триггер 24,« открывается элемент И 17. Кроме того, переводится в режим сдвига регистр 9. Первым импульсом с выхода генератора 16, проходящим через элемент И 17, производится обнуление триггера 33, который переводит регистры 30 в режим записи. Кроме того, если первый разряд управлякщего кода имеет единичное значение, то элемент И 12 открыт (н выходе элемента И-НЕ обязательно пр сутствует единичный сигнал,поскольк в ()-м триггере регистра 9 запис на , маркер и сигнал на его нулевом выходе равен нулю) и в счет чик 26 через элемент И 25 записывае ся единица. В результате по} вляется единичный сигнал на первом выходе дешифратора 27, информация с поля 18.1 регистра 18 через группы элементов И 19.1 ИЛИ 20 и И 21 заносит ся в первые разряды регистров 30.1-30.т. Если же в первом разряде управляющего кода записан нуль то импульс в счетчик 26 не проходит и в первые разряды регистров 30.130.ro заносятся нули. Затем по этому же импульсу, задержанному элементом 10, производит ся сдвиг информации в регистре 9 и установка в единичное состояние, затем и сдвиг ( с задержкой на элементе, 28) информации в регистрах 30.1-30.т. Работа устройства при поступлении следующего импульса на ВЕЗсоде элемента И 17 осуществляется аналогично. После прихода импульса и сдвига кода в peгиcтpie 9 маркерная единица сдвигается в первый разряд регистра и на выходе элемента И-НЕ появляется нулевой сигнал.В результате запрещается занесение и сдвиг в регистры 30.1-ЗО.т и обнуляется триггер 24 и счетчик 26. Кроме того открывается группа-элементов И 32, и информация (код операционной микрокоманды) поступае т на выход устройства 37.. Затем по очередному адресу, сфор мированному в регистре 4, из блока 1t4 памяти микрокоманд 6 считывается следующий код, и устройство работает по описанному выше алгоритму. После считывания и формирования последней операционной микрокоманды, содержащей микрооперацию Конец микропрограммы, производите обнуление триггера 14. После этого в регистр 4 заносится код следующей опера1щи, и по команде Пуск начинается выполнение следзпощей микропрограммы. Оцен1:са технико-экономической эффективности предлагаемого устройства по отношению к прототипу и базовому объекту. Объёмы оборудования блока памяти микрокоманд предлагаемого устройства и прототипа ( базового объекта) вычисляются по формуле (1) и (2) Соответственно: W (k+m.n)NC,5, , (1) W k m.NC ,(2) где И k m - исходная длина линейкиi n - число информативных зон, та - ширина зоны. Тогда V% W-k-mn)NC Значения параметров k,m,n,M выбирают в соответствии с конкретными данными: k 6, m 40, m 4, N 512. Подставляя их в формулу (3),получают AW « 79. , Оценивают величину относитель-, ного выиграша в оборудовании блока памяти 100% - 31%. Таким образом, технические преимущества предлагаемого изобретения по отношению к прототипу и базовому объекту состоят в существенном (на 30% и более) сокращении объема оборудования блока памяти, сложностью и надежностью которого определяется сложность и надежность устройства в целом.

Л

J50-J

jff ril о-ЧоГ )(l

X5

ГПтИ I

tio

flGRG/ /

гЛ7

L. //

/y/7

/ff

J/

J7

(лс/г/

срие.2

Авторы

Даты

1984-04-15—Публикация

1982-11-24—Подача