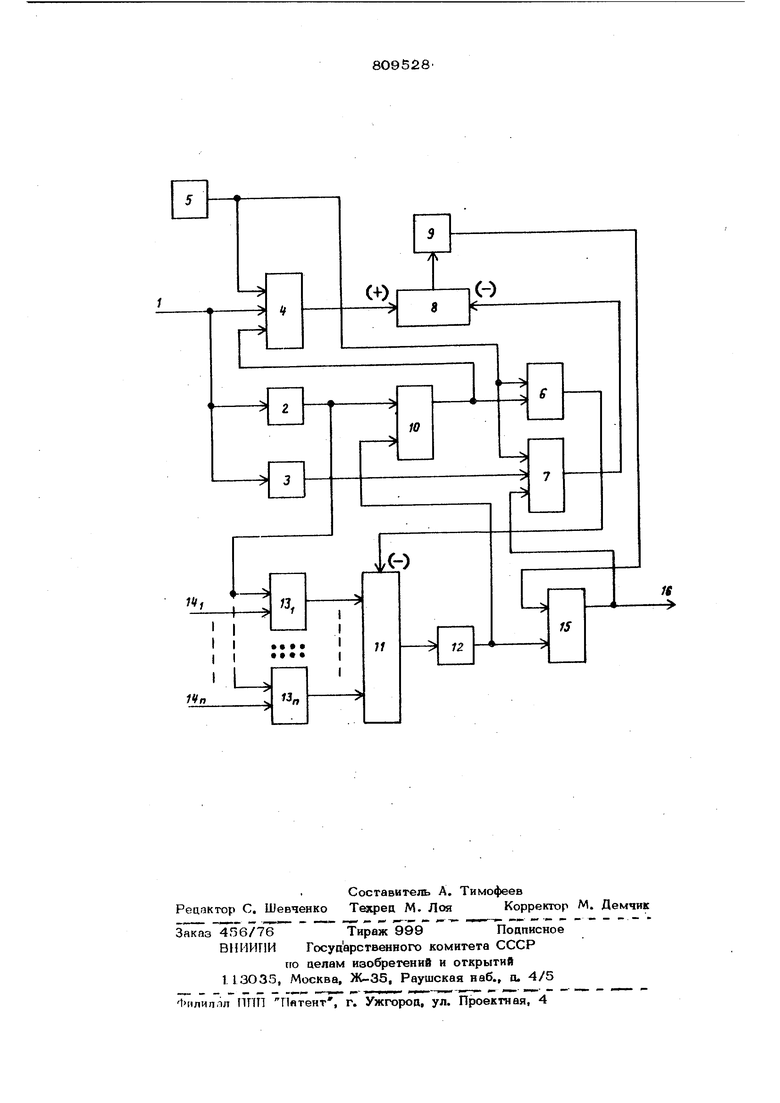

Изобретение относится к измерительной и вычислительной технике и может быть использовано в устройствах автоматики, а в частности, для зацержки прямоугольных импульсов. Известно устройство регулируемой временной задержки прямоугольных им пульсов, содержащее генератор задержки дифференцирующие цепи, элементы ИЛИ, элементы И и элементы НЕ, которое обеспечивает формирование задержанного импульса, а также позволяет плавно менять величину задержки путем подстройки формируемого генератором задержки имйульса }. Недостатками этого устройства являют ся ограниченная величина задержки импульса (расширение пределов задержки достигается путем последовательного вклю чения необходимого количества устройств задержки), а также наличие регулировки для задания задержки, что не позволяет его широко использовать в импульсных устройствах. Кроме тоП), точность задерЖКЦ импульсов зависит от точности регулировки и Квалификации оператора. Известно устройство задержки прямоугольных импульсов, которое содержит генератор опорной частоты, вентили, реверсивный счетчик, элемент НЕ, формирующий триггер, дешифратор нуля, дифференцирующую цепь и элемент задержки 4ронга им пульса 2. . Недостатком этого устройства является то, что оно не позволяет программно изменять длительность формируемой зацержки при непрерывном поступлении импульсов на вход устройства, а также не обеспечивает необходимую точность задержки, так как элемент задержки фронта импульса выполняется по схемам, зависящим от влияния дестабилизирующих факторов на длительность формируемой задержки. Цель изобретения - повышение точности формирования длительности задержки я расширение функциональных возможностей путем обеспечения возможности изменения длительноеги задержки программным путем при непрерывном поступлении импульсов на вход устройства. Указанная цель достигается тем, что в устройство задержки прямоугольных импульсов, содержащее входную шину, подключенную ко входу дифференцирующей цепи, ко входу инвертора и к первому входу первого логического элемента И, второй вход которого подключен к выходу генератора опорной частоты и к первому входу второго логического-элемента И, первый реверсивный счетчик, суммирующий вход KOTopoiX) подключен к выходу первого логического элемента И, вычитаю щий вход - к выходу второго логического элемента И, а выход - ко входу первого дешифратора, и выходной триггер, вход установки в ноль которого подключен к выходу первого дешифратора, а единичный выход - к выходной шине и ко второму входу второго логического элемента И, третий вход которого подключен к выходу инвертора) введены управляющий триггер, второй реверсивный счетчик,, П третьих логических элементов И по числу разрядов второго реверсивного счетчика, второй дешифратор и четвертый логический элемент И , причем первые входы п третьих логических элементов И подключены поразрядно к п шинам задания кода задержки, вторые входы третьих логических элементов И объединены и подключены к выходу дифференцирующей цепи и входу установки в единицу управляющего тригге ра, а выходы третьих логических элементов И поразрядно подключены к установоч ным входам второго реверсивного счетчика, выход которого подключен ко входу второго дешифратора, выход которого под ключен ко входу установки в единицу выходного триггера и ко входу установки в ноль управляющего триггера, единичныйвыход которого подключен к третьему вхо ду первого логического элемента И и к первому входу четвертого логического элемента И, второй вход которого подклю чен к выходу генератора опорной частоты а выход четвертого логического элемента И подключен к вычитающему входу второго реверсивного счетчика. На чертеже представлена функциональная схема устройства. Устройство содержит входную шину 1, подключенную ко входу дифференцирующей цепи 2, ко входу инвертора 3 и к первому входу элемента И 4, генератор 5. опорной частоты,выход которого подключен ко второму входу элемента И 4 и к 80 84 первым входам элементов И 6 и 7, реверивный счетчик 8 длительности импульса, уммирующий вход которого подключен к ыходу элемента И 4, вычитающий вход выходу элемента И 7, а выход - ко ходу дешифратора 9 нуля, управляющий триггер 10, единичный выход которого подключен ко второму входу элемента И 6 и третьему входу элемента И 4, реверсивный счетчик II, длительности задержки выход которого подключен ко входу деши4ратора 12 нуля, вычитающий вход к выходу элемента И 6, а установочные входы поразрядно - к выходам двухвходовых элементов И 13, разрядов реверсивного счетчика 11 длительности задержки ), первые входы которых подключены к шинам 14 задания кода задержки, соответственно, а вторые входы объединены и подключены к выходу дифференцирующей цепи 2 и ко входу установки в единицу управляющего триггера 1О, и выходной триггер 15, вход установки в единицу которого подключен ко входу установки в ноль управляющего триггера 10 и к выходу дешифратора 12 нуля, вход установки в ноль - к выходу цеши(}ратора 9 нуля, а единичный выход - к выходной шине 16 и ко второ-. му входу элемента И 7, третий вход которого подключен к выходу инвертора 3. Устройство работает следующим образом. В исходном состоянии реверсивные счетчики 8 и 11 и триггеры 1О и 15 находятся Б нулевом состоянии. При этом уровень логического нуля с единичного выхода управляющего триггера 10 блокирует прохождение импульсов с генератора 5 опорной частоты через элементы И 4 и 6, а уровень логического нуля с единичного выхода выходного триггера 15 через элементы И 7. Одновременно, прохождение импульсов генератора 5 опорной частоты через элемент И 4 блокируется отсутствием сигнала на входной шине 1. При работе устройртва возможны два случая: случай, когда длительность задержки больше длительности задерживаемого импульса, и случай, когда длительность задержки меньше длительности задерживаемого импульса. В первом случае задерживаемый им пульс со входной шины 1 поступает на элемент И 4, подготавливая его для прохождения импульсов с генератора 5 опорной частоты на суммирующий вход реверсивного счетчика 8 длительности импульса, и через инвертор 3 запрещает прохож58цение импульсов с генератора 5 опорной частоты через элемент И 7 на вычитающий вход реверсивного счетчика 8 дли 4тельноети импульса на время длительности задерживаемого импульса. Одновремен но, задерживаемый импульс со входной шины 1 поступает на дифференцирующую цепь 2, на выходе которой формируется короткий импульс, соответствующий перед нему фронту этого импульса. Импульс с дифференцирующей цепи 2 устанавливает в единичное состояние управляющий триггер 10 и записывает в реверсивный счет чик 11 длительностизадержки через элементы И 13-,- 13рКод, поступающий с шин 14,- 14 задания кода задержки и соответствующий требуемой длительности заде жки. После того, как коде шин 14,- 1 заданиякода задержки записан в реверсивный счетчик 11 длительности задержки, он может быть программно изменен на код соответствующий новой длительности задержки. Уровень логической единицы с выхода управляющего триггера 1О разрешает прохождение на суммирующий вхо реверсивного счетчика 8 длительности им пульса через элемент И 4 импульсов генератора 5 опорной частоты на все врем длительности входного импульса. Таким образом, в реверсивный счетчи 8 длительности импульса записывается код, соответствующий длительности входного импульса. Одновременно, уровень ло гической единицы с выхода управляюще го триггера 10 разрешает прохождение через элемент И 6. импульсов генератора 5 опорной частоты на вычитающий вход реверсивного счетчика 11 длительности задержки. В то время, когда число импульсов, поступающих на вычитающий вход реверсивного счетчика 11 длительности задержки, равно коду, записанному в нем, счетчик обнуляется и импульс с выхода дешифратора 12 нуля устанавливает в нулевое состояние управляющий триггер 10 и в единичное состо5шие выходной триггер 15, формируя передний фронт выходного задержанного импульса. Уровень логического нуля с выхода триггера Ю управления запрещает прохождение импульсов опорного генератора 5 через элементы И 4 и 6 до прихода на входную шину 1 устройства ново го импульса. Уровень логической единицы с вьпсодното триггера 15 разрешает прохождение через элемент И 7 импульсов генератора 5 опорной частоты на вычитающий вход реверсивного счетчика 8 длительности импульса. В то время, ког8да число импульсов, поступивших на вычитающий вход реверсивного счетчика 8 длительности импульса, окажется равным числу и-мпульсов, поступивших ранее на суммирующий вход, счетчик обнулится и импуга)С на выходе дешифратора 9 нуля установит в нулевое состояние выходной триггер 15,закончив формирование выходного импульса. Уровень логического Hyf ля с выхода выходного триггера 15 запрещает дальнейшее прохождение импульсов генератора 5 опорной частоты через элемент И 7 . Таким образом, устройство вновь находится в исходном состоянии. В этом случае, когда длительность задержки меньше длительности вxoдI oгo импульса, устройство работает следующим образом. После прихода входного импульса в реверсивный счетчик 11 длительности задержки записываетсякодзадержки, и уровень логической единицы с выхода управляющего триггера 1О разрешает прохождение импульсов генератора 5 опорной частоты на суммирующий вход реверсивного счетчика 8 длительности импульса и на вычитающий вход реверсивного счетчика 11 длительности задержки через элементы И 4 и 6 соответственно. Обнуление реверсивного счетчика 11 длительности за- держки произойдет раньше, чем закончится действие входного импульса, что, в свою очередь, вызовет обнуление управляющегог триггера 10 и запрещение прохождения импульсов генератора 5 опорной частоты на суммирующий вход реверсивного счетчика 8 длительности импульса и на вычитающий вход реверсивного счетчика 11 длительности задержки. Таким образом, в реверсивном счетчике 8 длительности импульса записан код, соответствующий длительности задержки, а не длительности импульса, как в первом случае. Одновременно, входной импульс через инвертор 3 блокирует прохождение импульсов генератора 5 опорной частоты через элемент И 7 на вычитающий вход реверсивного счетчика 8 длительности импульса на все время длительности входного импульса. После окончания действия входного импульса импульсы генератора 5 опорной частоты начинают поступать на вычитающий вход реверсивного счетчика 8 длительности импульса. В остальном устройство работает аналогично первому случаю. Предлагаемое устройство задержки прямоугольных импульсов позволяет, в от личие от известных, повьгсить точность формируемой задержки, которая определяется только шагом квантования (.периодом импульсов генератора 5 опорной час тоты), а также программно изменять в широких пределах длительности формируемой задержки в темпе поступления задерживаемых импульсов на вход устрой ства. Пределы изменения длительности формируемой задержки в предлагаемом устройстве колеблятся от О до ( 1) Т, где Т - период импульсов генератора 5 опорной частоты, а п - число разрядов реверсивного счетчика 11 .длительности задержки. Поэтому предлагаемое устройство можно более широко использовать в импульсных устройствах измерительной и выислительной техники, а- также в устро ствах автоматики. Формула изобрегени Устройство задержки прямоугольных импульсов, содержащее входную шину, подключенную входу дифференцирующей цепи, ко входу инвертора и к первому вхоцу первого логического элемента И, второй вход которого подключен к выход генератора опорной частоты и к первому входу второго логического элемента И, первый реверсивный счетчик, суммирующий вход которого подключен к выходу первого логического элемента И, вычита щий вход - к выходу второго логическог элемента И, а выход - ковходу первого дешифратора, и выходной триггер, вход установки в ноль которого подключен к выходу первого дешифратора, а единичны выход - к выходной шине и ко второму входу второго логического элемента И, третий вход которого подключен j. выходу инвертора, отличающееся тем, что, -с целью повышения- точности формирования длительности задержки и расширения функциональных возможностей, в него введены управляющий триггер, второй реверсивный счетчик, п третьих логических элементов И по числу разрядов второго реверсивного счетчика, второй дешифратор и четвертый логический элемент И, причем первые входы П третьих логических элементов И подключены поразрядно к - шинам задания кода задержки, вторые входы третьих логических элементов И объединены и подключены к выходу дифференцирующей цепи и входу установки в единицу управляющего триггера, а выходы третьих логических элементов И поразрядно пош лючены к установочным входам второго реверсивного счетчика, выход которого подключен ко входу второго дешифратора, выход которого подключен ко входу установки в единицу выходного триггера и ко входу установки в ноль управляющего триггера, единичный выход которого подключен к третьему входу первого логического элемента И и к первому входу четвертого логического элемента И, второй вход которого подключен к вь1ходу генератора опорной частоты, а выход четвертого логического элемента И подключен к вычитающему входу второго реверсивного счетчика. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 534856, кл. НОЗК 5/13, О5Л 1.76. 2,Авторское свидетельство СССР N 45379О, кл. НОЗК 5/13, 15.12.74.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство задержки импульсов | 1981 |

|

SU974564A2 |

| Селектор импульсов по длительности | 1979 |

|

SU817998A1 |

| Устройство для управленияТиРиСТОРНыМ АВТОНОМНыМ иНВЕРТОРОМ | 1977 |

|

SU794704A1 |

| Устройство для задержки импульсов | 1980 |

|

SU907787A1 |

| Устройство для управляемой задержки импульсов | 1980 |

|

SU902236A1 |

| Устройство задержки импульсов | 1981 |

|

SU987808A1 |

| Формирователь импульсов | 1980 |

|

SU884110A1 |

| Устройство задержки прямоугольных импульсов | 1983 |

|

SU1100721A1 |

| АДАПТИВНЫЙ ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 2000 |

|

RU2166773C1 |

| Устройство для измерения нелинейности пилообразного напряжения | 1990 |

|

SU1777101A1 |

Авторы

Даты

1981-02-28—Публикация

1979-03-20—Подача