1

Изобрегение огносигся к импульсной технике и может быть использовано в устройствах преобразования и обработки информации

По основному авт, св. №54412О известно устройство цля синхронизации импульсов, используемое в импульсной технике для преобразования и обработки информации, которое содержит триггер, логический элемент ИЛИ, элемент совпадений, два логических элемента И-НЕ и логический элемент НЕ, выход которого соединен с первым входом элемента совпадений, а вход-соединен с выходом первого логического элемента И-НЕ, выход каждого из которых соединен с одним из входов другого, второй вход первого логического элемента И-НЕ соединен с выходом логического элемента ИЛИ, а второй вход второго элемента И-НЕ соединен со вторым входом элемента совпадений, при атом выход триггера соединен с одним из входов логического элемента ИЛИ, с другим входом которого соединен выход

элемента совпадений и один из входов три ггер а |V.

Недостатком этого устройства является невысокая надежность, так как при совпадении синхронизируемого сигнала с тактовым импульсом на выходе устройства будет появляться только часть синхронизированного импульса, что может привести к сбоям в системе.

Цель изобретения - повышение надежности устройства.

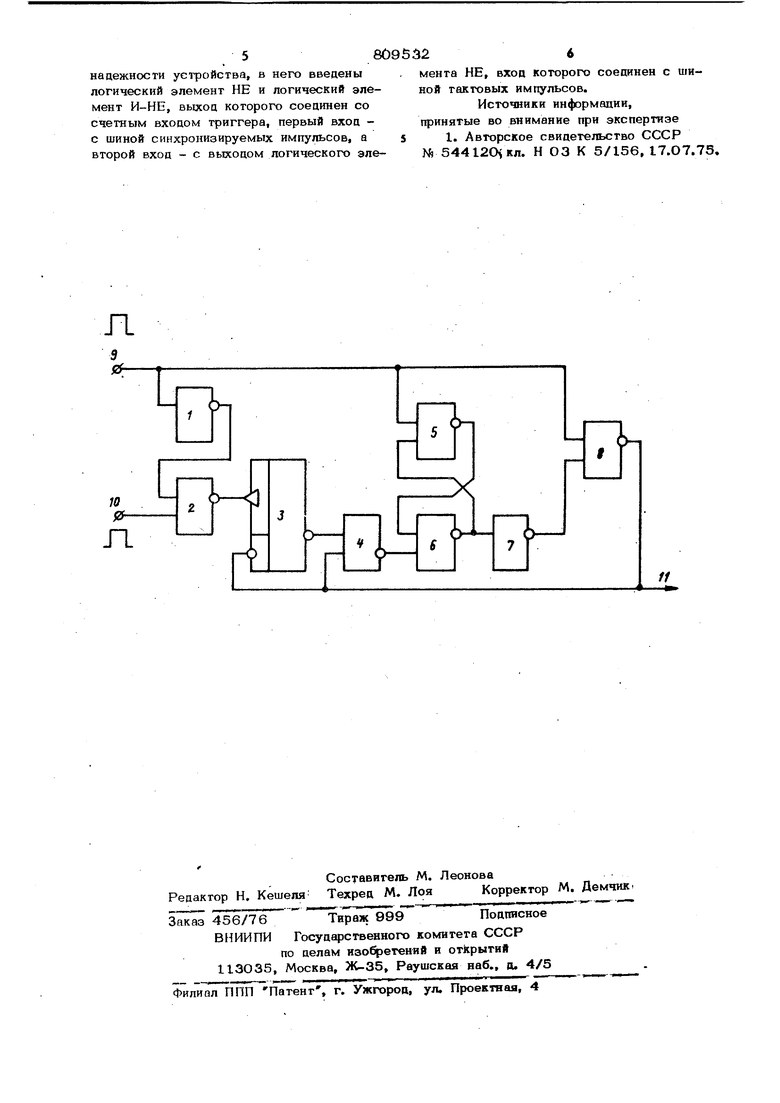

Поставленная цель достигается тем, что в устройстве для синхронизации импульсов, содержащее триггер, логический элемент ИЛИ, элемент совпадений, два логических элемента И-НЕ, выход каждого из которых соединен с одним из входов другого, второй вход первого логического элемента И-НЕ соединен с выходом логического элемента ИЛИ, а второй вход второго элемента И-НЕ соединен с одним из входов элемента совпадений, при этом рлход триггера соединен с одним из входов логического элемента ИЛИ, с другим BxonoM которого соещшен выхоц элемента совпадений и один из входов триггера, вход логического элемента НЕ соединен с выходом первого логического элемента И-НЕ, а выход - с другим входом элемен та совпадений, введены логический эле мент НЕ и логический элемент И-НЕ, вы,ход которого соединен со счетным входом триггера, первый вход - с шиной синхрониэируемых импульсов, а второй вход с выходом логического элемента НЕ, вход которого соединен с шиной тактовых импульсов. На чертеже представлена функциональная схема устройства для синхронизации импульсов. Устройство содержит логический элемент НЕ I, логический элемент И-НБ 2, триггер 3, логический элемент ИЛИ 4, логические элементы И-НЕ 5 и б, логи-ческий элемент НЕ 7, элемент 8 совпадения, шину 9 тактовых импульсов, шину 1О синхронизируемого импульса, шину 11 выходного сигнала. Шина 9 соединена с логическим элементом НЕ 1, первым входом логического элемента И-НЕ 5 и первым входом элемента 8 совпадений. Шина Ю соединена с первым входом логического элемента И-НЕ 2, а шина 11 - с выходом элемента 8 совпадений первым входом логического элемента ИЛИ 4 и установочным входом триггера 3. Выход логического элемента НЕ 1 соединен со вторым входом логического элемента И-НЕ 2, выход которого соединен со счетным входом триггера 3. Инверсный выход триггера 3 соединен со вторым входом логического элемента ИЛИ 4, выход которого соединен с первым входом логического элемен та И-НЕ 6. Второй вход логического эле мента И-НЕ 6 соединен с выходом логического элемента И-НЕ 5, а выход - со вторым входом логического элемента И-НЕ. 5 и входом логического элемента НЕ 7, выход которого соединен со вторы входом элемента 8 совпадений. Устройство для синхронизации импульсов работает следуквдим образом. В исходном положении триггер 3 находится в нулевом состоянии и с его инверсного выхода единичный потенциал поступает на один из входов логического элемента ИЛИ 4. При отсутствии тактово го импульса на шине 9 через логический элемент НЕ 1 подается разрешение на один из входов логического элемента И-НЕ 2 для прохождения сигнала с шины 10, Одновременно с выхода логического 8 24 лемента И-НЕ 5 и выхода элемента 8 овпадений снимается едини шый потениал, поступающий .на другой вход лпгичесого элемента ИЛИ 4 и на установочный вход триггера 3. С выхода логического лемента ИЛИ 4 снимается нулевой потениал, который прикладывается к первому входу логического элемента И-НЕ 6. Та-. КИМ образом в исходном состоянии с выходов логических элементов И-НЕ 5 и б снимаются единичные потенциалы, а с выхода логического элемента НЕ 7 - нулевой . Поступаюш.ий на шину 10 синхронизируемый импульс проходит через логический элемент И-НЕ 2 и по перепаду потенциалов переднего фронта опрокидывает триггер 3. На инверсном выходе триггера 3 появляется нулевой потенциал, на выходе логического элемента - нулевой потенциал, а на выходе логического элемента ИЛИ 4 - единичный . Логический элемент И-НЕ 6 открывается и на его выходе появляется нулевой потенциал, а на выходе логического элемента НЕ 7- единичный потенциал Поступающий затем на шину 9 тактовый импульс не изменяет потенциалы на выходах логических элементов И-НЕ 5 и б, а прохоця через открытый элемент 8 совпадений, инвертируется и поступает на выход 11 устройства в качестве синхронизированного импульса. Синхронизированный импульс, поступая на вход триггера 3, перебрасывает его в исходное состояние а поступая на вход логического элемента ИЛИ 4, поддерживает едини тый потенциал на его выходе. По окончании тактового импульса устройство возвращается в исходное состояние. При совпадении синхронизируемого импульса с тактовым импульсом логический элемент И-НЕ 2 закрыт через логический элемент НЕ 1. Работа устройства начинается после окончания следования тактового импульса. Предлагаемое устройство выгодно отличается от известного тем, что на его выходе будут появляться синхронизированные импульсы строго определенной длительности, равной длительности одного тактового-импульса, свою очередь повышает надежность устройства. ормула. изобретен и я Устройство для синхронизации импушэсов по авт. св. N 54412О, отличаю ш. е е с я тем, что, с целью повышения

нааежности ус7ройства, в него введены логический элемент НЕ и логический элемент И-НЕ, выход которого соединен со счетным входом триггера, первый вход с шиной синхронизируемых импульсов, а второй вход - с вьгходом логического элемента НЕ, вхоц которого соединен с шиной тактовых импульсов.

Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 54412О кл. Н 03 К 5/156,17.07.75.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синхронизации импульсов | 1975 |

|

SU544120A1 |

| Устройство для управления доступом к памяти | 1985 |

|

SU1282147A1 |

| Устройство для синхронизации импульсов | 1981 |

|

SU961125A1 |

| Селектор импульсов по длительности | 1980 |

|

SU869009A1 |

| Устройство для синхронизации импульсных сигналов | 1976 |

|

SU690620A1 |

| Синхронизирующее устройство | 1979 |

|

SU792574A1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ ИМПУЛЬСОВ | 2002 |

|

RU2238610C2 |

| Устройство тактовой синхронизации и выделения пачки импульсов | 1990 |

|

SU1723658A2 |

| Устройство для синхронизации импульсов | 1977 |

|

SU658725A1 |

| Устройство синхронизации | 1985 |

|

SU1285577A1 |

Авторы

Даты

1981-02-28—Публикация

1979-03-07—Подача