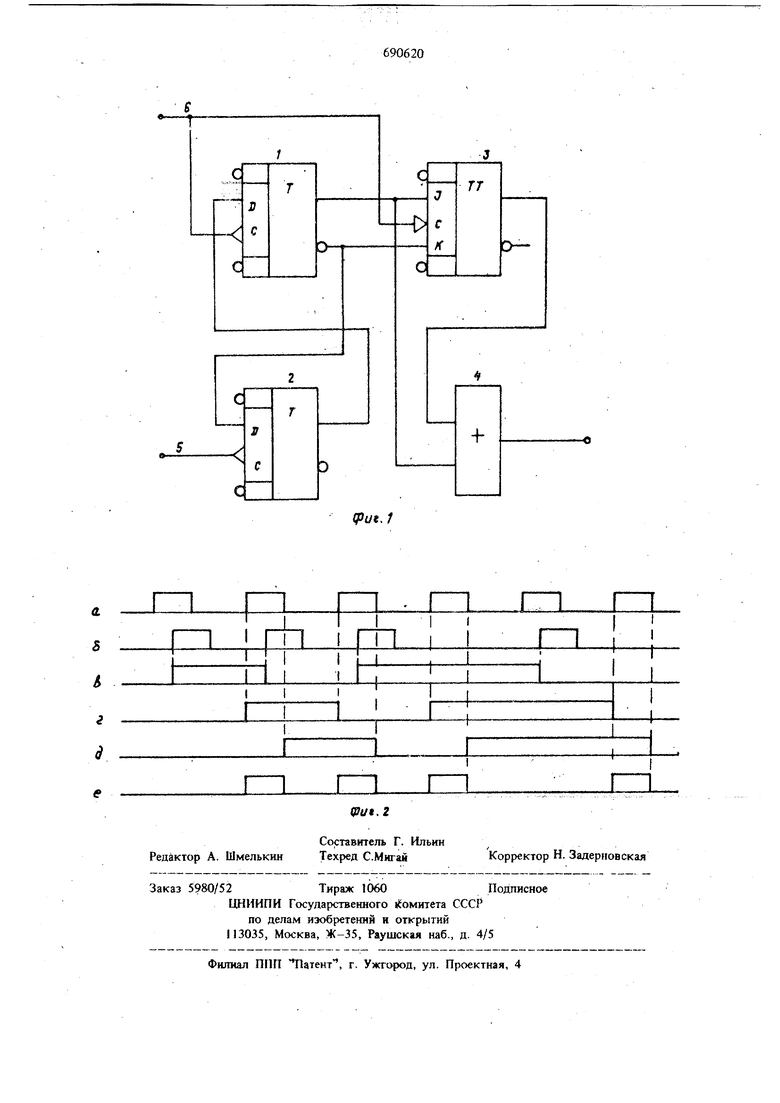

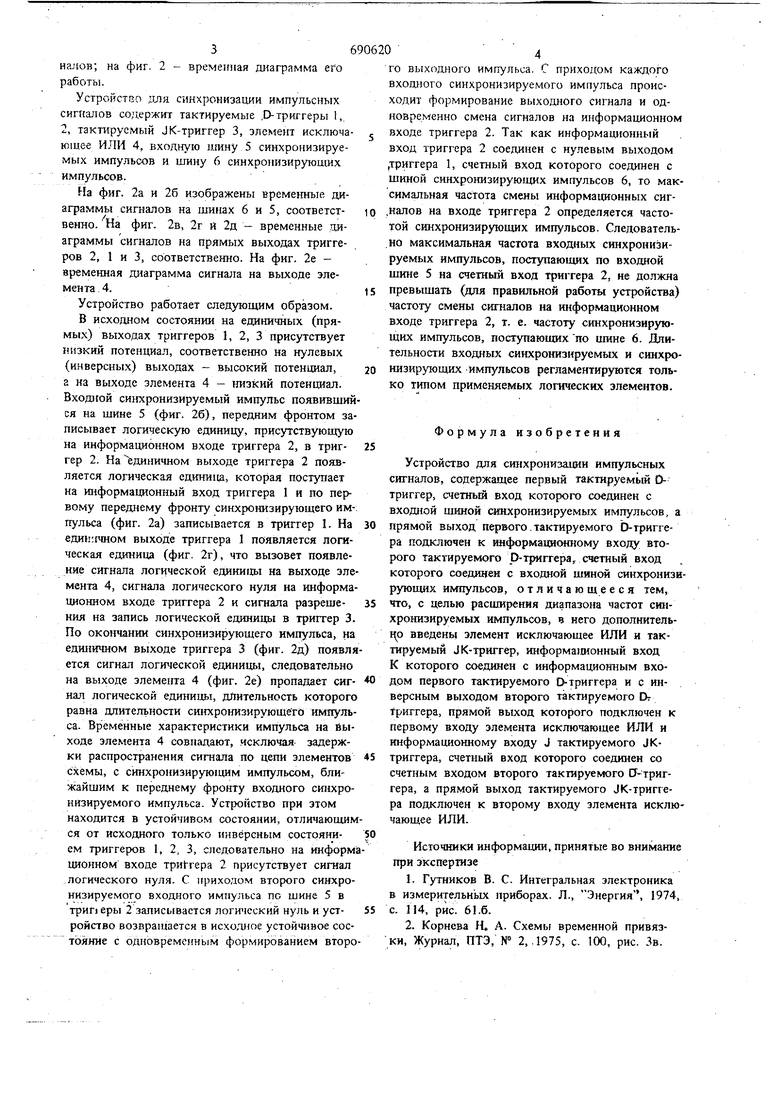

на фиг. 2 - временная диаграмма его работы.

Устройство зля синхронизации импульсных сигналов со,чержит тактируемые ,0-триггеры I,. 2, тактируемый JK-триггер 3, элемент исключающее ИЛИ 4, входную шину 5 синхро шзируемых импульсов и шину 6 синхронизирующих импульсов.

На фиг. 2а и 26 изображены временные диaqjBMMbi сигналов на шинах 6 и 5, соответствеяно. На фиг. 2в, 2г и 2д - временные диаграммы сигналов на прямых выходах триггеров 2, 1 и 3, соответственно. На фиг. 2е - временная диаграмма сигнала на выходе элемента 4. Устройство работает следующим образом. В исходном состоянии на единичных (прямых) выходах триггеров 1, 2, 3 присутствует низкий потенциал, соответственно на нулевых (инверсных) выходах - высокий потенциал, а на выходе элемента 4 - низкий потенциал. Входной синхронизируемый импульс появивщийся на шине 5 (фиг. 26), передним фронтом записывает логическую единицу, присутствующую на информационном входе триггера 2, в триггер 2. На единичном выходе триггера 2 появляется логическая едини1И, которая поступает на информационный вход триггера 1 и по первому переднему фронту синхронизирующего им-. пульса (фиг. 2а) записывается в триггер 1. На единичном выходе триггера 1 появляется логическая единица (фиг. 2г), что вызовет появление сигнала логической единицы на выходе элемента 4, сигнала логического нуля на информационном входе триггера 2 и сигнала разрешения на запись логической единицы в триггер 3. По окончании синхронизирующего импульса, на единичном выходе триггера 3 (фиг. 2д) появляется сигнал логической ещлнтщ, следовательно на выходе элемента 4 (фиг. 2е) пропадает сигнал логической единицы, длительность которого равна длительности сшгхронизируюшего импульса. Временные характеристики импульса на выходе элемента 4 совпадают, исключая- задержки распространения сигнала по цепи элементов схемы, с синхронизирующим импульсом, ближайшим к переднему фронту входного синхронизируемого импульса. Устройство при зтом находится в устойчиво.м состоянии, отличающимся от исходного только инверсным состоянием триггеров 1, 2, 3, следовательно на информционном входе TpHtrepa 2 присутствует сигнал логического нуля. С 1грихояом второго синхронизируемого входного импульса по шине 5 в трип еры 2 записывается логический нуль и устройство возвращается в исходное устойчивое состояние с одновременным формированием второго выходного импульса. С приходом каждого входного синхронизируемого импульса происходит формирование выходного сигнала и одновременно смена сигналов на информационном входе триггера 2. Так как информашюнный вход триггера 2 соединен с нулевым выходом .триггера 1, счетный вход которого соединен с шиной синхронизирую1цих импульсов 6, то максимальная частота смены информационных сиг,налов на входе триггера 2 определяется частотой синхронизирующих импульсов. Следовательно максимальная частота входных синхрони:зируемых импульсов, поступающих по входной шине 5 на счетный вход триггера 2, не должна превышать (для правильной работы устройства) частоту смены сигналов на информационном входе триггера 2, т. е. частоту синхронизирующих импульсов, поступаюодах по цшне 6. Длительности входных синхронизируемых и синхронизирующих импульсов регламентируются только типом применяемых логических элементов.

Формула изобретения

Устройство для синхронизации импульсных сигналов, содержащее первый тактируемый Dтриггер, счетный вход которого соединен с входной шиной синхронизируемых импульсов, а прямой выход первого, тактируемого D-триггера подключен к информационному входу второго тактируемого О-т|жггера, счетный вход которого соединен с входной шиной синхронизирующих импульсов, отличающееся тем, что, с целью расширения диапазона частот синхронизируемых импульсов, в него дополнительцр введены элемент исключающее ИЛИ и тактируемый JK-триггер, информа1шонный вход К которого соединен с информационным входрм первого тактируемого О-триггера н с инверсным выходом второго тактируемого От триггера, прямой выход которого подключен к первому входу элемента исключающее И.ПИ и информационному входу J тактируемого JKтриггера, счетный вход которого соединен со счетным входом второго тактируемого CJ- триггера, а прямой выход тактируемого J К-триггера подключен к второму входу элемента исключающее ИЛИ.

Источники информации, принятые во внимани при экспертизе

1.Гутников В. С. Интегральная электроника в измерительнь1х приборах. Л., Энергия , 1974 с. 114, рис. 61.6.

2.Корнева fi, А. Схемы временной привязки. Журнал, ПТЭ, Г 2, .1975, с. 100, рис. Зв.

a. S & г

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ИЗМЕРЕНИЯ СКОРОСТИ ВРАЩЕНИЯ ВАЛА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2017156C1 |

| Устройство тактовой синхронизации и выделения пачки импульсов | 1990 |

|

SU1723658A2 |

| ПРЕОБРАЗОВАТЕЛЬ БИНАРНОГО КОДА В ФАЗОМАНИПУЛИРОВАННЫЙ КОД | 1999 |

|

RU2159988C1 |

| Устройство для синхронизации импульсов | 1982 |

|

SU1192126A1 |

| ЖДУЩИЙ ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ | 1993 |

|

RU2047939C1 |

| Формирователь одиночного импульса | 1982 |

|

SU1157666A1 |

| Фазовый дискриминатор | 1986 |

|

SU1334355A1 |

| Генератор прямоугольных импульсов | 2021 |

|

RU2759439C1 |

| Синхронизирующее устройство | 1984 |

|

SU1213528A1 |

| МНОГОКАНАЛЬНЫЙ ЦИФРОВОЙ ФИЛЬТР | 1991 |

|

RU2029361C1 |

Авторы

Даты

1979-10-05—Публикация

1976-09-07—Подача