Изобретение относится к цифровой вычислительной технике, в частности к устройствам для сопряжения с памятью, и может быть использовано для построения систем с быстрой памятью.

Цель изобретения - расширение функциональных возможностей устройства путем организации приоритета по циклу записи информации.

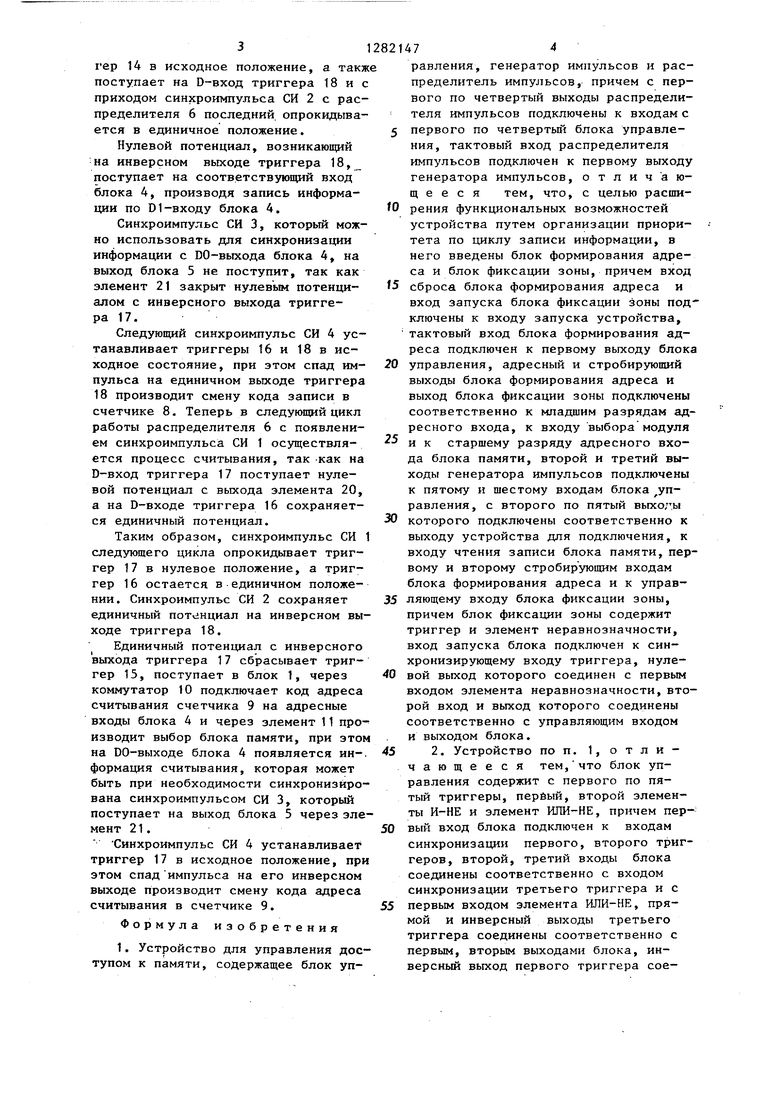

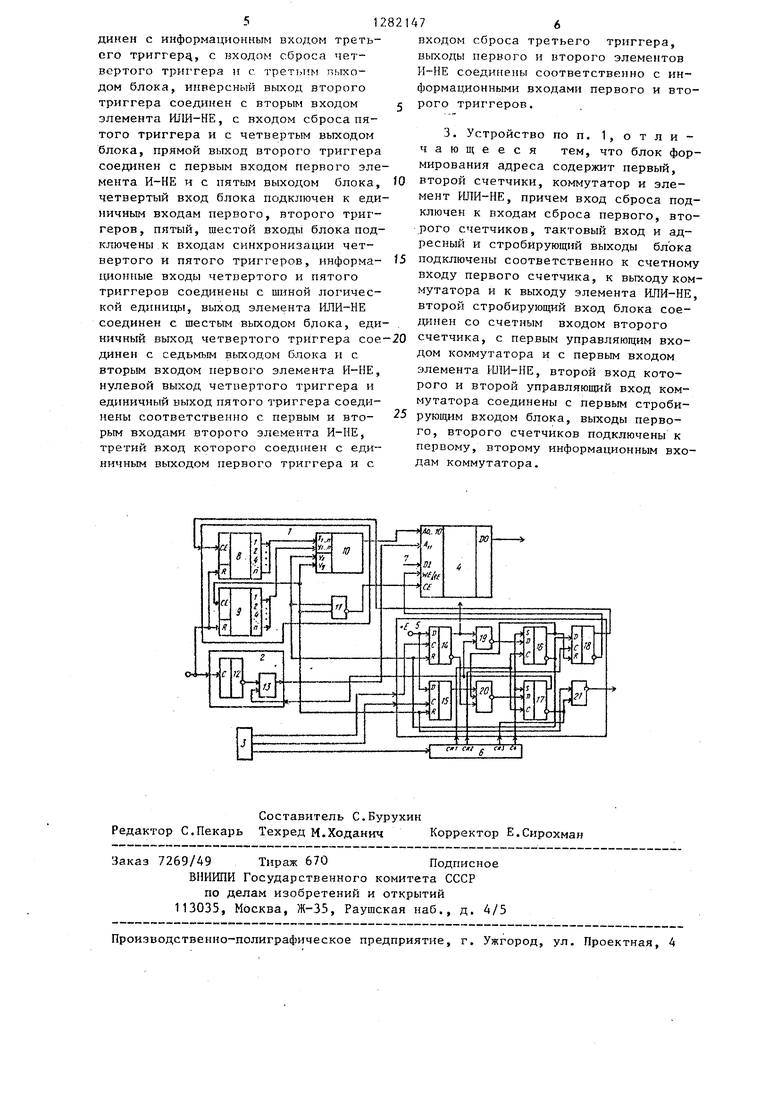

На чертеже представлена схема устройства.

Устройство содержит блок 1 формирования адреса, блок 2 фиксации зоны, генератор 3 импульсов, блок 4 памяти, блок 5 управления, распределитель 6 импульсов, информационный вход 7 устройства.

Блок 1 формирования адреса содер- 7КИТ первьш счетчик 8, второй счетчик 9, коммутатор 10, элемент ИЛИ-НЕ 11.

Блок 2 фиксации зоны содержит триггер 12 и элемент 13 неравнозначности.

Блок 5 управления содержит четвертый 14, пятьш 15, первый 16, второй 17, третий 18 триггеры, первый 19-. и второй 20 элементы И-НЕ, элемент ШТИ-НЕ 21,

Устройство работает следующим образом.

Блок 5 вырабатывает последовательность управляюар х сигналов, реализующую заданный алгоритм (запись- считывание) работы с памятью. Синхронизация блока 5 осуществляется распределителем 6 и генератором 3. Распределитель-6 представляет собой сдвиговый триггерньй регистр, про- движе;;ие которого осуществляется серией импульсов с выхода генератора 3. Однократная развертка распределителя 6 составляет цикл синхронизации, который может включать различное количество тактовых сигналов, например четыре: СИ 1,...,СИ 4.

Информация, подлежащая записи в блок 4, привязывается к сигналу запуска на входе устройства и при необходимости может быть синхронизирована сигналом с выхода триггера 14 5. Сигнал запуска используется также для установки счетчиков 8 и 9.

Информация, снимаемая с блока 4 в цикле считывания, может быть синхронизирована сигналом с выхода элемента ИЛИ-НЕ 21 блока 5.

Синхронизация входной и выходной информации может быть реализована с помощью и-трйггеров.

Распределитель 6 устанавливается

в исходное состояние при подаче напряжения питания.

Исходному состоянию распределителя 6 соответствует единичный потенциал сигнала СИ 4, который устанавливает триггеры 16 и 17 в единичное состояние, которому соответствует положительный потенциал на их единичных выходах. Положительный потенциал с выхода триггера 16 открывает по

одному из входов элемент И-НЕ 20 и устанавливает триггер 18 в нулевое состояние, которому соответствует по- тенциал на его инверсном выходе, этот пoтeнIJ иaл является запрещающим для

цикла записи в блоке 4. Единичньй потенциал с прямого выхода триггера 17 поступает на вход элемента 13, уровень сигнала с выхода которого определяет зону записи или считывания.

Сигнал запуска, появляясь на входе узла 2, опрокидывает триггер 12, производя этим смену зоны записи на зону считывания.

С выходов генератора 3 на С-входы триггеров 14 и 15 соответственно поступают импульсы частоты записи и считывания.

Приоритетом обращения к блоку 4

обладают импульсы частоты записи. Таким образом, если импульсы частоты записи и считывания приходят одновременно, то оба триггера 14 и 15 опрокидываются в единичное положение, при этом на выходе элемента 20 сохраняется единичный потенциал, а на выходе элемента 19 появляется нулевой потенциал, который поступает на D-вход триггера 16. Таким образом, при появлении синхроимпульса СИ 1 на С-входе триггеров 16 и 17 триггер 16 опрокидьшается в нулевое положение, а триггер 17 остается в единичном положении.

Единичный потенциал с инверсного выхода триггера 16 поступает в блок 1 и через элемент 11 поступает на вход блока 4, а также через коммутатор 10 подключает код адреса записи счетчика 8 к адресным входам блока 4.

Единичный потенциал с инверсного выхода триггера 16 сбрасывает тригrep 14 в исходное положение, а такж поступает на D-вход триггера 18 и с приходом синхроимпульса СИ 2 с распределителя 6 последний опрокидывается в единичное положение.

Нулевой потенциал, возникающий на инверсном выходе триггера 18, поступает на соответствующий вход блока 4, производя запись информации по D1-входу блока 4,

Синхроимпульс СИ 3, который можно использовать для синхронизации информации с DO-выхода блока 4, на выход блока 5 не поступит, так как элемент 21 закрыт нулевым потенци- алом с инверсного выхода триггера 17.

Следующий синхроимпульс СИ 4 устанавливает триггеры 16 и 18 в исходное состояние, при этом спад им- пульса на единичном выходе триггера 18 производит смену кода записи в счетчике 8. Теперь в следующий цикл работы распределителя 6 с появлением синхроимпульса СИ 1 осуществля- ется процесс считывания, так -как на D-вход триггера 17 поступает нулевой потенциал с выхода элемента 20, а на D-входе триггера 16 сохраняется единичный потенциал.

Таким образом, синхроимпульс СИ следующего цикла опрокидывает триггер 17 в нулевое положение, а триггер 16 остается в-единичном положении. Синхроимпульс СИ 2 сохраняет единичный пoт iнциaл на инверсном выходе триггера 18.

Единичный потенциал с инверсного выхода триггера 17 сбрасывает триггер 15, поступает в блок 1, через коммутатор 10 подключает код адреса считывания счетчика 9 на адресные входы блока 4 и через элемент 11 производит выбор блока памяти, при этом на DO-выходе блока 4 появляется информация считывания, которая может быть при необходимости синхронизирована синхроимпульсом СИ 3, который поступает на выход блока 5 через элемент 21.

Синхроимпульс СИ 4 устанавливает триггер 17 в исходное положение, при этом спад импульса на его инверсном выходе производит смену кода адреса считывания в счетчике 9.

Формула изобретения

1. Устройство для управления доступом к памяти, содержащее блок управления, генератор импульсов и распределитель импульсов, причем с первого по четвертый выходы распределителя импульсов подключены к входам с первого по четвертьш блока управления, тактовый вход распределителя импульсов подключен к первому выходу генератора импульсов, отличающееся тем, что, с целью расширения функциональных возможностей устройства путем организации приоритета по циклу записи информации, в него введены блок формирования адреса и блок фиксации зоны, причем вход сброса блока формирования адреса и вход запуска блока фиксации зоны подключены к входу запуска устройства, тактовьш вход блока формирования адреса подключен к первому выходу блок управления, адресный и стробируюший выходы блока формирования адреса и выход блока фиксации зоны подключены соответственно к младшим разрядам адресного входа, к входу выбора модуля и к старшему разряду адресного входа блока памяти, второй и третий выходы генератора импульсов подключены к пятому и шестому входам блока управления, с второго по пятый выхо/ ы которого подключены соответственно к выходу устройства для подключения, к входу чтения записи блока памяти, первому и второму стробир ующим входам блока формирования адреса и к управляющему входу блока фиксации зоны, причем блок фиксации зоны содержит триггер и элемент неравнозначности, вход запуска блока подключен к синхронизирующему входу триггера, нулевой выход которого соединен с первым входом элемента неравнозначности, второй вход и выход которого соединены соответственно с управляющим входом и выходом блока.

2. Устройство по п. 1, отличающееся тем, что блок управления содержит с первого по пятый триггеры, пербый, второй элементы И-НЕ и элемент ШТИ-НЕ, причем первый вход блока подключен к входам синхронизации первого, второго триггеров, второй, третий входы блока соединены соответственно с входом синхронизации третьего триггера и с первым входом элемента ИЛИ-НЕ, прямой и инверсный выходы третьего триггера соединены соответственно с первым, вторым выходами блока, инверсный выход первого триггера соединен с информационным входом третьего триггеру, с входом сброса четвертого триггера и с треты м выходом блока, инрерсный выход второго триггера соединен с вторым входом элемента ИЛИ-НЕ, с входом сброса пятого триггера и с четвертьм выходом блока, прямой выход второго триггера соединен с первым входом первого элемента И-НЕ и с пятым выходом блока, четвертый вход блока подключен к единичным входам первого, второго триггеров, пятый, шестой входы блока подключены к входам синхронизации четвертого и пятого триггеров, информа- 1ШО1П1ые входы четвертого и пятого триггеров соединены с шиной логической единицы, выход элемента ИЛИ-НЕ соединен с шестым выходом блока, еди ничный выход четвертого триггера сое динен с седьмым выxoдo i блока и с вторым входом первого элемента И-НЕ, нулевой выход четвертого триггера и единичный выход пятого триггера соединены соответственно с первым и вторым входами второго элемента И-НЕ, третий вход которого соединен с единичным выходом первого триггера и с

fO

входом сброса третьего триггера, выходы первого и второго элементов И-НЕ соединены соответственно с информационными входами первого и второго триггеров.

3. Устройство по п. 1, о т л и - чающееся тем, что блок формирования адреса содержит первый, второй счетчики, коммутатор и элемент ИЛИ-НЕ, причем вход сброса подключен к входам сброса первого, второго счетчиков, тактовый вход и адресный и стробирующий выходы блока подключены соответственно к счетному входу первого счетчика, к выходу коммутатора и к выходу элемента ИЛИ-НЕ, второй стробирующий вход блока сое- дашен со счетным входом второго счетчика, с первым управляющим входом коммутатора и с первым входом элемента ШШ-НЕ, второй вход которого и второй управляющий вход коммутатора соединены с первым строби- 25 рующим входом блока, выходы первого, второго счетчиков подключены к первому, второму информационным входам коммутатора.

5

20

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления обменом информацией процессора с памятью | 1986 |

|

SU1325494A1 |

| Устройство для сопряжения процессора с памятью | 1983 |

|

SU1149272A1 |

| Устройство для управления обменом информацией процессора с памятью | 1988 |

|

SU1587525A1 |

| Устройство для сортировки информации | 1986 |

|

SU1365075A1 |

| Микропрограммное устройство управления с динамической памятью | 1985 |

|

SU1260954A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ КАЧЕСТВА МАГНИТНОГО НОСИТЕЛЯ | 1992 |

|

RU2040050C1 |

| Устройство для сопряжения процессора с памятью | 1989 |

|

SU1742823A1 |

| Устройство для контроля записи информации в блоках памяти | 1982 |

|

SU1076954A1 |

| Устройство для сопряжения | 1983 |

|

SU1104498A1 |

| Многоканальное устройство ввода аналоговой информации | 1987 |

|

SU1418726A1 |

Изобретение относится к области цифровой вычислительной техники, в частности к устройствам для сопряжения с памятью, и может быть использовано для построения систем с быстрой памятью. Целью изобретения является расширение функциональных возможностей устройства за счет организации приоритета по ииклу записи информации. Устройство содержит блок управления, блок формирования адреса, блок формирования зоны и блок памяти. Логика управления устройства обеспечивает более высокий приоритет сигналов записи в память по сравнению с сигналами чтения из памяти при одновременном поступлении обоих сигналов. 2 з.п. ф-лы, 1 ил. 1С 00 1С

С Cfl g СИ с I

Составитель С.Бурухин Редактор С.Пекарь Техред М.Ходанич Корректор Е.Сирохман

Заказ 7269/49 Тираж 670Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Устройство для сопряжения | 1979 |

|

SU881722A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство управления обращением к памяти | 1975 |

|

SU556444A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-01-07—Публикация

1985-07-03—Подача