(54) АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1979 |

|

SU809555A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1277396A1 |

| Аналого-цифровой преобразователь | 1979 |

|

SU884122A1 |

| Способ преобразования аналогового сигнала в цифровой сигнал и устройство для его осуществления | 1977 |

|

SU892704A1 |

| Аналого-цифровой преобразователь на приборах с зарядовой связью | 1980 |

|

SU947959A1 |

| ЦИФРОАНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ | 2012 |

|

RU2485681C1 |

| ПРЕОБРАЗОВАТЕЛЬ ИНТЕРВАЛА ВРЕМЕНИ В ПОСТОЯННОЕ НАПРЯЖЕНИЕ | 1990 |

|

RU2007028C1 |

| Аналого-цифровой преобразователь | 1980 |

|

SU1112549A1 |

| Аналого-цифровой преобразователь изображений | 1990 |

|

SU1798759A1 |

| Устройство для измерения отклонения частоты от номинального значения | 1984 |

|

SU1322450A1 |

I

Изобретение относится к устройствам импульсной техники и предназначено для использования в цифровых измерительных приборах, устройсвах автоматического управления, в системах сбора и обработки данных.

Известны аналого-цифровые преобразователи поразрядного уравновешивания, содержащие устройство сравнения, на один из входов которого подается входной сигнал, а аыход подключен к устройству управления, выходы устройства управления соединены с п входами (п - число двоичных разрядов преобразователя) цифро-аналогового преобразователя, выход которого соединен со вторьм входой устройства сравнения 1J.

Недостатком этих преобразователе является большое число логических элементов (до 8-10 двухвходовых элементов на один разряд), необходимых для построения схемы управления которые занимают большую площадь и потребляют значительную мощность.

Наиболее близким по технической сущности и достигаемому результату к предлагаемому является аналогоцифровой преобразователь, содержащи источник входного сигнала, устройство сравнения, выход которого соединен с вхсздом устройства управления, выход которого подсоединён к первому входу устройства колда утации, первый выход последнего через устройство аналогового хранения соединен с первым входом устройства сравнения, источник эталонного сигнала, подключенный к первому входу формирователя зарядов 2.

Недостатком этого преобразователя является низкое быстродействие, обусловленное большим временем выравнивания поверхностных потенциалов

s под двумя идентичными электродами (затворами), с помощью которых осуществляется деление пополам эталонных зарядов в формирователе зарядов.

Цель изобретения - повышение бы0стродействия преобразователя.

Поставленная цель достигается тем, что в аналого-цифровой преобразователь , содержащий источник входного сигнала, устройство сравнения, выход

5 которого соединен с входом устройства управления, выход которого подключен к первому входу устройства коммутации, первый выход последнего через устройство аналогового хранения соеди0нен с первым входом устройства сравнения, источникэталонного сигнала, подключенный к первому входу формирователя зарядов, введена линия задержки с весовыми отводами, вход которой соединен с выходом формирователя зарядов, выход - со вторым устройства коммутации/ второй ВЫХОД которого подключен ко второму входу устройства сравнения, а дополнительный выход устройства управления подключен к первому дополнительному входу формирователя зарядов, к второму дополнительному входу которого подключен источник входного сигнала, причем линия задержки с весовыми отводами выполнена в виде сдвиговой линии на приборах с зарядовой связью с весовыми отводами на основе разрезанных электродов или в виде сдвиговой линии на приборах с зарядовой связью с, боковыми отводами и резистивной матрицы типа R-2R разрядные выводы которой подключены к боковым отводам сдвиговой линии на приборах с зарядовой связью.

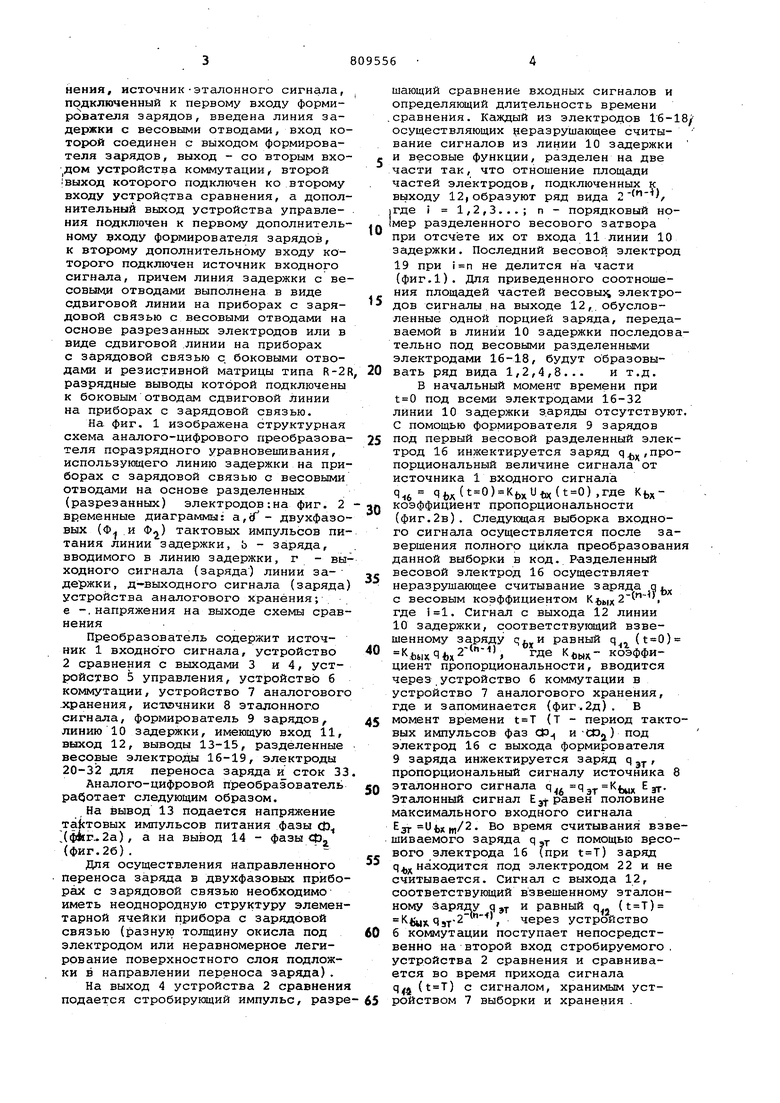

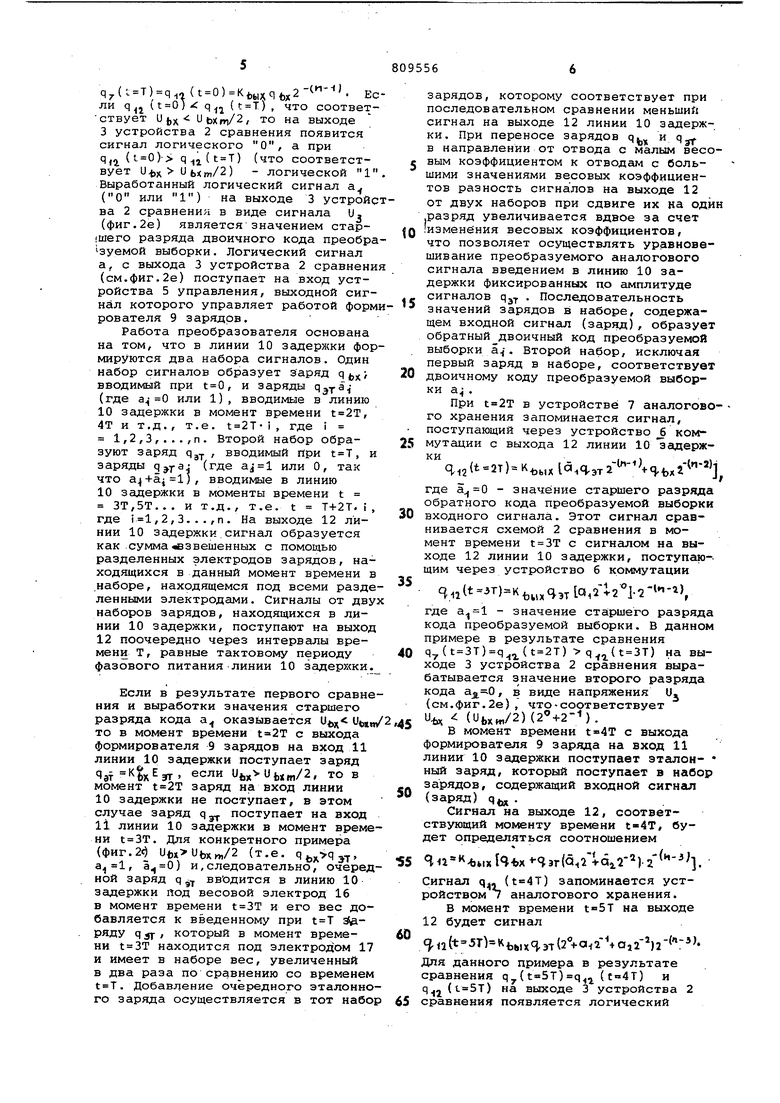

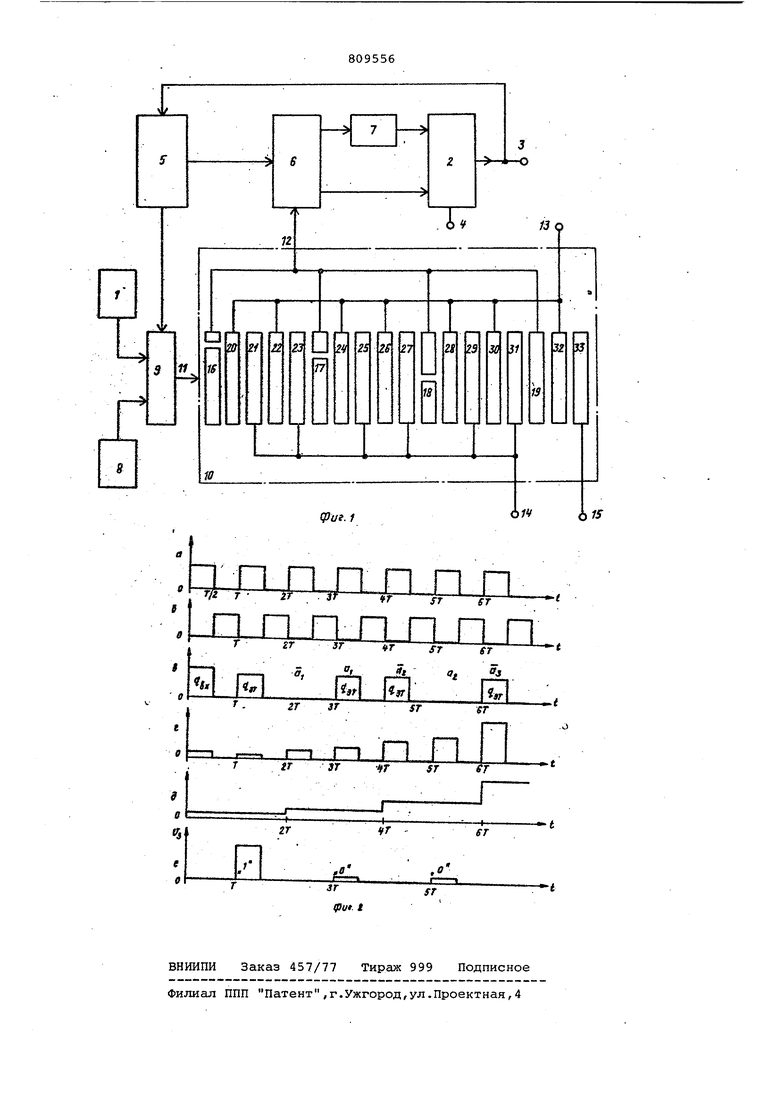

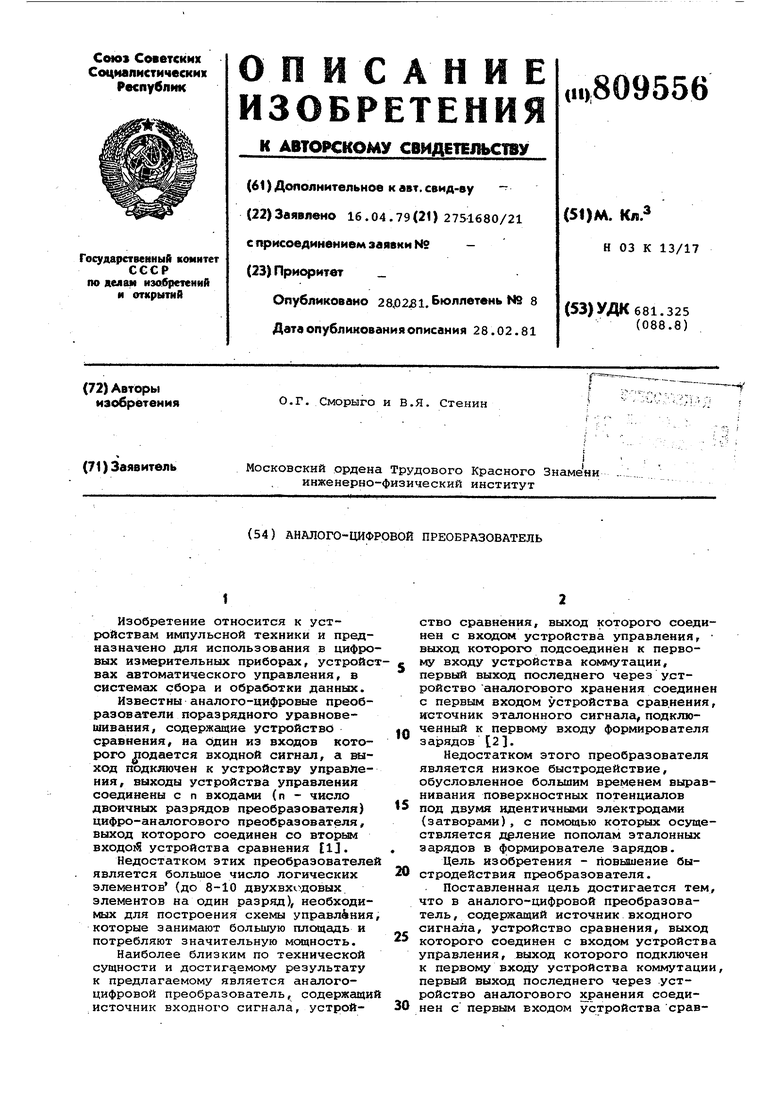

На фиг. 1 изображена структурная схема аналого-цифрового преобразователя поразрядного уравновешивания, использукидего линию задержки на приборах с зарядовой связью с весовыми отводами на основе разделенных (разрезанных) электродов:на фиг. 2 временные диаграммы: а, двухфазовых (Ф и ) тактовых импульсов питания линии задержки, b - заряда, вводимого в линию задержки, г - выходного сигнала (заряда) линии за- держки, д выходного сигнала (заряда) устройства аналогового хранения; е -.напряжения на выходе схемы сравнения

Преобразователь содержит источник 1 входного сигнала, устройство 2 сравнения с выходами 3 и 4, устройство 5 управления, устройство б коммутации, устройство 7 аналогового .хранения, источники 8 эталонного сигнала, формирователь 9 зарядов, линию 10 задержки, имеющую вход 11, выход 12, выводы 13-15, разделенные весовые электроды 16-19, электроды 20-312 для переноса заряда и сток 33

Аналого-цифровой преобразователь работает следующим образом.

На вывод 13 подается напряжение та|стовых импульсов питания фазы ф ,(), а на вывод 14 - фазы ср. (фиг.26).Для осуществления направленного переноса заряда в двухфазовых приборах с зарядовой связью необходимо иметь неоднородную структуру элементарной ячейки прибора с зарядовой связью (разную толщину окисла под электродом или неравномерное легирование поверхностного слоя подложки в направлении переноса заряда).

На выход 4 устройства 2 сравнения подается стробирующий импульс, разрешающий сравнение входных сигналов и определяющий длительность времени .сравнения. Каждый из электродов le-l осуществляющих церазрушающее считывание сигналов из линии 10 задержки и весовые функции, разделен на две части так, что отношение площади частей электродов, подключенных к выходу 12, образуют ряд вида Где i 1,2,3...; п - порядковый но1мер разделенного весового затвора при отсчёте их от входа 11 линии 10 задержки. Последний весовой электрод 19 при не делится на части (фиг.1). Для приведенного соотношения площадей частей весовьи электродов сигналы на выходе 12,, обусловленные одной порцией заряда, передаваемой в линии 10 задержки последовательно под весовыми разделенными электродами 16-18, будут образовывать ряд вида 1,2,4,8... и т.д. В начальный момент времени при под всеми электродами 16-32 линии 10 задержки заряды отсутствуют С помощью формирователя 9 зарядов под первый весовой разделенный электрод 16 инжектируется заряд q,пропорциональный величине сигнала от источника 1 входного сигнала qfcA(t 0) bxtJf)x() .где Kfexкоэффициент пропорциональности (фиг.2в). Следунадая выборка входного сигнала осуществляется после завершения полного цикла преобразовани данной выборки в код. Р-азделенный весовой электрод 16 осуществляет неразрушающее считывание заряда q с весовым коэффициентом Ktbix где . Сигнал с выхода 12 линии 10 задержки, соответствующий взвешенному заряду q,JИ равный ц( 0)

К,ьыхЯь2 тае коэффициент пропорциональности, вводится через устройство 6 коммутации в устройство 7 аналогового хранения, где и запоминается (фиг.2д). В момент времени (Т - период тактовых импульсов фаз СР и СО) под электрод 16 с выхода формирователя 9 заряда инжектируется заряд ц, пропорциональный сигналу источника 8 эталонного сигнала q qj.Kt, Е j Эталонный сигнал Eyj-равен половине максимального входного сигнала ,хт/2- Во время считывания взвешиваемого заряда q т с помощью врсового электрода 16 (при ) заряд q находится под электродом 22 и не считывается. Сигнал с выхода 12, соответствующий взвешенному эталонному заряду q jT и равный q (t T) q3., через устройство 6 коммутации поступает непосредственно на второй вход стробируемого . устройства 2 сравнения и сравнивается во время прихода сигнала Чй ( сигналом, хранимым устройством 7 выборки и хранения . q7()q,, (t 0)Kfcb|xqbx2 - ЕС ЛИ q j () q () , что соответствует и |,) : UbXfn/2, то на выходе 3 устройства 2 сравнения появится сигнал логического О, а при 4f2. (- 0) (что соответствует U Ubxm/2) - логической 1 Выработанный логический сигнал а (О или 1) на выходе 3 устройс ва 2 сравнения в виде сигнала U, (фиг.2е) является значением стар(шего разряда двоичного кода преобра зуемой выборки. Логический сигнал а, с выхода 3 устройства 2 сравнени (см.фиг.2е) поступает на вход устройства 5 управления, выходной сигнал которого управляет работой форм рователя 9 зарядов. Работа преобразователя основана на том, что в линии 10 задержки фор мируются два набора сигналов. Один набор сигналов образует заряд q,; вводимый при t 0, и заряды (где или 1), вводимые в линию 10 задержки в момент времени , 4т и т.д., т.е. , где i 1,2,3,...,п. Второй набор образуют заряд q , вводимый при , и заряды (где или О, так что , вводимые в линию 10 задержки в моменты времени t ЗТ,5Т... и т.д., т.е. t Т+2Т. i, где ,2,3...,п. На выходе 12 линии 10 задержки сигнал образуется как-сумма взвешенных с помощью разделенных электродов зарядов, находящихся в данный момент времени в наборе, находящемся под всеми разде ленными электродами. Сигналы от дву наборов зарядов, находящихся в линии 10 задержки, поступают на выход 12 поочередно через интервалы времени Т, равные тактовому периоду фазового питания линии 10 задерх ки. Если в результате первого сравне ния и выработки значения старшего разряда кода а оказывается ь.гг то в момент времени с выхода формирователя 9 зарядов на вход 11 линии 10 задержки поступает заряд Чэ если JьJ( то в момент заряд на вход линии 10задержки не поступает, в этом случае заряд q поступает на вход 11линии 10 задержки в момент време ни . Для конкретного примера (фиг.2 ,/2 (т.е. , ) и,следовательно, очеред ной заряд q -j вводится в линию 10 задержки под весовой электрод 16 в момент времени и его вес добавляется к введенному при г ряду , который в момент времени находится под электродом 17 и имеет в наборе вес, увеличенный в два раза по сравнению со временем . Добавление очередного эталонно го заряда осуществляется в тот набо зарядов, которому соответствует при последовательном сравнении меньший сигнал на выходе 12 линии 10 задержки. При переносе зарядов q и q в направлении от отвода с малым весовым коэффициентом к отводам с большими значениями весовых коэффициентов разность сигналов на выходе 12 от двух наборов при сдвиге их на один разряд увеличивается вдвое за счет изменения весовых коэффициентов, что позволяет осуществлять уравновешивание преобразуемого аналогового сигнала введением в линию 10 задержки фиксированных до амплитуде сигналов qjy . Последовательность значений зарядов в наборе, содержащем входной сигнал (заряд), образует обратный двоичный код преобразуемой выборки . Второй набор, исключая первый заряд в наборе, соответствует двоичному коду преобразуемой выбор ки а . При в устройстве 7 аналогового хранения запоминается сигнал, поступающий через устройство 6 коммутации с выхода 12 линии 10 задержq,)K,,q эт2 Яbxг , где - значение старшего разряда обратного кода преобразуемой выборки входного сигнала. Этот сигнал сравнивается схемой 2 сравнения в момент времени с сигналом на выходе 12 линии 10 задержки, поступаю-щим через устройство 6 коммутации S.)KfeMx 3Tla.2-b. где - значение старшего разряда кода преобразуемой выборки. В данном примере в результате сравнения q()q() q() на выходе 3 устройства 2 сравнения вырабатывается значение второго разряда кода , в виде напряжения U (см.фиг.2е), что-соответствует (,/2)(2°+2-}. В момент времени с выхода формирователя 9 заряда на вход 11 линии 10 задержки поступает эталон- ный заряд, который поступает в набор зарядов, содержащий входной сигнал (заряд) q . Сигнал на выходе 12, соответствующий моменту времени t-4T, будет определяться соотношением Чп,(о, Сигнал Qi, () запоминается устройством аналогового хранения. В момент времени на выходе 12 будет сигнал ()Kb,xC},3T(2Vai2%ai2-) Для данного примера в результате сравнения q()q () и q,j() на выходе 3 устройства 2 сравнения появляется логический сигнал в виде U (см.фиг.2е, что соответствует Ufcx зт (2 +2 ) . На фиг.2 показаны временные диаграммы для уравновешивания входного заря да q, только в трех разрядах преобразователя, соответствующий двоичный -код будет 100. Формирование младшего разряда кода происходит на последнем этапе, начиная с моментавремени (n-l)T В этот момент времени под весовым электродом 19 находится заряд QJJ, а под остальными весовыми разделенны ми электродами в направлении от ве|сового электрода 19 к весовому элекроду 16 - заряды величиной а q gt Выходной сигнал с выхода 12, через устройство б коммутации вводится и запоминается в устройстве 7 аналогового хранения. Через такт фазового питания в момент времени t(2n-l)T t+T на другой вход устройства 2 сравнения поступает сигнал ()ЧыхЯэт(ч-«- сна). Эти два сигнала сравниваются устройством 2 сравнения, на выходе 3 которого вырабатывается логический сигнал ац, соответствующий значению младшего разряда кода. Логический сигнал а, вводится в линию 10 задерж ки- в виде заряда величиной Двоичный код преобразуемого аналогового сигнала формируется в процессе преобразования последовательно на выходе 3 устройства 2 сравнения . в вище импульсного сигнала ид. Кроме этого, после завершения преобразования он содержится в виде зарядов ajqjT в линии 10 задержки.и может быть выведен оттуда в виде пос ледовательного кода через сток 33 и вывод 15. Значения двоичного кода а4 чередуются в разрядах линии 10 задер ки со значениями обратного двоичного кода 34 преобразованной выборки вход ного .аналогового сигнала. Формула изобретения 1.Аналого-цифровой преобразователь, содержащий источник входного сигнала, устройство сравнения, выход которого соединен с входом устройства управления, выход которого подключен к первому входу устройства коммутации, первый выход последнего через устройство аналогового хранения соединен с первым входом устройства сравнения, источник эталонного сигнала, подключенный к первому входу формирователя зарядой, о тличающийся тем, что, с целью повышения быстродействия преобразователя, в него введена Ътиния задержки с весовыми отводами, вход которой соединен с выходом формирователя зарядов, выход - со вторым входом устройства коммутации,, второй выход которого подключен ко второму входу устройства сравнения, а дополнительный выход устройства управле1вия подключен к первому дополнительному входу формирователя зарядов, к второму дополнительному входу которого подключен источник входного сигнала. 2.Преобразователь по п.1, о тл и ч а ю щ и и с я тем, что линия задержки с весовыми отводами выполнена в виде сдвиговой линии на приборах с зарядовой связью с весовыми отводами на основе разрезанных электродов. 3.Преобразователь по п.1, о тли чающийся тем, что линия, задержки с весовыми отводами выполнена в виде сдвиговой линии на приборах с зарядовой связью с боковыми отводами и резистивной матрицы типа R-2R, разрядные выводы которой подключены .к боковым отводам сдвиговой линии на приборах с зарядовой связью. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетелц ство СССР №167373, кл. Н 03 К 13/02,. 1966. 2.Патент Франции 2343369, кл. Н 03 К 13/02, 1977 (прототип).

I

/Jo

Авторы

Даты

1981-02-28—Публикация

1979-04-16—Подача