Изобретение относится к измерительной технике и может быть использовано при разработке устройств для приема и обработки сигнала.

Целью изобретения является увеличение диапазона преобразуемых частот.

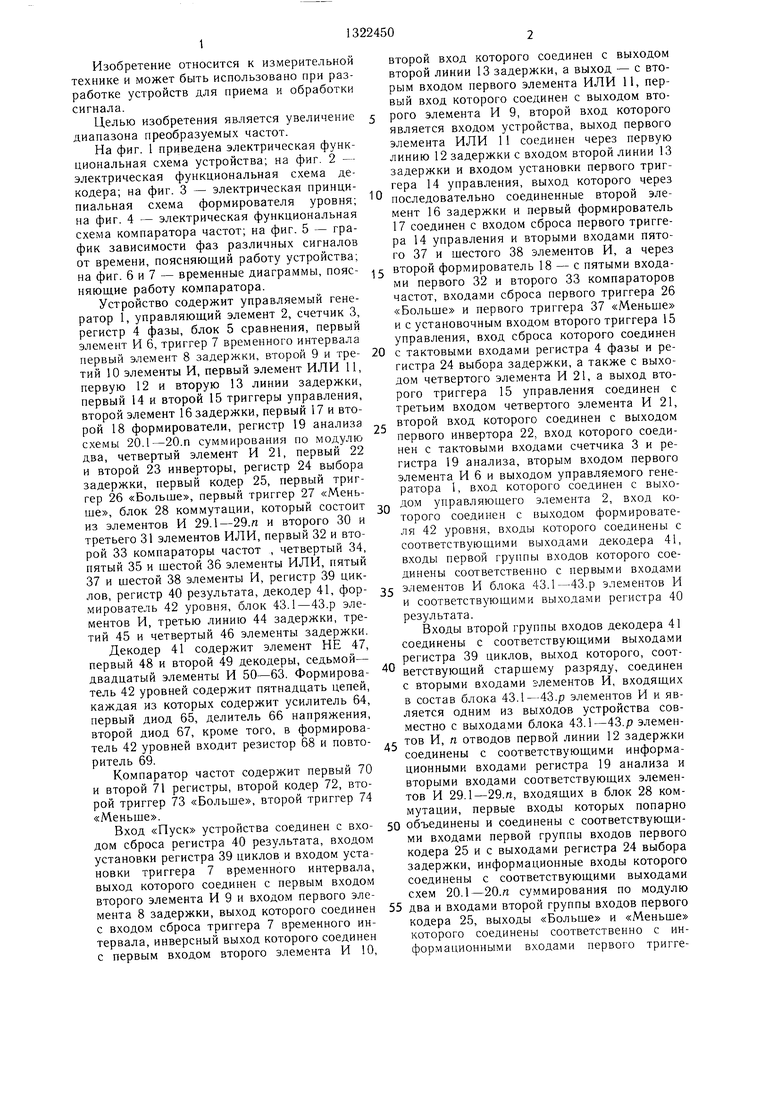

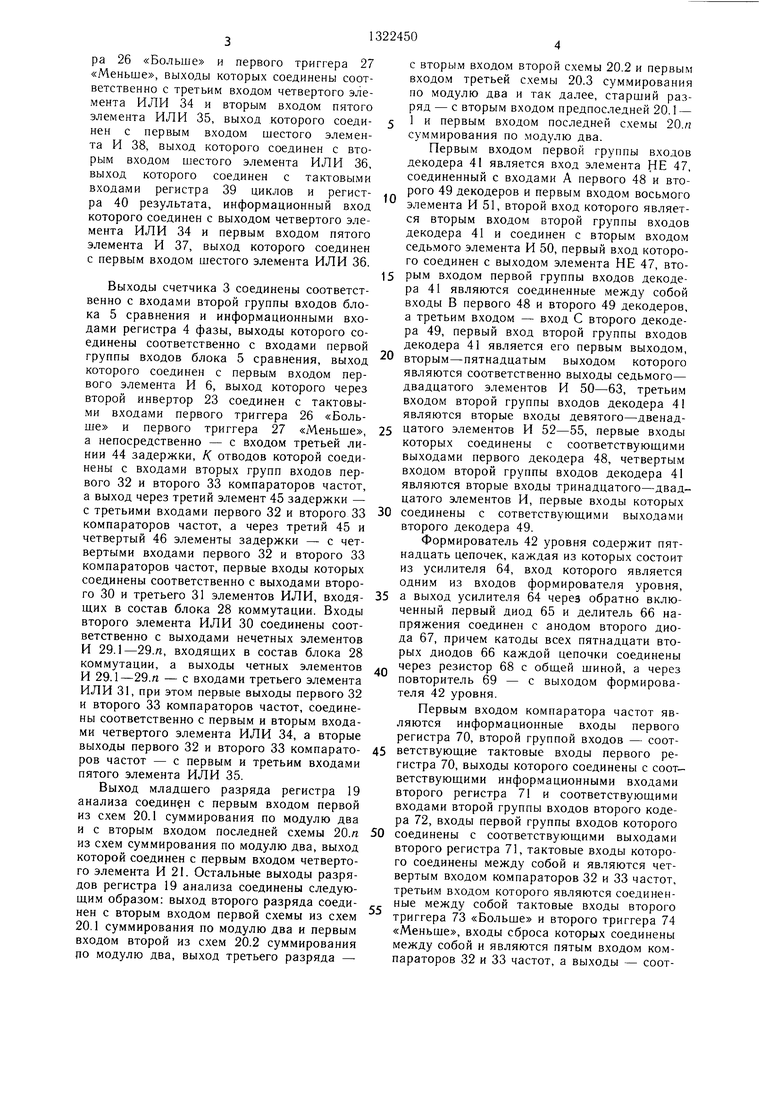

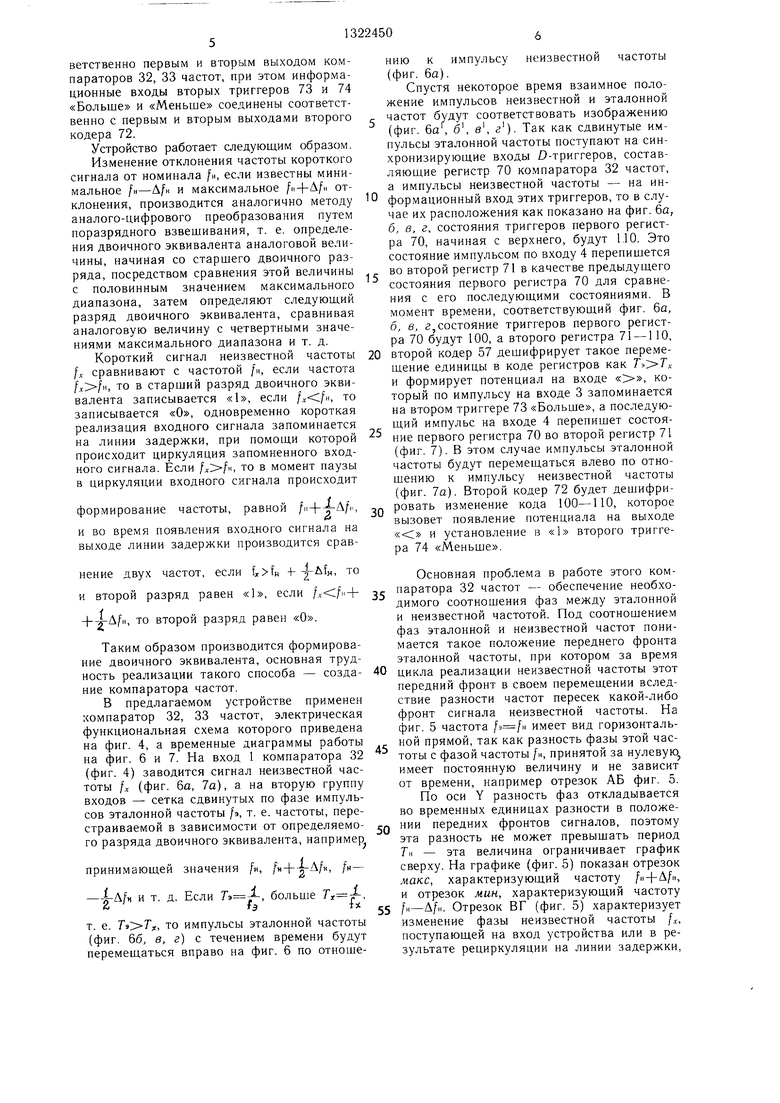

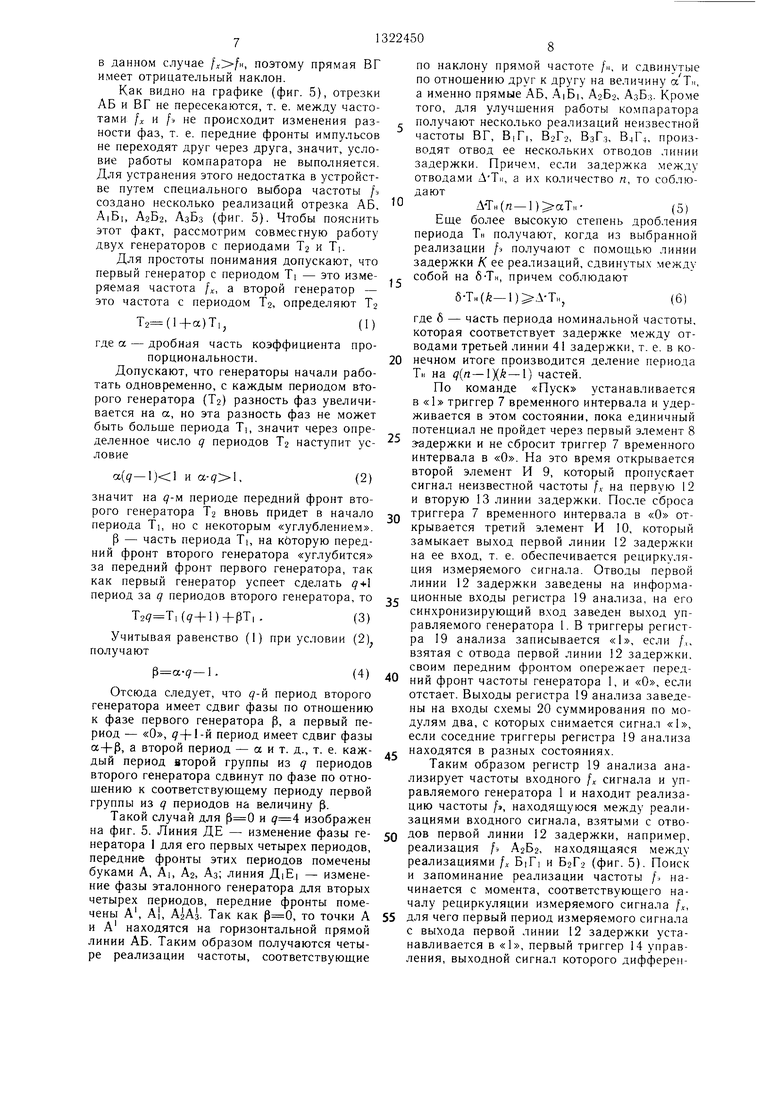

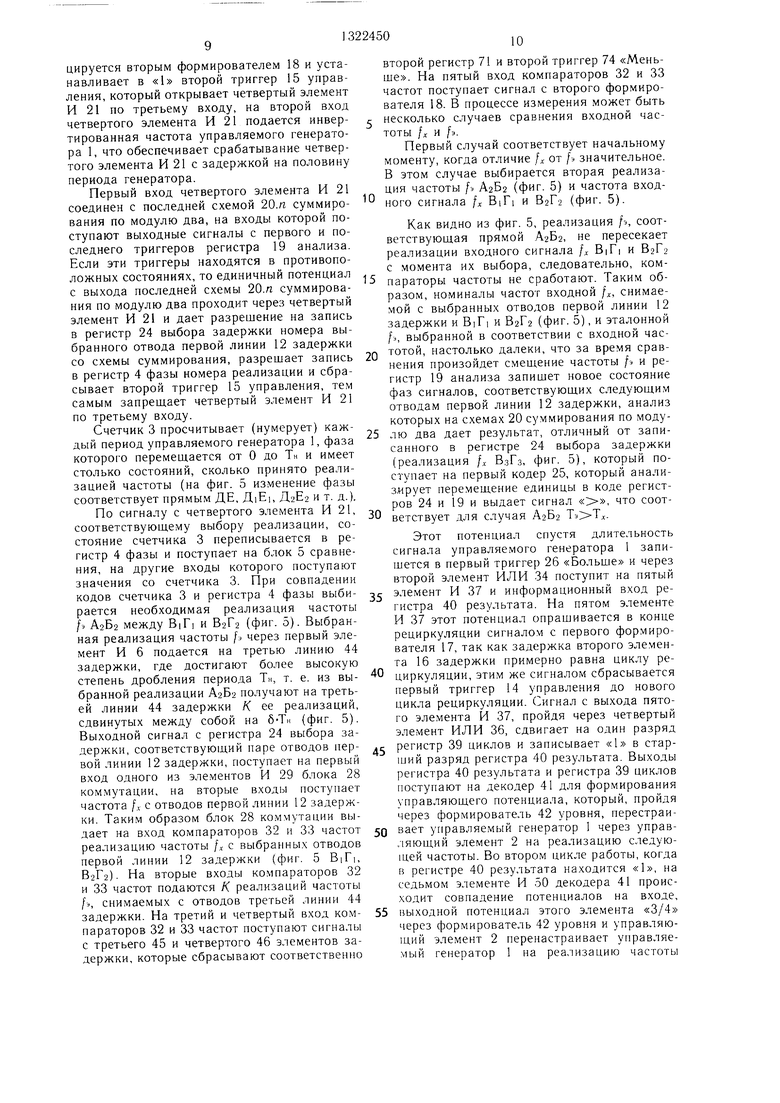

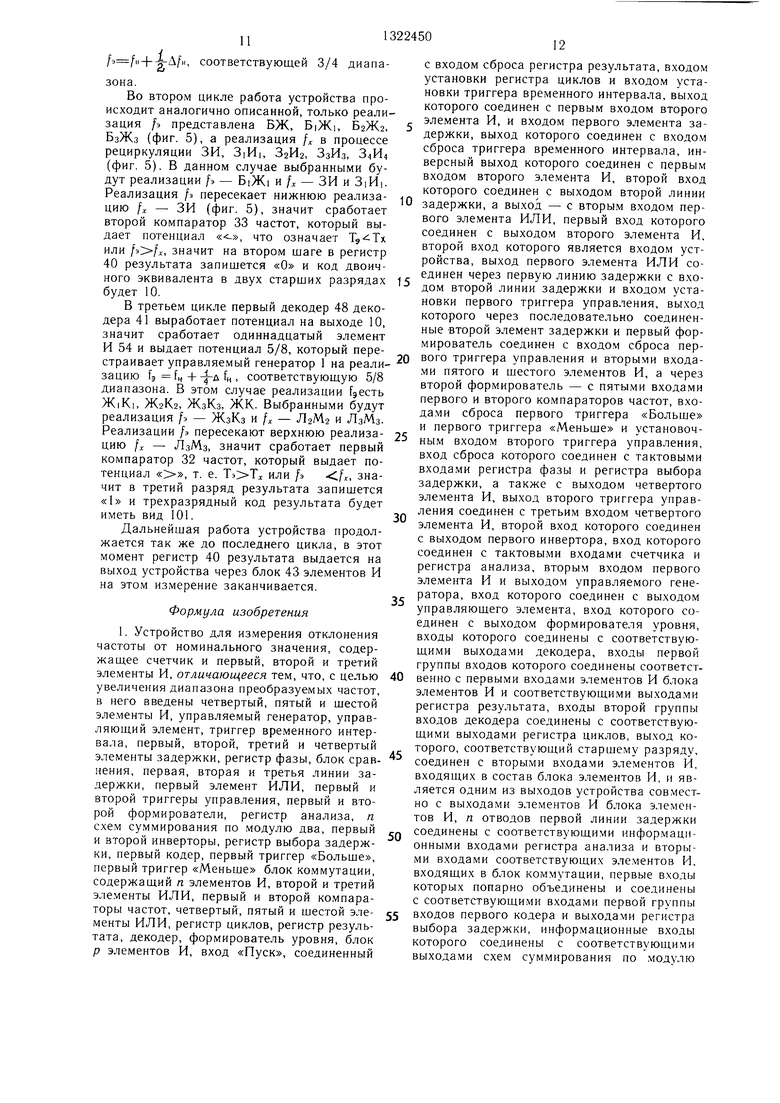

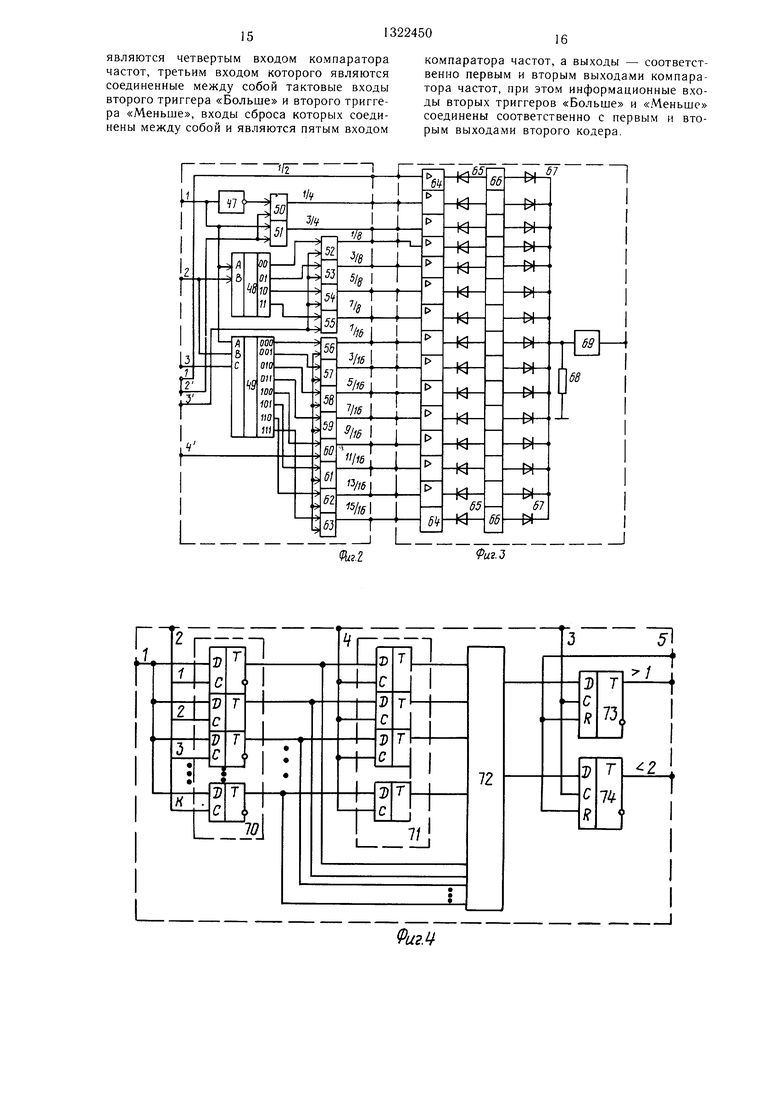

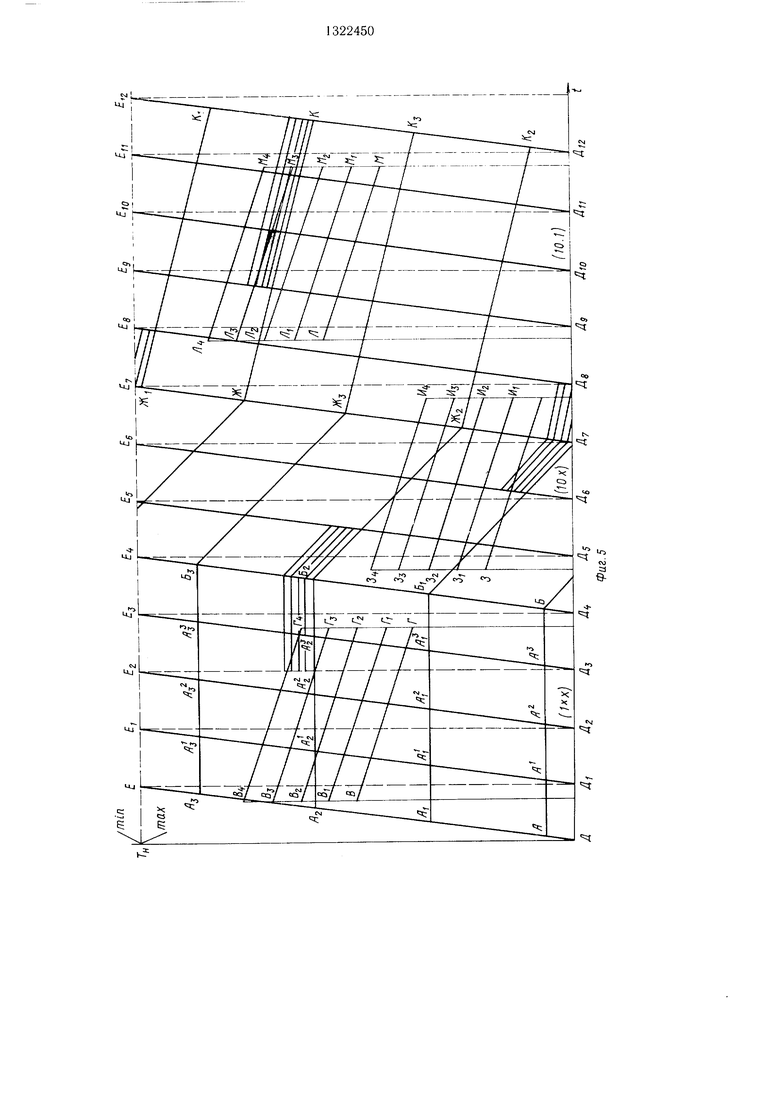

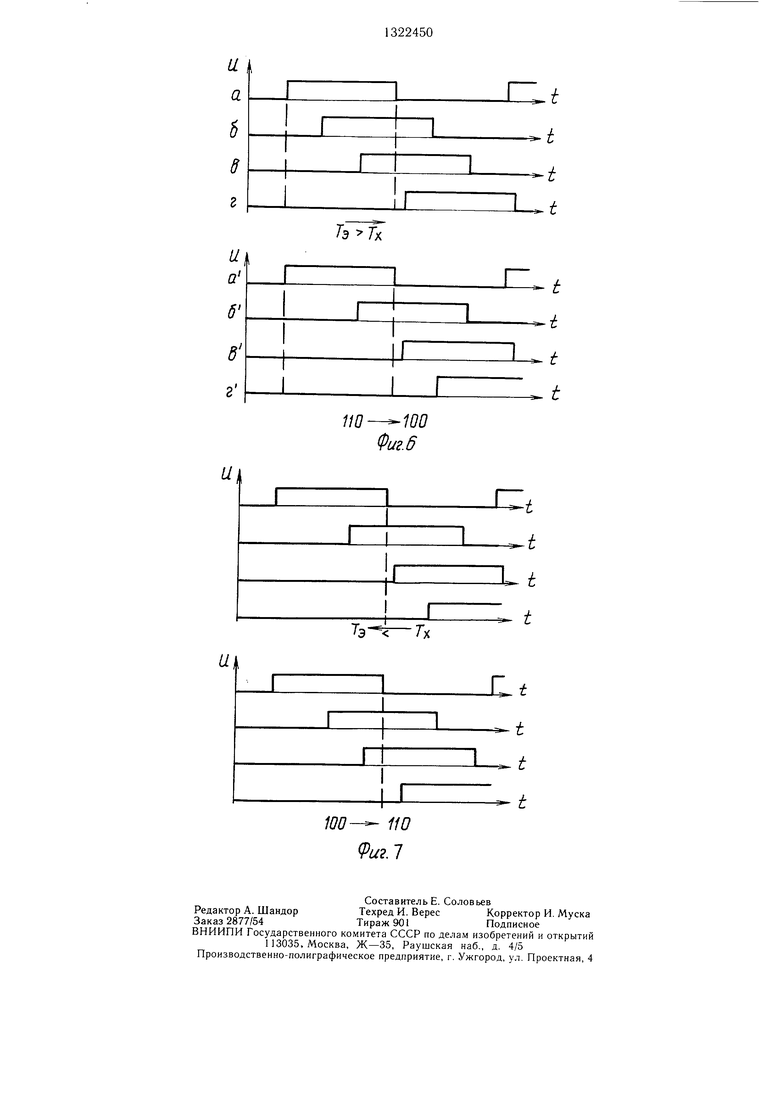

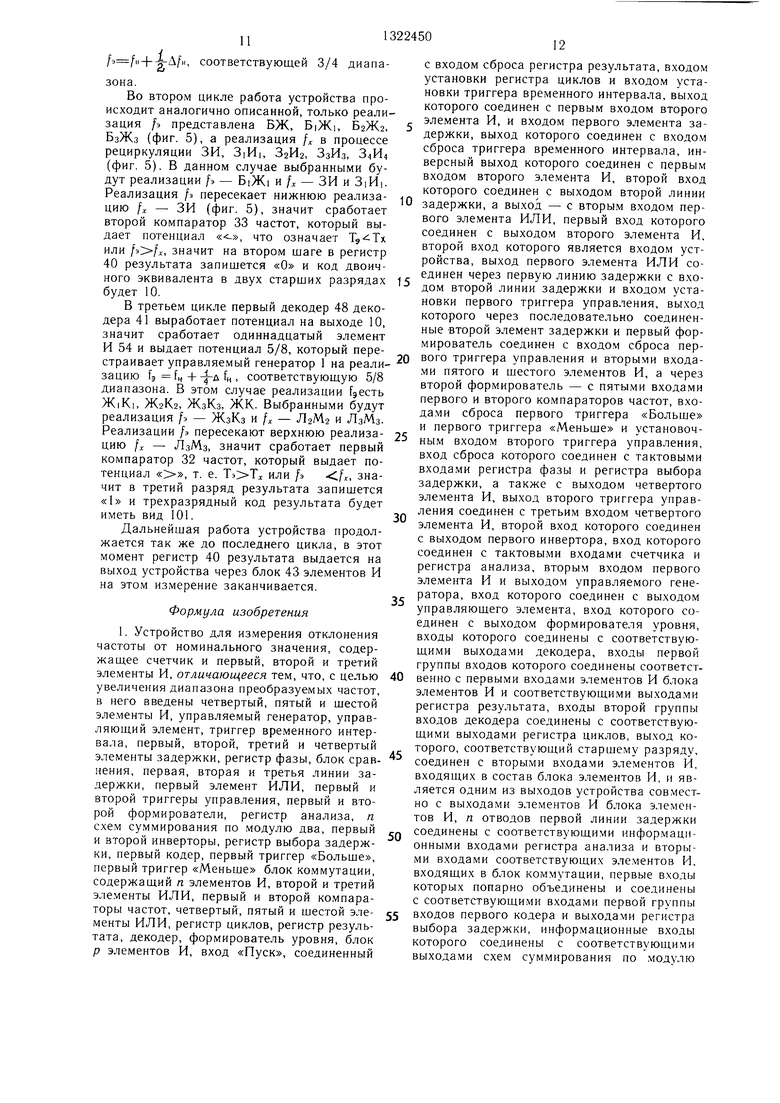

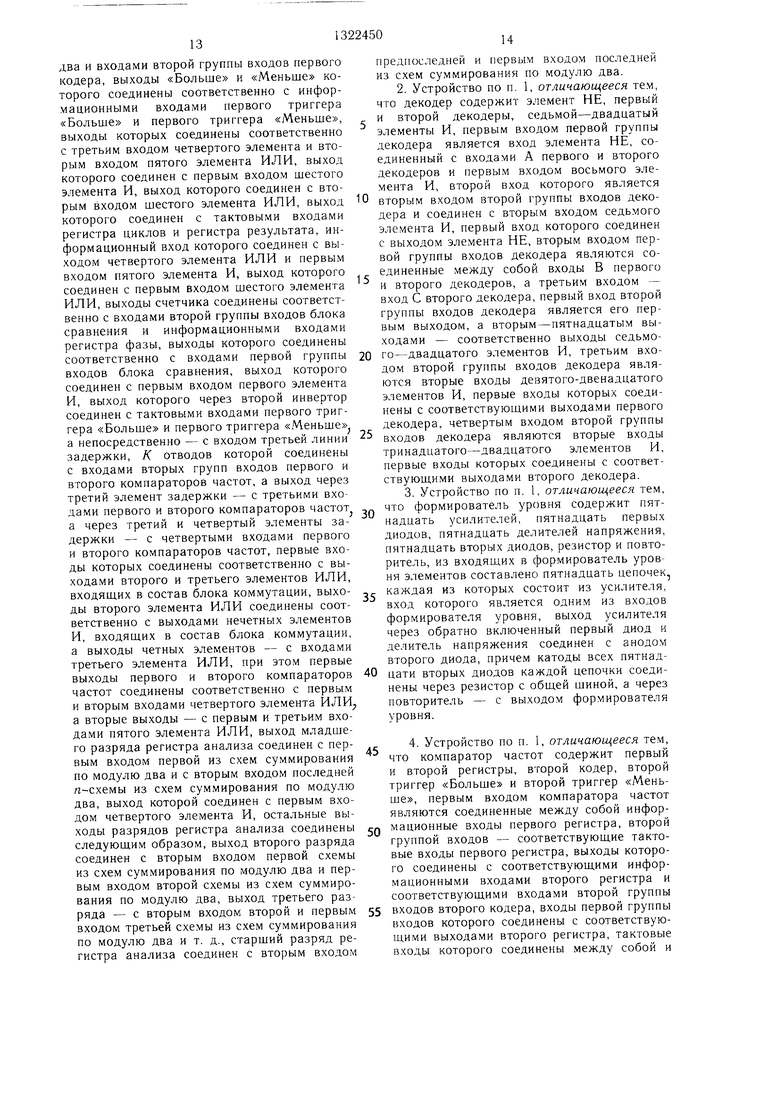

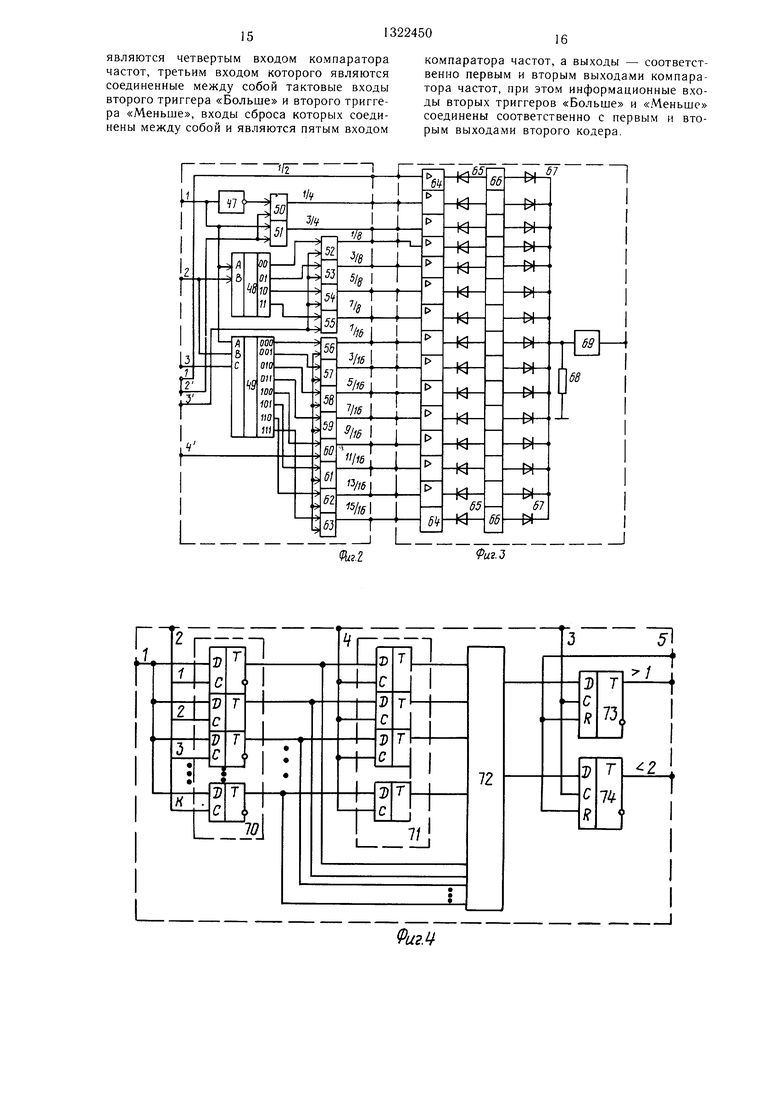

На фиг. 1 приведена электрическая функциональная схема устройства; на фиг. 2 - электрическая функциональная схема декодера; на фиг. 3 - электрическая принципиальная схема формирователя уровня; на фиг. 4 - электрическая функциональная схема компаратора частот; на фиг. 5 - график зависимости фаз различных сигналов от времени, поясняющий работу устройства; на фиг. 6 и 7 - временные диаграммы, поясняющие работу компаратора.

Устройство содержит управляемый генератор 1, управляющий элемент 2, счетчик 3, регистр 4 фазы, блок 5 сравнения, первый элемент И 6, триггер 7 временного интервала первый элемент 8 задержки, второй 9 и третий 10 элементы И, первый элемент ИЛИ 11, первую 12 и вторую 13 линии задержки, первый 14 и второй 15 триггеры управления, второй элемент 16 задержки, первый 17 и второй 18 формирователи, регистр 19 анализа схемы 20.1-20.п суммирования по модулю два, четвертый элемент И 21, первый 22 и второй 23 инверторы, регистр 24 выбора задержки, первый кодер 25, первый триггер 26 «Больше, первый триггер 27 «Меньше, блок 28 коммутации, который состоит из элементов И 29.1-29.п и второго 30 и третьего 31 элементов ИЛИ, первый 32 и второй 33 компараторы частот , четвертый 34, пятый 35 и шестой 36 элементы ИЛИ, пятый 37 и шестой 38 элементы И, регистр 39 циклов, регистр 40 результата, декодер 41, формирователь 42 уровня, блок 43.1-43.р элементов И, третью линию 44 задержки, третий 45 и четвертый 46 элементы задержки.

Декодер 41 содержит элемент НЕ 47, первый 48 и второй 49 декодеры, седьмой- двадцатый элементы И 50-63. Формирователь 42 уровней содержит пятнадцать цепей, каждая из которых содержит усилитель 64, первый диод 65, делитель 66 напряжения, второй диод 67, кроме того, в формирователь 42 уровней входит резистор 68 и повторитель 69.

Компаратор частот содержит первый 70 и второй 71 регистры, второй кодер 72, второй триггер 73 «Больше, второй триггер 74 «Меньше.

Вход «Пуск устройства соединен с входом сброса регистра 40 результата, входом установки регистра 39 циклов и входом установки триггера 7 временного интервала, выход которого соединен с первым входом второго элемента И 9 и входом первого элемента 8 задержки, выход которого соединен с входом сброса триггера 7 временного интервала, инверсный выход которого соединен с первым входом второго элемента И 10,

0

второй вход которого соединен с выходом второй линии 13 задержки, а выход - с вторым входом первого элемента ИЛИ 11, первый вход которого соединен с выходом второго элемента И 9, второй вход которого является входом устройства, выход первого элемента ИЛИ 11 соединен через первую линию 12 задержки с входом второй линии 13 задержки и входом установки первого триггера 14 управления, выход которого через последовательно соединенные второй элемент 16 задержки и первый формирователь 17 соединен с входом сброса первого триггера 14 управления и вторыми входами пятого 37 и шестого 38 элементов И, а через

5 второй формирователь 18 - с пятыми входами первого 32 и второго 33 компараторов частот, входами сброса первого триггера 26 «Больше и первого триггера 37 «Меньше и с установочным входом второго триггера 15 управления, вход сброса которого соединен

0 с тактовыми входами регистра 4 фазы и регистра 24 выбора задержки, а также с выходом четвертого элемента И 21, а выход второго триггера 15 управления соединен с третьим входом четвертого элемента И 21,

r второй вход которого соединен с выходом первого инвертора 22. вход которого соединен с тактовыми входами счетчика 3 и регистра 19 анализа, вторым входом первого элемента И 6 и выходом управляемого генератора 1, вход которого соединен с выхо дом управляющего элемента 2, вход которого соединен с выходом формирователя 42 уровня, входы которого соединены с соответствующими выходами декодера 41, входы первой группы входов которого соединены соответственно с первыми входа.ми

5 элементов И блока 43.1-43.р элементов И и соответствующими выходами регистра 40 результата.

Входы второй группы входов декодера 41 соединены с соответствующими выходами регистра 39 циклов, выход которого, соответствующий старщему разряду, соединен с вторыми входами элементов И, входящих в состав блока 43.1-43.р элементов И и является одним из выходов устройства совместно с выходами блока 43.1-43. р элеменс тов И, п отводов первой линии 12 задержки соединены с соответствующими информационными входами регистра 19 анализа и вторыми входами соответствующих элементов И 29.1-29.п, входящих в блок 28 коммутации, первые входы которых попарно

0 объединены и соединены с соответствующими входами первой группы входов первого кодера 25 и с выходами регистра 24 выбора задержки, информационные входы которого соединены с соответствующими выходами схем 20.1-20.п суммирования по модулю

5 два и входами второй группы входов первого кодера 25, выходы «Больше и «Меньше которого соединены соответственно с информационными входами первого тригге0

pa 26 «Больше и первого триггера 27 «Меньше, выходы которых соединены соответственно с третьим входом четвертого элемента ИЛИ 34 и вторым входом пятого элемента ИЛИ 35, выход которого соединен с нервым входом шестого элемента И 38, выход которого соединен с вторым входом шестого элемента ИЛИ 36, выход которого соединен с тактовыми входами регистра 39 циклов и регистра 40 результата, информационный вход которого соединен с выходом четвертого элемента ИЛИ 34 и первым входом пятого элемента И 37, выход которого соединен с первым входом шестого элемента ИЛИ 36.

Выходы счетчика 3 соединены соответственно с входами второй группы входов блока 5 сравнения и информационными входами регистра 4 фазы, выходы которого соединены соответственно с входами первой группы входов блока 5 сравнения, выход которого соединен с первым входом первого элемента И 6, выход которого через второй инвертор 23 соединен с тактовыми входами первого триггера 26 «Больше и первого триггера 27 «Меньше, а непосредственно - с входом третьей линии 44 задержки, К. отводов которой соединены с входами вторых групп входов первого 32 и второго 33 компараторов частот, а выход через третий элемент 45 задержки - с третьими входами первого 32 и второго 33 компараторов частот, а через третий 45 и четвертый 46 элементы задержки - с четвертыми входами первого 32 и второго 33 компараторов частот, первые входы которых соединены соответственно с выходами второго 30 и третьего 31 элементов ИЛИ, входящих в состав блока 28 коммутации. Входы второго элемента ИЛИ 30 соединены соответственно с выходами нечетных элементов И 29.1-29.л, входящих в состав блока 28 коммутации, а выходы четных элементов И 29.1-29.п - с входами третьего элемента ИЛИ 31, при этом первые выходы первого 32 и второго 33 компараторов частот, соединены соответственно с первым и вторым входами четвертого элемента ИЛИ 34, а вторые выходы первого 32 и второго 33 компараторов частот - с первым и третьим входами пятого элемента ИЛИ 35.

Выход младщего разряда регистра 19 анализа соединен с первым входом первой из схем 20.1 суммирования по модулю два и с вторым входом последней схемы 20.п из схем суммирования по модулю два, выход которой соединен с первым входом четвертого элемента И 21. Остальные выходы разрядов регистра 19 анализа соединены следующим образом: выход второго разряда соединен с вторым входом первой схемы из схем 20.1 суммирования по модулю два и первым входом второй из схем 20.2 суммирования по модулю два, выход третьего разряда -

0

5

0

5

0

5

0

5

0

5

с вторы1м входом второй схемы 20.2 и первым входом третьей схемы 20.3 суммирования по модулю два и так далее, старший разряд - с вторым входом предпоследней 20.1 - 1 и первым входом последней схемы 20.л суммирования по .модулю два.

Первым входом первой группы входов декодера 41 является вход элемента НЕ 47, соединенный с входами А первого 48 и второго 49 декодеров и первым входом восьмого элемента И 51, второй вход которого является вторым входом второй группы входов декодера 41 и соединен с вторым входом седьмого элемента И 50, первый вход которого соединен с выходом элемента НЕ 47, вторым входом первой группы входов декодера 41 являются соединенные между собой входы В первого 48 и второго 49 декодеров, а третьим входом - вход С второго декодера 49, первый вход второй группы входов декодера 41 является его первым выходом, вторым-пятнадцатым выходом которого являются соответственно выходы седьмого- двадцатого элементов И 50-63, третьим входом второй группы входов декодера 41 являются вторые входы девятого-двенадцатого элементов И 52-55, первые входы которых соединены с соответствующими выходами первого декодера 48, четвертым входом второй группы входов декодера 41 являются вторые входы тринадцатого-двадцатого элементов И, первые входы которых соединены с сответствующими выходами второго декодера 49.

Формирователь 42 уровня содержит пятнадцать цепочек, каждая из которых состоит из усилителя 64, вход которого является одним из входов формирователя уровня, а выход усилителя 64 через обратно включенный первый диод 65 и делитель 66 напряжения соединен с анодом второго диода 67, причем катоды всех пятнадцати вторых диодов 66 каждой цепочки соединены через резистор 68 с общей шиной, а через повторитель 69 - с выходом формирователя 42 уровня.

Первым входом компаратора частот являются информационные входы первого регистра 70, второй группой входов - соответствующие тактовые входы первого регистра 70, выходы которого соединены с соответствующими информационными входами второго регистра 71 и соответствующими входами второй группы входов второго кодера 72, входы первой группы входов которого соединены с соответствующими выходами второго регистра 71, тактовые входы которого соединены между собой и являются четвертым входом компараторов 32 и 33 частот, третьим входом которого являются соединенные между собой тактовые входы второго триггера 73 «Больще и второго триггера 74 «Меньще, входы сброса которых соединены между собой и являются пятым входом компараторов 32 и 33 частот, а выходы - соответственно первым и вторым выходом компараторов 32, 33 частот, при этом информационные входы вторых триггеров 73 и 74 «Больше и «Меньше соединены соответственно с первым и вторым выходами второго кодера 72.

Устройство работает следуюшим образом.

Изменение отклонения частоты короткого сигнала от номинала f, если известны минимальное /н-Afn и максимальное fa-i- f отклонения, производится аналогично методу аналого-цифрового преобразования путем поразрядного взвешивания, т. е. определения двоичного эквивалента аналоговой величины, начиная со старшего двоичного разряда, посредством сравнения этой величины с половинным значением максимального диапазона, затем определяют следуюш,ий разряд двоичного эквивалента, сравнивая аналоговую величину с четвертными значениями максимального диапазона и т. д.

Короткий сигнал неизвестной частоты л; сравнивают с частотой /и, если частота , то в старший разряд двоичного эквивалента записывается «1, если , то записывается «О, одновременно короткая реализация входного сигнала запоминается на линии задержки, при помощи которой происходит циркуляция запомненного входного сигнала. Если , то в момент паузы в циркуляции входного сигнала происходит

формирование частоты, равной / +4-A/ii,

2 и во время появления входного сигнала на

выходе линии задержки производится сравнение двух частот, если ,« -f- . то и второй разряд равен «1, если + -|-AfH, то второй разряд равен «О.

Таким образом производится формирование двоичного эквивалента, основная трудность реализации такого способа - создание компаратора частот.

В предлагаемом устройстве применен компаратор 32, 33 частот, электрическая функциональная схема которого приведена на фиг. 4, а временные диаграммы работы на фиг. 6 и 7. На вход 1 компаратора 32 (фиг. 4) заводится сигнал неизвестной частоты fx (фиг. 6а, 7а), а на вторую группу входов - сетка сдвинутых по фазе импульсов эталонной частоты /э, т. е. частоты, перестраиваемой в зависимости от определяемого разряда двоичного эквивалента, например

принимающей значения f, /«-f- -A/K, /н-

--й-А/ч и т. д. Если , больше , faijc

т. е. , то импульсы эталонной частоты (фиг. 66, в, г) с течением времени будут перемешаться вправо на фиг. 6 по отношению к импульсу неизвестной частоты (фиг. 6а).

Спустя некоторое время взаимное положение импульсов неизвестной и эталонной

частот будут соответствовать изображению (фиг. 6а , б , е , г ). Так как сдвинутые импульсы эталонной частоты поступают на синхронизирующие входы D-триггеров, составляющие регистр 70 компаратора 32 частот, а импульсы неизвестной частоты - на информационный вход этих триггеров, то в случае их расположения как показано на фиг. 6а, б, в, г, состояния триггеров первого регистра 70, начиная с верхнего, будут 1,10. Это состояние импульсом по входу 4 перепишется во второй регистр 71 в качестве предыдущего состояния первого регистра 70 для сравнения с его последуюш.ими состояниями. В момент времени, соответствующий фиг. ба, б, в, г,состояние триггеров первого регистра 70 будут 100, а второго регистра 71 -110,

0 второй кодер 57 дешифрирует такое перемещение единицы в коде регистров как и формирует потенциал на входе «, который по импульсу на входе 3 запоминается на втором триггере 73 «Больше, а последующий импульс на входе 4 перепишет состоя ние первого регистра 70 во второй регистр 71 (фиг. 7). В этом случае импульсы эталонной частоты будут перемешаться влево по отношению к импульсу неизвестной частоты (фиг. 7а). Второй кодер 72 будет дешифриQ ровать изменение кода 100-110, которое вызовет появление потенциала на выходе « и установление в «1 второго триггера 74 «Меньше.

Основная проблема в работе этого комс паратора 32 частот - обеспечение необходимого соотношения фаз между эталонной и неизвестной частотой. Под соотношением фаз эталонной и неизвестной частот понимается такое положение переднего фронта эталонной частоты, при котором за время

0 цикла реализации неизвестной частоты этот передний фронт в своем перемещении вследствие разности частот пересек какой-либо фронт сигнала неизвестной частоты. На фиг. 5 частота имеет вид горизонтальной прямой, так как разность фазы этой частоты с фазой частоты н, принятой за нулевую., имеет постоянную величину и не зависит от времени, например отрезок АБ фиг. 5. По оси Y разность фаз откладывается во временных единицах разности в положеQ НИИ передних фронтов сигналов, поэтому эта разность не может превышать период Тн - эта величина ограничивает график сверху. На графике (фиг. 5) показан отрезок макс, характеризующий частоту /н+А/н, и отрезок мин, характеризующий частоту

5 f«-А/н. Отрезок ВГ (фиг. 5) характеризует изменение фазы неизвестной частоты fx, поступающей на вход устройства или в результате рециркуляции на линии задержки.

5

7

в данном случае , поэтому прямая ВГ имеет отрицательный наклон.

Как видно на графике (фиг. 5), отрезки АБ и ВГ не пересекаются, т. е. между частотами /д: и /э не происходит изменения разности фаз, т. е. передние фронты импульсов не переходят друг через друга, значит, условие работы компаратора не выполняется. Для устранения этого недостатка в устройстве путем специального выбора частоты /э создано несколько реализаций отрезка АБ, А|Б|, А2Б2, АзБз (фиг. 5). Чтобы пояснить этот факт, рассмотрим совместную работу двух генераторов с периодами Т2 и TI.

Для простоты понимания допускают, что первый генератор с периодом TI - это измеряемая частота /х, а второй генератор - это частота с периодом Тз, определяют Т2

Т2(1+а)Т,,(I)

где а - дробная часть коэффициента пропорциональности.

Допускают, что генераторы начали работать одновременно, с каждым периодом второго генератора (Т2) разность фаз увеличивается на а, но эта разность фаз не может быть больше периода Ti, значит через определенное число q периодов Т2 наступит условие

а((7-1)1 и a-q.

значит на -м периоде передний фронт второго генератора Т2 вновь придет в начало периода TI, но с некоторым «углублением. Р - часть периода Ti, на которую передний фронт второго генератора «углубится за передний фронт первого генератора, так как первый генератор успеет сделать ( период за q периодов второго генератора, то

,(9+1)+рТ|.(3)

Учитывая равенство (1) при условии (2) получают

.(4)

Отсюда следует, что -й период второго генератора имеет сдвиг фазы по отношению к фазе первого генератора р, а первый период - «О, -f-1-й период имеет сдвиг фазы а+р, а второй период - а и т. д., т. е. каждый период второй группы из q периодов второго генератора сдвинут по фазе по отношению к соответствующему периоду первой группы из q периодов на величину р.

Такой случай для и ( изображен на фиг. 5. Линия ДЕ - изменение фазы генератора 1 для его первых четырех периодов, передние фронты этих периодов помечены буками А, AI, А2, АЗ; линия Д1Е| - изменение фазы эталонного генератора для вторых четырех периодов, передние фронты помечены А , А|, А2Аз. Так как , то точки А и А находятся на горизонтальной прямой линии АБ. Таким образом получаются четыре реализации частоты, соответствуюш,ие

22450о

о

по наклону прямой частоте /н, и сдвинутые по отношению друг к другу на величину а Тн, а именно прямые АБ, А|Б|, А2Б2, АзБз. Кроме того, для улучшения работы компаратора получают несколько реализаций неизвестной частоты ВГ, В|Г|, В2Г2, ВзГз, В4Г4, производят отвод ее нескольких отводов линии задержки. Причем, если задержка между отводами Д Тн, а их количество л, то соблюдают10А-Тн(п-1)5 аТн-(5)

Еще более высокую степень дробления периода Тн получают, когда из выбранной реализации /э получают с помощью линии задержки /( ее реализаций, сдвинутых между собой на б-Тн, причем соблюдают

б-Тн()(6)

где б - часть периода номинальной частоты, которая соответствует задержке между отводами третьей линии 41 задержки, т. е. в ко20 нечном итоге производится деление периода Тн на q(n-1Х - 1) частей.

По команде «Пуск устанавливается в «1 триггер 7 временного интервала и удерживается в этом состоянии, пока единичный потенциал не пройдет через первый элемент 8

задержки и не сбросит триггер 7 временного интервала в «О. На это время открывается второй элемент И 9, который пропускает сигнал неизвестной частоты /i на первую 12 и вторую 13 линии задержки. После сброса

OQ триггера 7 временного интервала в «О открывается третий элемент И 10, который замыкает выход первой линии 12 задержки на ее вход, т. е. обеспечивается рециркуляция измеряемого сигнала. Отводы первой линии 12 задержки заведены на информа г ционные входы регистра 19 анализа, на его синхронизирующий вход заведен выход управляемого генератора 1. В триггеры регистра 19 анализа записывается «1, если /,, взятая с отвода первой линии 12 задержки, своим передним фронтом опережает перед40 НИИ фронт частоты генератора 1, и «О, если отстает. Выходы регистра 19 анализа заведены на входы схемы 20 суммирования по модулям два, с которых снимается сигнал «I, если соседние триггеры регистра 19 анализа

с находятся в разных состояниях.

Таким образом регистр 19 анализа анализирует частоты входного 1 сигнала и управляемого генератора 1 и находит реализацию частоты /э, находящуюся между реализациями входного сигнала, взятыми с отво50 Дов первой линии 12 задержки, например, реализация /э А2Б2, находящаяся между реализациями /л Б|Г| и Б2Г2 (фиг. 5). Поиск и запоминание реализации частоты /з начинается с момента, соответствующего началу рециркуляции измеряемого сигнала /.j,

55 для чего первый период измеряемого сигнала с выхода первой линии 12 задержки устанавливается в «Ь, первый триггер 14 управления, выходной сигнал которого дифференцируется вторым формирователем 18 и устанавливает в «1 второй триггер 15 управления, который открывает четвертый элемент И 21 по третьему входу, на второй вход четвертого элемента И 21 подается инвертированная частота управляемого генератора 1, что обеспечивает срабатывание четвертого элемента И 21 с задержкой на половину периода генератора.

Первый вход четвертого элемента И 21 соединен с последней схемой 20.п суммирования по модулю два, на входы которой поступают выходные сигналы с первого и последнего триггеров регистра 19 анализа. Если эти триггеры находятся в противоположных состояниях, то единичный потенциал с выхода последней схемы 20.п суммирования по модулю два проходит через четвертый элемент И 21 и дает разрешение на запись в регистр 24 выбора задержки номера выбранного отвода первой линии 12 задержки со схемы суммирования, разрешает запись в регистр 4 фазы номера реализации и сбрасывает второй триггер 15 управления, тем самым запрещает четвертый элемент И 21 по третьему входу.

Счетчик 3 просчитывает (нумерует) каждый период управляемого генератора 1, фаза которого перемещается от О до Тн и имеет столько состояний, сколько принято реализацией частоты (на фиг. 5 изменение фазы соответствует прямым ДЕ, Д1Е1, Д2Е2 и т. д.).

По сигналу с четвертого элемента И 21, соответствующему выбору реализации, состояние счетчика 3 переписывается в регистр 4 фазы и поступает на блок 5 сравнения, на другие входы которого поступают значения со счетчика 3. При совпадении кодов счетчика 3 и регистра 4 фазы выбирается необходимая реализация частоты /э А2Б2 между В|Г| и В2Г2 (фиг. 5). Выбранная реализация частоты /; через первый элемент И 6 подается на третью линию 44 задержки, где достигают более высокую степень дробления периода Ти, т. е. из выбранной реализации А2Б2 получают на третьей линии 44 задержки К ее реализаций, сдвинутых между собой на б-Тн (фиг. 5). Выходной сигнал с регистра 24 выбора задержки, соответствующий паре отводов первой линии 12 задержки, поступает на первый вход одного из элементов И 29 блока 28 коммутации, на вторые входы поступает частота fx с отводов первой линии 12 задержки. Таким образом блок 28 коммутации дает на вход компараторов 32 и 33 частот реализацию частоты / с выбранных отводов первой линии 12 задержки (фиг. 5 BiFi, В2Г2). На вторые входы компараторов 32 и 33 частот подаются К реализаций частоты f-i, снимаемых с отводов третьей линии 44 задержки. На третий и четвертый вход компараторов 32 и 33 частот поступают сигналы с третьего 45 и четвертого 46 элементов задержки, которые сбрасывают соответственно

второй регистр 71 и второй триггер 74 «Меньше. На пятый вход компараторов 32 и 33 частот поступает сигнал с второго формирователя 18. В процессе измерения может быть г несколько случаев сравнения входной частоты /д; и fy.

Первый случай соответствует начальному моменту, когда отличие fx от /э значительное. В этом случае выбирается вторая реализация частоты /э А2Б2 (фиг. 5) и частота вход- ного сигнала / BiFi и В2Г2 (фиг. 5).

Как видно из фиг. 5, реализация /ч, соответствующая прямой А2Б2, не пересекает реализации входного сигнала / В|Г| и В2Г9 с момента их выбора, следовательно, ком5 параторы частоты не сработают. Таким образом, номиналы частот входной fx, снимаемой с выбранных отводов первой линии 12 задержки и В|Г| и В2Г2 (фиг. 5), и эталонной э, выбранной в соответствии с входной часQ тотой, настолько далеки, что за время сравнения произойдет смещение частоты /- и регистр 19 анализа запищет новое состояние фаз сигналов, соответствующих следующим отводам первой линии 12 задержки, анализ которых на схемах 20 суммирования по моду5 лю два дает результат, отличный от записанного в регистре 24 выбора задержки (реализация fx ВзГз, фиг. 5), который поступает на первый кодер 25, который анализирует перемещение единицы в коде регистров 24 и 19 и выдает сигнал «, что соот0 ветствует для случая А2Б2 .

Этот потенциал спустя длительность сигнала управляемого генератора 1 запишется в первый триггер 26 «Больше и через второй элемент ИЛИ 34 поступит на пятый

5 элемент И 37 и информационный вход регистра 40 результата. На пятом элементе И 37 этот потенциал опрашивается в конце рециркуляции сигналом с первого формирователя 17, так как задержка второго элемента 16 задержки примерно равна циклу ре0 циркуляции,этим же сигналом сбрасывается первый триггер 14 управления до нового цикла рециркуляции. Сигнал с выхода пятого элемента И 37, пройдя через четвертый элемент ИЛИ 36, сдвигает на один разряд

с регистр 39 циклов и записывает «1 в стар- 1ПИЙ разряд регистра 40 результата. Выходы регистра 40 результата и регистра 39 циклов поступают на декодер 41 для формирования управляющего потенциала, который, пройдя через формирователь 42 уровня, перестраи0 вает управляемый генератор 1 через управ- .ляющий элемент 2 на реализацию следую- пд,ей частоты. Во втором цикле работы, когда в регистре 40 результата находится «1, на седьмом элементе И 50 декодера 41 происходит совпадение потенциалов на входе,

5 выходной потенциал этого элемента «3/4 через формирователь 42 уровня и управляющий элемент 2 перенастраивает управляемый генератор 1 на реализацию частоты

(, соответствующей 3/4 диапазона.

Во втором цикле работа устройства происходит аналогично описанной, только реализация /э представлена БЖ, Б1Ж1, БдЖа, БзЖз (фиг. 5), а реализация / в процессе рециркуляции ЗИ, 3|Hi, 32И2, ЗзИз, 34И4 (фиг. 5). В данном случае выбранными будут реализации /э - Б|Ж1 и / - ЗИ и 3iH|. Реализация /э пересекает нижнюю реализа- цию fx - ЗИ (фиг. 5), значит сработает второй компаратор 33 частот, который выдает потенциал « , что означает или , значит на втором шаге в регистр 40 результата запишется «О и код двоичного эквивалента в двух старших разрядах будет 10.

В третьем цикле первый декодер 48 декодера 41 выработает потенциал на выходе 10, значит сработает одиннадцатый элемент И 54 и выдает потенциал 5/8, который пере- страивает управляемый генератор 1 на реали- зацию fg f + -f-д fn , соответствующую 5/8 диапазона. В этом случае реализации Гдесть Ж|Кь ЖгКа, ЖзКз, ЖК. Выбранными будут реализация /э - ЖзКз и / - Л2М2 и ЛзМз. Реализации /э пересекают верхнюю реализа- цию fx - ЛзМз, значит сработает первый компаратор 32 частот, который выдает потенциал , т. е. или /э /дг, значит в третий разряд результата запишется «1 и трехразрядный код результата будет иметь вид 101.

Дальнейшая работа устройства продолжается так же до последнего цикла, в этот момент регистр 40 результата выдается на выход устройства через блок 43 элементов И на этом измерение заканчивается.

Формула изобретения

1. Устройство для измерения отклонения частоты от номинального значения, содержащее счетчик и первый, второй и третий элементы И, отличаюш,ееся тем, что, с целью увеличения диапазона преобразуемых частот, в него введены четвертый, пятый и шестой элементы И, управляемый генератор, управляющий элемент, триггер временного интервала, первый, второй, третий и четвертый элементы задержки, регистр фазы, блок сравнения, первая, вторая и третья линии задержки, первый элемент ИЛИ, первый и второй триггеры управления, первый и второй формирователи, регистр анализа, п схем суммирования по модулю два, первый и второй инверторы, регистр выбора задержки, первый кодер, первый триггер «Больше, первый триггер «Меньше блок коммутации, содержащий п элементов И, второй и третий элементы ИЛИ, первый и второй компараторы частот, четвертый, пятый и шестой эле- менты ИЛИ, регистр циклов, регистр результата, декодер, формирователь уровня, блок р элементов И, вход «Пуск, соединенный

5 .JQ 15

25 30

5

5

0

5

0

с входом сброса регистра результата, входом установки регистра циклов и входом установки триггера временного интервала, выход которого соединен с первым входом второго элемента И, и входом первого элемента задержки, выход которого соединен с входом сброса триггера временного интервала, инверсный выход которого соединен с первым входом второго элемента И, второй вход которого соединен с выходом второй линии задержки, а выхо.д. - с вторым входом первого элемента ИЛИ, первый вход которого соединен с выходом второго элемента И, второй вход которого является входом устройства, выход первого элемента ИЛИ соединен через первую линию задержки с входом второй линии задержки и входом установки первого триггера управления, выход которого через последовательно соединенные -второй элемент задержки и первый формирователь соединен с входом сброса первого триггера управления и вторыми входами пятого и шестого элементов И, а через второй формирователь - с пятыми входами первого и второго компараторов частот, входами сброса первого триггера «Больше и первого триггера «Меньше и установочным входом второго триггера управления, вход сброса которого соединен с тактовыми входами регистра фазы и регистра выбора задержки, а также с выходом четвертого элемента И, выход второго триггера управления соединен с третьим входом четвертого элемента И, второй вход которого соединен с выходом первого инвертора, вход которого соединен с тактовыми входами счетчика и регистра анализа, вторым входом первого элемента И и выходом управляемого генератора, вход которого соединен с выходом управляющего элемента, вход которого соединен с выходом формирователя уровня, входы которого соединены с соответствующими выходами декодера, входы первой группы входов которого соединены соответственно с первыми входами элементов И блока элементов И и соответствующими выходами регистра результата, входы второй группы входов декодера соединены с соответствующими выходами регистра циклов, выход которого, соответствующий старшему разряду, соединен с вторыми входами элементов И, входящих в состав блока элементов И, и является одним из выходов устройства совместно с выходами элементов И блока элементов И, п отводов первой линии задержки соединены с соответствующими информационными входами регистра анализа и вторыми входами соответствующих элементов И, входящих в блок коммутации, первые входы которых попарно объединены и соединены с соответствующими входами первой группы входов первого кодера и выходами регистра выбора задержки, информационные входы которого соединены с соответствующими выходами схем суммирования по модулю

два н входами второй группы входов первого кодера, выходы «Больше и «Меньше которого соединены соответствеино с информационными входами первого триггера «Больше и первого триггера «Меньше, выходы которых соединены соответственно с третьим входом четвертого элемента и вторым входом пятого элемента ИЛИ, выход которого соединен с первым входом шестого элемента И, выход которого соединен с вторым входом шестого элемента ИЛИ, выход которого соединен с тактовыми входами регистра циклов и регистра результата, информационный вход которого соединен с выходом четвертого элемента ИЛИ и первым входом пятого элемента И, выход которого соединен с первым входом шестого элемента ИЛИ, выходы счетчика соединены соответственно с входами второй группы входов блока сравнения и информационными входами регистра фазы, выходы которого соединены соответственно с входами первой группы входов блока сравнения, выход которого соединен с первым входом первого элемента И, выход которого через второй инвертор соединен с тактовыми входами первого триггера «Больше и первого триггера «Меньше а непосредственно - с входом третьей линии задержки, /С отводов которой соединены с входами вторых групп входов первого и второго компараторов частот, а выход через третий элемент задержки - с третьими входами первого и второго компараторов частот а через третий и четвертый элементы задержки - с четвертыми входами первого и второго компараторов частот, первые входы которых соединены соответственно с выходами второго и третьего элементов ИЛИ, входящих в состав блока коммутации, выходы второго элемента ИЛИ соединены соответственно с выходами нечетных элементов И, входяш,их в состав блока коммутации, а выходы четных элементов - с входами третьего элемента ИЛИ, при этом первые выходы первого и второго компараторов частот соединены соответственно с первым и вторым входами четвертого элемента ИЛИ. а вторые выходы - с первым и третьим входами пятого элемента ИЛИ, выход младшего разряда регистра анализа соединен с первым входом первой из схем суммирования по модулю два и с вторым входом последней п-схемы из схем суммирования по модулю два, выход которой соединен с первым входом четвертого элемента И, остальные выходы разрядов регистра анализа соединены следующим образом, выход второго разряда соединен с вторым входом первой схемы из схем суммирования по модулю два и первым входом второй схемы из схем суммирования по модулю два, выход третьего разряда - с вторым входом второй и первым входом третьей схемы из схем суммирования по модулю два и т. д., старший разряд регистра анализа соединен с вторым входом

0

0

5

предпоследней и первым входом последней из схем суммирования по модулю два.

2.Устройство по п. 1, отличающееся тем, что декодер содержит элемент НЕ, первый и второй декодеры, седьмой-двадцатый элементы И, первым входом первой группы декодера является вход элемента НЕ, соединенный с входами А первого и второго декодеров и первым входом восьмого элемента И, второй вход которого является вторым вхОхЦОм второй группы входов декодера и соединен с вторым входом седьмого элемента И, первый вход которого соединен с выходом элемента НЕ, вторым входом первой группы входов декодера являются соединенные между собой входы В первого и второго декодеров, а третьим входом - вход С второго декодера, первый вход второй группы входов декодера является его первым выходом, а вторым - пятнадцатым выходами - соответственно выходы седьмого-двадцатого элементов И, третьим входом второй группы входов декодера являются вторые входы девятого-двенадцатого элементов И, первые входы которых соединены с соответствующими выходами первого декодера, четвертым входом второй группы входов декодера являются вторые входы тринадцатого-двадцатого элементов И, первые входы которых соединены с соответ- ствуюш.ими выходами второго декодера.

3.Устройство по п. 1, отличающееся тем, что формирователь уровня содержит пятнадцать усилителей, пятнадцать первых диодов, пятнадцать делителей напряжения, пятнадцать вторых диодов, резистор и повторитель, из входящих в формирователь уровня элементов составлено пятнадцать цепочек каждая из которых состоит из уси.тителя, вход которого является одним из входов формирователя уровня, выход усилителя через обратно включенный первый диод .ч делитель напряжения соединен с анодом второго диода, причем катоды всех пятнадцати вторых диодов каждой цепочки соединены через резистор с общей шиной, а через повторитель - с выходом формирователя уровня.

0

5

0

4. Устройство по п. 1, отличающееся тем, что компаратор частот содержит первый и второй регистры, второй кодер, второй триггер «Больше и второй триггер «Меньше, первым входом компаратора частот являются соединенные между собой информационные входы первого регистра, второй группой входов - соответствующие тактовые входы первого регистра, выходы которого соединены с соответствующими информационными входами второго регистра и соответствующими входами второй группы

входов второго кодера, входы первой группы входов которого соединены с соответствующими выходами второго регистра, тактовые входы которого соединены между собой и

являются четвертым входом компаратора частот, третьим входом которого являются соединенные между собой тактовые входы второго триггера «Больше и второго триггера «Меньше, входы сброса которых соединены между собой и являются пятым входом

Й/г.2

компаратора частот, а выходы - соответственно первым и вторым выходами компаратора частот, при этом информационные входы вторых триггеров «Больше и «Меньше соединены соответственно с первым и вторым выходами второго кодера.

Фиг:}

uj ;

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения отклонения частоты от номинального значения | 1984 |

|

SU1357863A1 |

| Цифровой частотный демодулятор | 1984 |

|

SU1298845A1 |

| Контролируемый пункт системы телемеханики | 1988 |

|

SU1524080A1 |

| Дельта-кодек | 1989 |

|

SU1725398A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ УГЛА | 1996 |

|

RU2115229C1 |

| Устройство передачи и приема информации | 1991 |

|

SU1793454A1 |

| УСТРОЙСТВО КОДИРОВАНИЯ, ПРИЕМА И ПЕРЕДАЧИ ЦИФРОВОЙ ИНФОРМАЦИИ ПО ДВУХПРОВОДНОЙ ЛИНИИ СВЯЗИ | 1996 |

|

RU2115240C1 |

| Контролируемый пункт системы телемеханики | 1985 |

|

SU1345230A1 |

| Способ маркирования информационных комбинаций в системах последовательной записи с двухчастотным кодированием и устройства записи и воспроизведения для его осуществления | 1987 |

|

SU1543445A1 |

| Цифровая телеметрическая система для морских сейсмических исследований | 1982 |

|

SU1037317A1 |

Изобретение может быть использовано при разработке устройств для приема и обработки сигнала. Цель изобретения - увеличение диапазона преобразуемых частот. Устройство содержит счетчик 3 и элементы И 6, 9 и 10. В устройство введены управляемый генератор 1, управляющий элемент 2, регистр 4 фазы, блок 5 сравнения, триггер 7 временного интервала, элементы 8, 16, 45 и 46 задержки, элементы ИЛИ 11, 34-36, 1инии 12, 13 и 44 задержки, триггеры 14 и 15 управления, формирователи 17 и 18, регистр 19 анализа, схемы 20.1-20.jV суммирования по модулю два, элементы И 21, 37 и 38, инверторы 22 и 23, регистр 24 выбора задержки, кодер 25, триггер 26 «Больше, триггер 27 «Меньше, блок 28 коммутации, компараторы 32 и 33 частот, регистр 39 циклов, регистр 40 результата, декодер 41, формирователь 42 уровня и блоки 43.1-43.Я элементов И и образованы новые функциональные связи. В описании приведены схемы декодера 41, формирователя 42 уровня и компараторов 32 и 33 частот. 3 з. п. ф-лы, 7 ил. сл 00 IND ьо 4 СЛ быдоча резу/ отата SroiT

| Устройство для измерения временных интервалов | 1982 |

|

SU1034009A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| ПРЕОБРАЗОВАТЕЛЬ «ЧАСТОТА-КОД» | 0 |

|

SU300133A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-07-07—Публикация

1984-02-03—Подача