Изобретение относится к вычислительрой технике.

Известен аналого-цифровой преобразователь поразрядного уравновешивания, содержащий блок сравнения, выход которого соединен со входом запоминающего ре-, гистра, к п другим входам которого под- соединены п выходов . сдвигового регистра, п выходов запоминающего регистра соединены с п входами параллельного цифроаналоговогопреобразователя на основе резистивной матрицы R-2R, выход которого Q соединен с одним из двух входов блока сравнения, к второму входу которого подключен геиератор входного сигнала (1.

Недостатком является большое количество логических элементов.

Известен аналого-цифровой преобразо- is ватель, содержащий блок сравнения, выход которого соединен со входом блока управления, выход блока управления соединен с одним из входов блока коммутации, к другому входу которого подсоединен ге-. нератрр эталонных сигналов, два выхода 20 блока коммутации соединены со входами двух блоков хранения разрядов, выходы которыхподсоединены ко входам блока сравнения, генератор входного сигнала подклю. чей к одному из блоков хранения зарядов 2.

Недостатком устройства является низ кая точность преобразования. . Цель изобретения - повышение точ-, . ности преобразования.

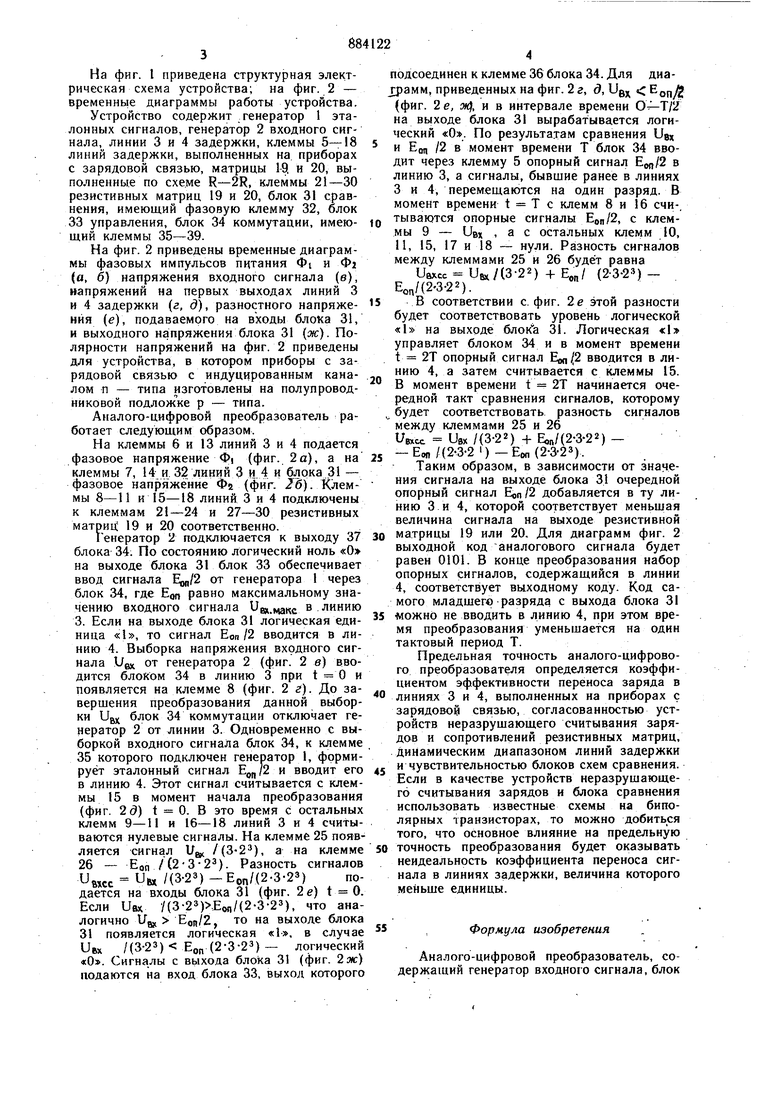

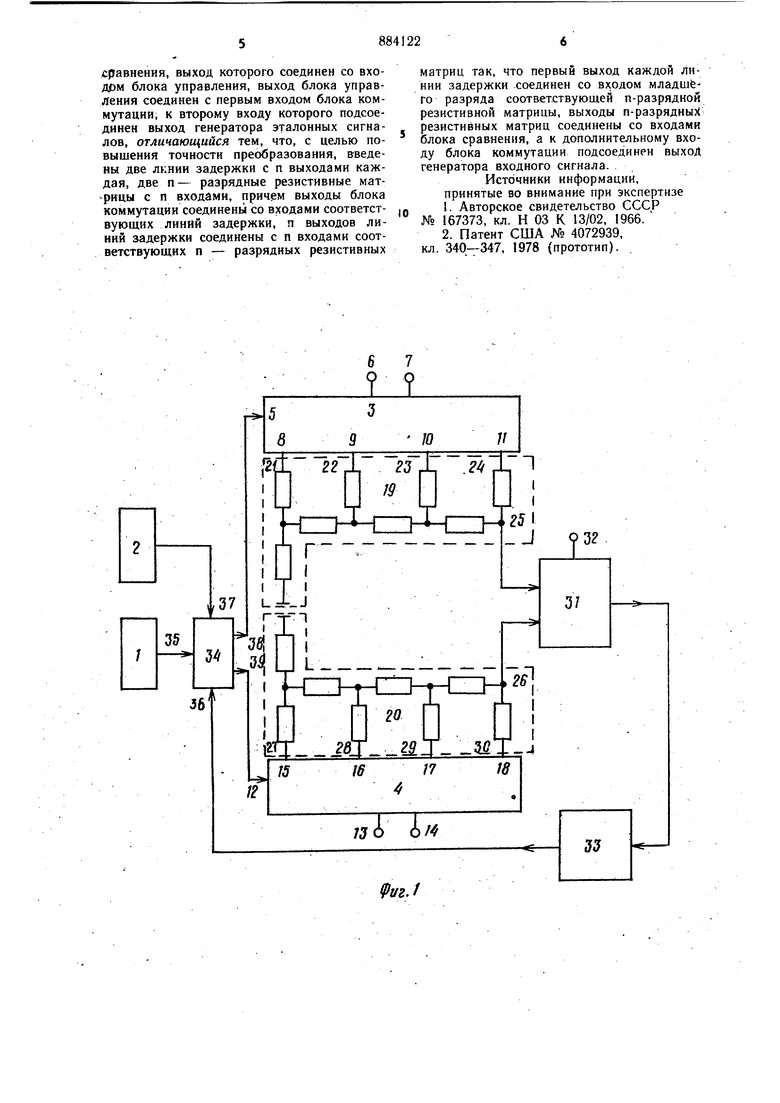

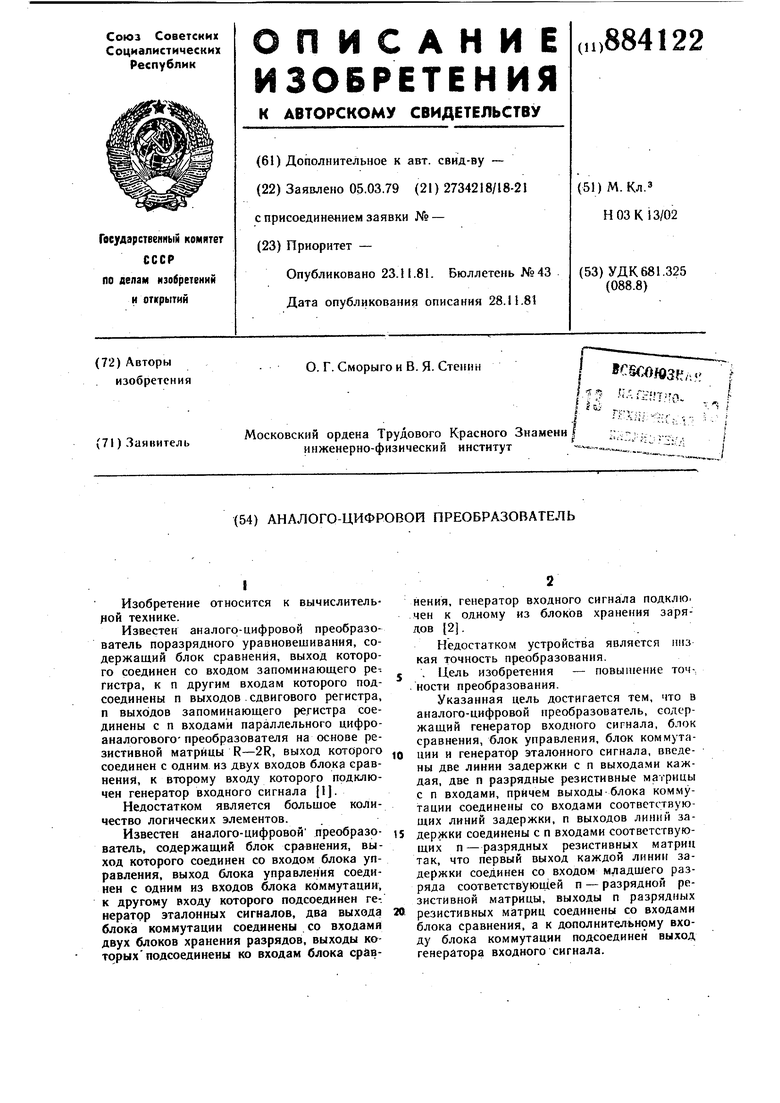

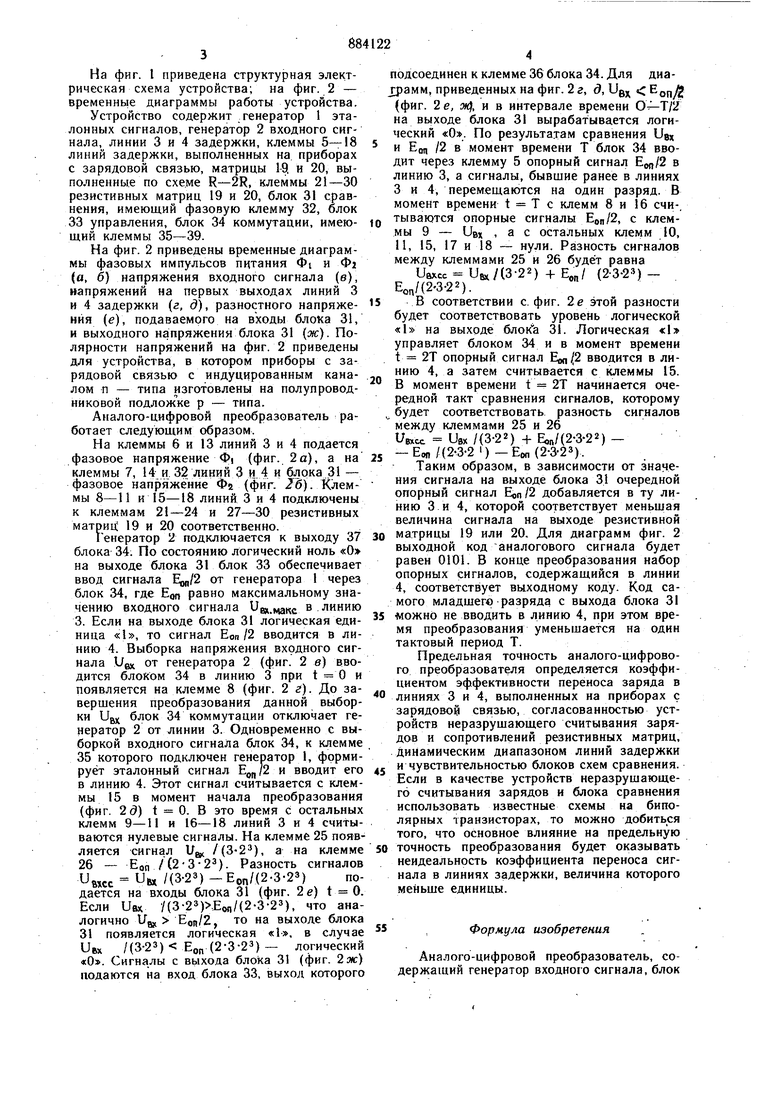

Указанная цель достигается тем, что в аналого-цифровой преобразователь, содержащий генератор входного сигнала, блок сравнения, блок управления, блок коммутации и генератор эталонного сигнала, введены две линии задержки с п выходами каждая, две п разрядные резистивные матрицы с п входами, причем выходы-блока коммутации соединены со входами соответствующих линий задержки, п выходов линий задержки соединены с п входами соответствующих п-разрядных резистивных матриц так, что первый выход каждой линии задержки соединен со входом младшего разряда соответствуюцХей п - разрядной резистивной матрицы, выходы п разрядных резистивных матриц соединены со входами блока сравнения, а к дополнительн9му входу блока коммутации подсоединен выход генератора входного сигнала. На фиг. 1 приведена структурная электрическая схема устройства; на фиг. 2 - временные диаграммы работы устройства. Устройство содержит генератор 1 эталонных сигналов, генератор 2 входного сигнала, линии 3 и 4 задержки, клеммы 5-18 линий задержки, выполненных на приборах с зарядовой связью, матрицы 19. и 20, Lполненные по схеме R-2R, клеммы 21-30 резистивных матриц 19 и 20, блок 31 сравнения, имеющий фазовую клемму 32, блок 33 управления, блок 34 коммутации, имею- ю щий клеммы 35-39. На фиг. 2 приведены временные диаграммы фазовых импульсов питания Ф1 и Ф1 (а, б) напряжения входного сигнала (в), напряжений на первых выходах линий 3 и 4 задержки (г, д), разностного напряженйя (е), подаваемого на входы блока 31, и выходного напряжения блока 31 (ж). Полярности напряжений на фиг. 2 приведены для устройства, в котором приборы с зарядовой связью с индуцированным кана- , лом п - типа изготовлены на полупроводполупроводниковой подложке р - типа. Аналого-цифровой преобразователь работает следующим образом. На клеммы 6 и 13 линий 3 и 4 подается фазовое напряжение Ф| (фиг. 2а), а на 2 клеммы 7, 14 и. 32 линий 3 и 4 и блока 31 - фазовое напр1яжёние Фг (фиг. J6). Клеммы 8-11 и линий 3 и 4 подключены к клеммам и 27-30 резистивных MaTDHii 19 и 20 соответственно. Генератор 2 подключается к выходу 37 блока 34. По состоянию логический ноль «О на выходе блока 31 блок 33 обеспечивает ввод сигнала Е„/2 от генератора 1 через блок 34, где ЕоГравно максимальному значению входного сигнала UB, в линию 3. Если на выходе блока 31 ловчеекая единица «I, то сигнал Ео„/2 вводится в линию 4. Выборка напряжения входного сигнала Ugji от генератора 2 (фиг. 2 в) вводится блоком 34 в линию 3 при t О и .и,Г11.71 JT D tJirin rilX/ J I ILT-ri,I. VJ ri появляется на клемме 8 (фиг. 2 г). До завершения преобразования данной выборки и, блок 34 коммутации отключает генератор 2 от линии 3 Одновременно с выборкой входного сигнала блок 34, к клемме 35 которого подключен генератор 1, формируёт эталонный сигнал и вводит его в линию 4. Этот сигнал считывается с клеммы 15 в момент начала преобразования (фиг. 2д) t 0. В это время с остальных клемм 9-11 и 16-18 линий 3 и 4 считываются нулевые сигналы. На клемме 25 появляется сигнал (3-23), а на клемме 26 - ЕОП /(2-3-23). Разность сигналов и Ute /(3-2)Eon/(2 3-2) подае тся на входы блока 31 (фиг. 2е) t 0. Если Uax /(3-23).Еоя/(2-3-23), что аналогично Ugji Еоп/2, то на выходе блока 31 появляется логическая «1, в случае Ubx /(3-23) ЕОП (2-3-23) - логический «О. Сигналы с выхода блока 31 (фиг. 2ж) подаются на вход блока 33, выход которого одсоединен к клемме 36 блока 34. Для диаpaMM, приведенных на фиг. 2 г, д, Ugj EQJ,/j (фиг. 2 е, 3«J, и в интервале времени на выходе блока 31 вырабатывается логический «О. По результатам сравнения UBX „ F /9 в момент воемени Тблок пво и Ьщ, // в момент времени 1 олок J4 через клемму 5 опорный сигнал в линию 3, а сигналы, бывшие ранее в линиях 3 и 4, перемещаются на один разряд. В момент времени t Т с клемм 8 и 16 счи-. тыкаются опорные сигналы ЕО„/2, с клеммы 9 - UBX , а с остальных клемм 10, - нули. Разность сигналов между клеммами 25 и 26 будет равна Uaxcc UBX/(3-22) + ЕОП/ (2-3-2) Eon/{2-3-22). В соответствии с. фиг. 2е этой разности будет соответствовать уровень логической «1 на выходе 31. Логическая «1 управляет блоком 34 и в момент времени t 2Т опорный сигнал вводится в ли затем считывается с клеммы 15. В момент времени t 2Т начинается очередной такт сравнения сигналов, которому будет соответствовать разность сигналов между клеммами 25 и 26 UBXCC Uex /(3-22) + Ei,n/(2-3-22) - Eon/{2-3-2)-Eon (2-3-23). Таким образом, в зависимости от значения сигнала на выходе блока 31 очередной опорный сигнал ЕОП /2 добавляется в ту линию 3 и 4, которой соответствует меньшая величина сигнала на выходе резистивнои матрицы 19 или 20. Для диаграмм фиг. 2 выходной код аналогового сигнала будет 0101. В конце преобразования набор опорных сигналов, содержащийся в линии соответствует выходному коду. Код младшего разряда с выхода блока 31 «ожнб не вводить в линию 4, при этом вре« преобразования уменьшается на один тактовый период Т. Предельная точность аналого-цифрового преобразователя определяется коэффиЦиентом эффективности переноса заряда в « 1 линиях 3 и 4, выполненных на приборах с зарядовой связью, согласованностью устР иств неразрушающего считывания заря « сопротивлении резистивных матриц, Динамическим диапазоном линии задержки и чувствительностью блоков схем сравнения, Если в качестве устройств неразрушающе -- v.-rnn.Tn „РП.,П«,ПЯ,П.„Рг6 считывания зарядов и блока сравнения использовать известиые схемы на биполярных транзисторах, то можно добиться того, что основное влняние на предельную точность преобразования будет оказывать неидеальность коэффициента переноса сигнала в линиях задержки, величина которого меньше единицы. , Формула изобретения . ., . Аналого-цифровой преобразователь, содержащий генератор входного сигнала, блок

сравнения, выход которого соединен со входрм блока управления, выход блока управления соединен с первым входом блока коммутации, к второму входу которого подсоединен выход генератора эталонных сигналов, отличающийся тем, что, с целью повышения точности преобразования, введены две линии задержки с п выходами каждая, две п - разрядные резистивные матфицы с п входами, причем выходы блока коммутации соединены со входами соответствующих линий задержки, п выходов линий задержки соединены с п входами соответствующих п - разрядных резистивных

матриц так, что первый выход каждой линии задержки .соединен со входом младше го разряда соответствующей п-разрядной резистивной матрицы, выходы п-разрядных резистивных матриц соединены со входами блока сравнения, а к дополнительному входу блока коммутации подсоединен выхоД генератора входного сигнала.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 167373, кл. Н 03 К 13/02, 1966.

2.Патент США № 4072939, кл. 340-347, 1978 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1979 |

|

SU809555A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ С САМОКОНТРОЛЕМ | 2010 |

|

RU2431233C1 |

| Аналого-цифровой преобразователь | 1990 |

|

SU1720160A1 |

| ДВУХКАНАЛЬНЫЙ РЕЗЕРВИРОВАННЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2003 |

|

RU2251209C2 |

| Последовательно-параллельный аналого-цифровой преобразователь | 1989 |

|

SU1676100A1 |

| Аналого-цифровой преобразователь | 1979 |

|

SU809556A1 |

| ЦИФРО-АНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ | 2013 |

|

RU2546557C2 |

| УСТЮЙСТВО ДЛЯ СОПРЯЖЕНИЯ АНАЛОГОВОЙ И ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНОЙ АППАРАТУРЫ | 1979 |

|

SU826559A1 |

| Следящий аналого-цифровой преобразователь | 1975 |

|

SU546099A1 |

| Устройство для кодирования звуковых сигналов с инерционным компандированием | 1985 |

|

SU1356233A1 |

37

35

5

ЗЬ

б 7

1

7J6 6/

l/8,f

Авторы

Даты

1981-11-23—Публикация

1979-03-05—Подача