(54) АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1979 |

|

SU809556A1 |

| Аналого-цифровой преобразователь | 1979 |

|

SU884122A1 |

| Аналого-цифровой преобразователь | 1980 |

|

SU1112549A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1277396A1 |

| СПОСОБ КОГЕРЕНТНОГО НАКОПЛЕНИЯ РАДИОИМПУЛЬСОВ | 2003 |

|

RU2293347C2 |

| УСТРОЙСТВО СЧИТЫВАНИЯ С ВРЕМЕННОЙ ЗАДЕРЖКОЙ И НАКОПЛЕНИЕМ СИГНАЛОВ С МНОГОЭЛЕМЕНТНЫХ ФОТОПРИЕМНИКОВ ИНФРАКРАСНОГО ИЗЛУЧЕНИЯ | 2012 |

|

RU2498456C1 |

| Многоканальный преобразователь угла поворота вала в код | 1980 |

|

SU947895A1 |

| Асинхронный аналого-цифровой преобразователь | 1976 |

|

SU616711A1 |

| Дискретно-аналоговое устройство задержки | 1979 |

|

SU879758A1 |

| Устройство для контроля аналоговых объектов | 1986 |

|

SU1397941A1 |

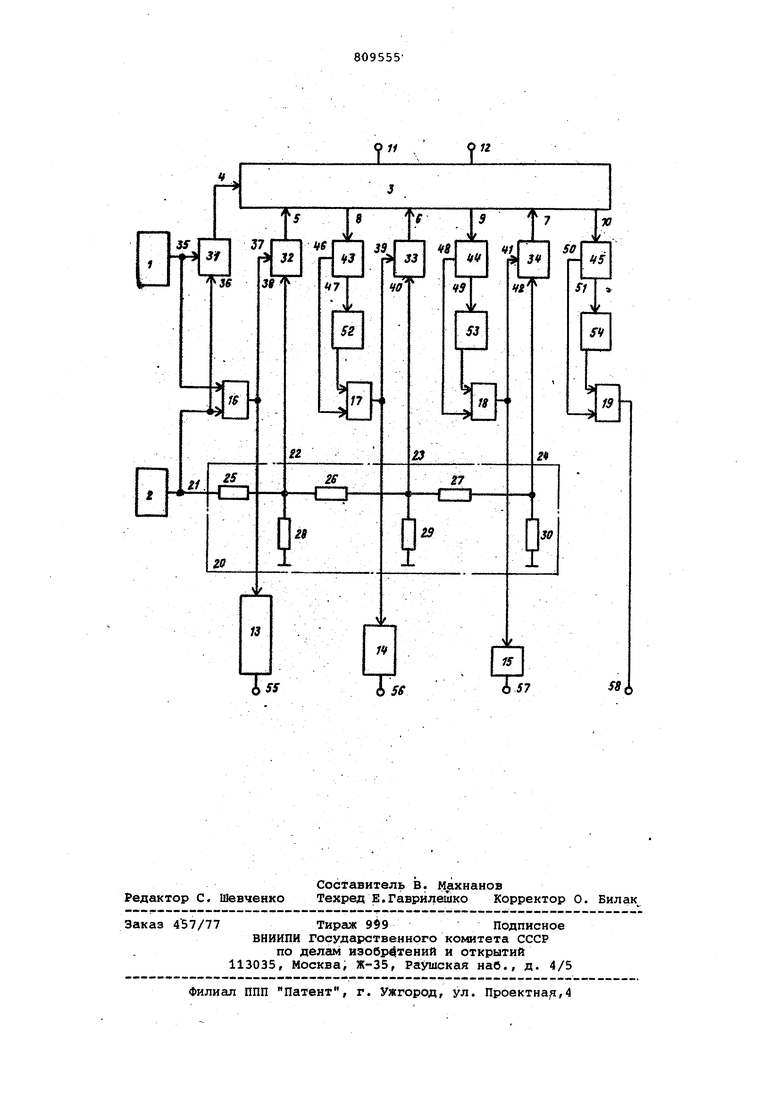

к первому входуэлемента сравнения старшего разряда которого подключен выход источника входного сигнала, ко второму входу - источник эталонного напряжения, выходы элементов сравнения, кроме младшего разряда, соединены со входами п-1 сдвиговых регистров, введены резистйвная матрица R-2R на п-1 разряд, пдвухвходовых устройств ком- цутацки, п-1 Двухвыходовых устройств 1«)ммутации, п-1 устройств аналогового храгГения, а линия задержки содержит п-1 дополнительных входов, причем к первому входу первого двухвходового устройства коммутации подклю-: чен источник входного сигнала, ковторому вixoдy - источник эталонного напряжения, к выходу - первый вход линии задержки, п-1 выходов которой соединены со входами п-1 двухвыходовах устройств комму1гации, у каждого из которых первый выход через соответствующее устройство аналогового хранения, а второй выход - непосредственно соединены со входш соответствующего элемента сравнения данного разряда., выходы элементов сравнения, кроме элемента сравнения младшего разряда, соединены с первыми входами соответствующих им двухвходовых устройств коммутации, выходы которых соединены с п-1 входами линии задержки, йстрчник эталонного напряжения подключен ко входу резистивной матрицы R-2R, п-1выходы которой собдийены со вторыми входами п-1 двухвходовых устройств коммутации, . -На чертеже изображена блок-схема аналого-цифрового преобразователя на четыре двоичных разряда.

Преобразователь содвЕжит источник 3. входного сигнала, источник 2 эталонного напряжения, линию 3 задерж- ; ки, имекяцую входы 4-7, выходы 8-10 я выводы для подключения двух фаз 11 В 12 импульснВго питания,,сдвигоSHte регистры 13-15, элементы 16-19 еравнения, резистивную матрицу 20, имеющую вход 21, выходы 22-24 и соевас ИУК) резисторы 25-30, двухвхоовые устройства 31-34 коммутации . со входами 35-42, двухвыходовые устойства 43-45 коммутации с зыхо-ами 46-51, устройства 52-54 анало-гового хранения. Выходом преобразо- являются выходы 55-57 сдви- . говых регистров 13-15 и выход 58 элемента 19 сравнения. В качестве линии задержки используется устройство, выполненное на приборах с зарядовой связью с двухфазным импульс НЬ1М питанием и леразрушающим считыванием передаваемых сигналов на боковых выходах.

Аналого-цифровой преобразователь работает следующим образом.

На вход 35 устройства 31 коммутации подается входной аналоговый

сигнал , от источника 1 входного сигнала, на вход 21 подается от источника 2 эталонного напряжения эталонное напряжение f равное поло- . вине максимального входного сигнала УЛ ЕЭТ При этом на

выходе 22 напряжение Ujj Еэт/2/ на выходе 23 напряжение Uja Еэт/4, на выходе 24 - Uj EjT/S- От источника 1 входного сигнала и источ|ника 2 эталонного напряжения выборка входного сигнала Ui,,(| и з талонный сигнал Еэ7 поочередно в линию 3 задержки по входу 4 с помощью двухвходового устройства 31 коммутации, образуя набор из двук аналоговых сигналов U-f,i ().Jbx-i Ubxt0) и ()Еэ7-/ где определяет начало отсчета времени с момента ввода выборки входного сигнала Т период ввода сигнала в линию 3 задерж. ки. , . : /

Затем в линию 3 задержки по входу 4 вводится следующий набор из двух сигналов: следующей выборки входного

.сигнала и to,-f-1-1 и Ьх эталонного сигнала Eg, т.е. Uf., ) U.. Ubx(t 2T) и (,i (t 3T) E,t

Так В линии 3 .задержки формируется И перемещается набор изДВУХ сигнаijiOB - выборки входного сигнала и эталонного сигнала. Процесс преоб-. разования выборки входного сигнала в двоичный код рассмотрим на примере выборки входного сигнала .().i Одновременно с вводом этой выборки входного сигнала в линию 3 задержки по входу 4 в момент времени , эта выбОрка сравнивается со значением эталонного сигнала .ЕЭТ элементом 16 сравнения. Результатом сравнения.является логический сигнал на его выходе равный или , являющийся значением старшего разряда кода преобразуемой выборки входного аналогового сигнала U{,xf Логический сигнал а поступает на вход регистра сдвига 13, выполняющего роль динамической памяти, и одновременно на вход 37 двухвходового устройства 32 коммутации. Значение логического сигнала а на выходе элемента 16 сравнения управляет двухвкодовым устройством 32 коммутации по входу 37 и обеспечивает добавление сигнала Ujj ЕЭТ/2 с выхода резистивной, матрицы 20 через двухвходовое устройство. 32 коммутации к меньшему из двух в наборе сигналов Uj, ()llui4 и lit,г ()Ез, перемещакнаихся в линии 3 задержки, например, если в результате сравнения и.4. Ufcx() Е эт f то после

;выборки логического сигнала на вы:ходе элемента 16 сравнения бу-.

дет осуществляться добавка к меньшему в наборе из двух сигналов, т.е. будет U ()UH (t T)Ubx{, а Щ ()E JT+ЕЗ|-/2 . Далее, при переносе набора из двух сравниваемы сигналов по линии 3 задержки первый из них в момент времени и,4 (t 2T)Uux считывается неразрущающим способом с линии 3 задержки и поступает на двухвыходовое устройство 43 коммутации и на устройст во 52 аналогового хранения, которым и запоминается. С выхрда устройства 52 аналогового хранения это сигнал поступает ка один из входов элемента 17 сравнения в момент . В следующий такт переноса сигналов по линии 3 задержки, т.е. при , второй из сигналов в рассматриваемом наборе Ufa ( U47 () E3T-t-Ej-f/2 считывается неразрушающим способом с выхода 8 и с выхода 46 устройства 43 коммута ции и поступает на второй вход элемента 17 сравнения. В результате сравнения сигналов из рассматриваемого набора ii ()U, и (1 ЗТ)Еэт+Езт/2 элемент 17 сравнения вырабатывает значение вта рого разряда двоичного кода а преобразуемой выборки и(,х4 аналогового сигнала. Пусть С ЕЭТ+ Еэт/2, тогда . Логический сигнал с выхода элемента 17 сравнения пост пает на вход сдвигового регистра 14 имеющего на один разряд меньше, чем сдвиговый регистр 13, в котором хра нится значение а . Одновременно сиг нсш с выхвда элемента 17 сравнения по входу 39 управляет двухвходовьш устройством 33 коммутацииi KOTopoe осуществляет добавку уравновешивающего сигнала к меньшему из сигналов в перемешающемся в лини 3 задержки наборе из двух сигналов и Ujj.B рассматриваемом примере Щ )Xи+г() и добавка U23 Ejr/4 осуществляется к первому сигналу в наборе, т.е. (t-3TjcU44a aT;f E3T/4Ub,f-t-EjiM ()«Eэт эГ/а. Аналогично происходит процесс фо мирования более младших разрядов кода аналогового сигнала и tr( ч сопровождающийся уравновешиванием двух сигналов в наборе U44 и 4Л г перемещающихся в линии 3 задержки. Процесс преобразования завершается выработкой на выходе 58 элемекта 19 сравнения значения млад шего разряда кода, а 1, синхронно с выработкой которого на выходах 55-5 СДВИГОВЫХ регистров появляются значения остальньЬс разрядов кода а , ff, Одновременно в аналого-цифровом преобразователе происходит уравяовешивание п (для рассматриваемого примера ) выборок входного сигнаla и, где ,2,3.... На выходах 55-58 через промежутки времени t«2T. появляются значения параллельного двоичного кода преобразуемых выборок входного сигнала. Формула изобретения. Аналого-цифровой преобразователь, содержащий источник входного сигнала, источник эталонного напряжения, линию задержки с н-1 выходами, где п - количество разрядов преобразователя, п-1 сдвиговых регистров, п элементов сравнения, и первому входу элемента сравнения старшего разряда которого подключен выход источника входного сигнала, ко второму входу - источник ЗТалонного напряжения, выЯода элементов сравнения, кроме младшего разряда, соединены со входами п-1 сдвиговых регистров, отличают и й-, с я тем, что, с целью повышения точности, в него введены резистивная матрица R-2R на п-1 разряд, п двухвходовых устройств коммутации, л-1 двухвыходовых устройств коммутации, п-1 устройств аналогового хранения, а линия задержки содержит п-1 допол-. нительнБк входов, причем к первому входу первого двухвходового устройства коммутации подключен источник входного сигнала, ко второму входу источник эталонного напряжения, к выходу - первый вход линии задержки, п-1 выходов которой соединены с входами п-1 двухвыходовых устройств коммутации, у каждого из которых первый выход через соответствующее устройство аналогового хранения, а второй выход - непосредственно соединены, со входами соответствующе- го элемента сравнен ия данного разряда, BBKOfi элементов сравнения, кроме элемента сравнения младдаего разр5ща, соединены с первыми входами соответствующих им двухвходовых устройств коммутации, вьвгоды которых соединены с п-1 входаьш линии задержки, источник эталонного напряжения подключен ко входу резистнвной матрицы R-2R, .п-1 выходы которой соединены со вторыми входами п-1 двухвкодовьог устройств -коммутации. Источники информации, принятые во внимание при экспертизе . 1. Балакай В.Г. и др. Интеграль- ные схемы АЦП и ЦАП. Энергия, 1978, с. 55. 2.Electronic Design 1969, 1, с. 101-102 (прототип).

6

Г

5

Авторы

Даты

1981-02-28—Публикация

1979-04-16—Подача