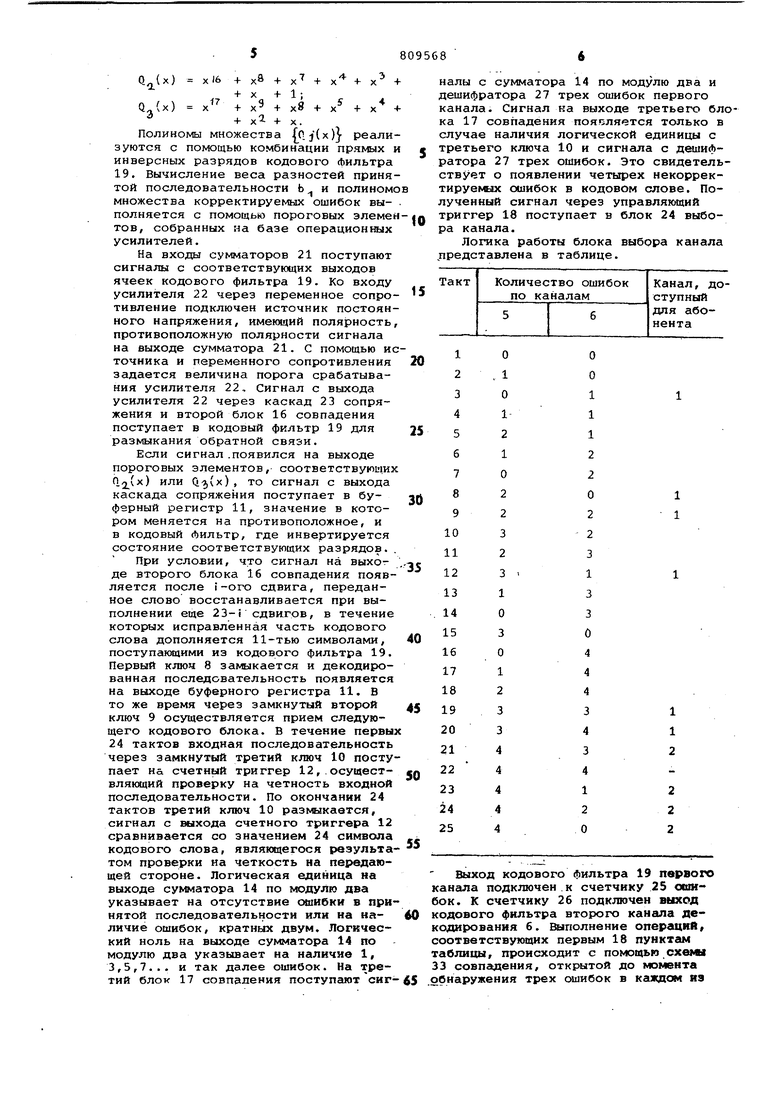

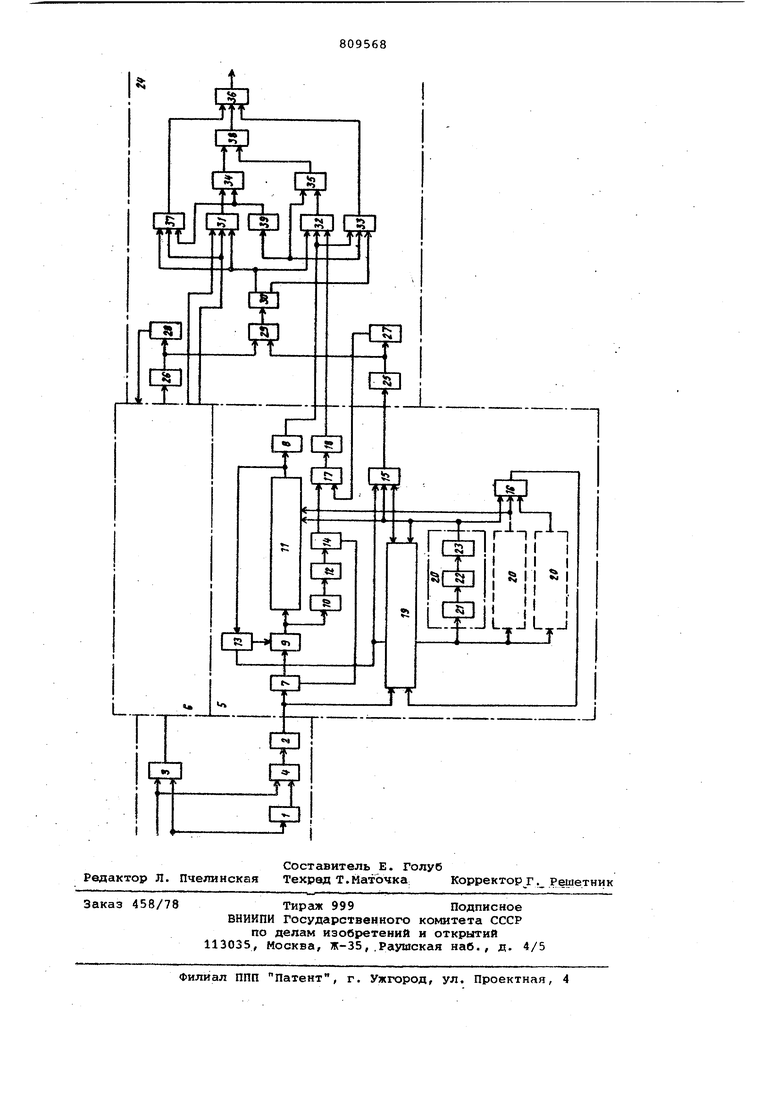

Изобретение относится к технике радиосвязи и может использоваться для помехоустойчивого приема в системах космической радиосвязи. Известно устройство декодирования линейного циклического кода, содержащее объединенные по первому входу пер вый блок логического сложения и первый инвертор, выход которого через вторюй блок логического сложения подключен ко входу второго инвертора, при этом вторые входы первого и второго блока логического сложения объединены, а также первый канал декодирования , содержащий буферный регистр и кодовый фильтр, выход которого подключен ко входам пороговых блоков, причем выход первого блока логического сложения подключен к первому входу первого канала декодирования ll Однако известное устройство имеет низкие помехоустойчивость и быстродействие. Цель изобретения - повышение помехоустойчивости и быстродействия. Поставленная цель достигается тем что в устройство декодирования линейного циклического кода, содержаще э объединенные по первому входу пер- вый блок логического сложения и первый инвертор, выход которого через второй блок логического сложения подключен ко входу второго инвертора, при этом вторые входы первого и второго блока логического сложения объединены, а также первый канал декодирования, содержащий буферный регистр и кодовый фильтр, выход которого подключен ко входам пороговых блоков, причем выход первого блока логического сложения подключен к первому .входу первого канала декодирования, введены второй канал декодирования и блок выбора канала, при этом к первому входу второго- канала декодирования подключен выход второго инвертора, а три выхода каждого канала декодирования подключены к соответствующим входам блока выбора канала, выходы которого подключены ко вторым входам каждого канала декодирования. При этом в каждый канал декодирования введены первый сумматор по модулю два, первый ключ, два блока совпадения, последовательно соединенные элемент пеиляти и второй ключ, а также последовательно соединенные третий ключ, счетный триггер, второй суюляхор по модулю два, третий блок срвпадения и управляющий триггер, при это второй выход элемента памяти подключен ко второму входу второго суммато ра по модулю два, а выход второго ключа подключен ко входам третьего ключа и буферного регистра, выход которого подключен ко входу первого ключа и первому входу первого сумматора по модулю два, ко второму входу которого, объединенному с первым вхо дом первого блока совпадения, подключен выход кодового фильтра, а выход первого сумматора по модулю два подключен ко второму входу второго ключа, выходы пороговых блоков подключены к соответствующим входам буферного регистра, первого блока совпадения и кодового фильтра, а также через второй блок совпадения к третьему входу кодового фильтра, четвертый вход которого объединен со входом элемента памяти и является первым входом каждого канала декодирования, вторым входом которого является второй вход третьего блока совпадения, а первым, вторым и третьим выходами каждого канала декодирования являются соответственно выхо ды первого ключа, управляющего триггера и первого блока совпадения. Причем пороговый блок выполнен в виде последовательно соединенных сум матора, усилителя с переменным поро гом усиления и каскада сопряисения, выход которого является выходом пор гового блока, входом которого является вход сумматора. Входная после010000000000довательность, b С детектора качества стертые 001000000001 символы Последователь011000000001 . ность, Ь Последователь010000000000ность, b Далее Ь к bg поступают в дваиден тичных канала декодирования 5 и 6. Пример работы перкого канала 5 декодирован у1. Входная последовательность Ь чсереэ элемент 7 пад-гятк, замннутнй второй ключ 9 поступает в буферный регистр 11 и в кодовый фильтр 19, производяйгий вычисление синдрома где Н - транспортированная проверочная матрица кода, составленная из коэффициентов проверочного полинома аи да h(x) « 1 + + + xf + x-fi На чертеже представлена структурная электрическая схема предлагаемого устройства. Устройство декодирования линейного циклического кода содержит первый и второй инверторы 1 и 2 соответственно, первый и второй блоки 3 и 4 логического сложения соответственно, первый и второй каналы декодирования 5 и б соответственно, каждый из которых состоит из элемента 7 памяти, первого, второго и третьего ключей 8, 9 и 1.0 соответственно, буферного регистра 11, счетного триггера 12, первого и второго сумматоров 13 и 14 по модулю два соответственно, первого, второго и третьего блоков 15, 16 и 17 совпадения соответственно, управляющего триггера 18, кодового фильтра 19 и трех пороговых блоков 20, каждый из которых содержит сумматор 21, усилитель 22 с переменным порогом усиления и каскад 23 сопряжения, блок 24 вьгбора канала, состоящий из двух счетчиков 25 и 26 ошибок, трех дешифраторов 27 - 29, управляющего триггера 30, восьми схем 31-38 совпадения и инвертора 39. Устройство работает следующим образом. На вход устройства поступает информационная последовательность Ь и . сигналы, соответствующие стертым символам в принятом сообщении. С помощью инверторов 1, 2 и блоков 3, 4 логического сложения формируются две последовательности Ь и Ьу, являющиеся результатами замены .стертых символов 011000101011 00.о 000010000 000000111011 0110001010 11 Бели ошибок при передаче нет, то н 0. При наличии ошибок во входной последовательности состояние будет ненулевым. После заполнения буферного регистра 11 и элемента 7 памяти (первые 24-е такта) ключ 9 соединяет выход с входом, ключ 8 раэкялкается и производится циклический сдвиг в буферном регистре 11 и кодовом фильтре 19. При Кс1ждом сдйиге записанное значение сравнивается с каждой из трех комбинаций покрывающего множества {йЛхУ (где j 1, 2, 3), включающего в себя полиномы Полиномы множества о(х)} реализуются с помощью комбинации прямых и j инверсных разрядов кодового фильтра 19. Вычисление веса разностей принятой последовательности Ь и полиномов множества корректируемых ошибок вы- . полняется с помощью пороговых элемен-«я тов, собранных на базе операционных усилителей. На входы сумматоров 21 поступают сигналы с соответствующих выходов ячеек кодового фильтра 19. Ко входу усилителя 22 через переменное сопротивление подключен источник постоянного напряжения, имекмдий полярность, противоположную полярности сигнала на выходе сумматора 21. С помощью источника и переменного сопротивления 20 задается величина порога срабатывания усилителя 22, Сигнал с выхода усилителя 22 через каскад 23 сопряжения и второй блок 16 совпадения поступает в кодовый фильтр 19 для 25 размыкания обратной связи. Если сигнал .появился на выходе пороговых элементов, соответствующих ) или Ci-,() то сигнал с выхода каскада сопряжения поступает в бу- jjj ферный регистр 11, значение в котором меняется на противоположное, и в кодовый лильтр, где инвертируется состояние соответствующих разрядов.. При условии, что сигнал на выхо- ..-35 де второго блока 16 совпадения появляется после i-ого сдвига, переданное слово восстанавливается при выполнении еще 23-i сдвигов, в течение которых исправленная часть кодового слова дополняется 11-тью символами, 40 поступающими из кодового фильтра 19. Первый ключ 8 замыкается и декодированная последовательность появляется на выходе буферного регистра 11. В то же время через замкнутый второй 5 ключ 9 осуществляется прием следующего кодового блока. В течение первых 24 тактов входная последовательность через замкнутый третий ключ 10 поступает на счетный триггер 12, осущест- JQ влякяций проверку на четность входной последовательности. По окончании 24 тактов третий ключ 10 размыкается, сигнал с иыхода счетного триггера 12 сравнивается со значением 24 символа кодового слова, являющегося рвзульта- том проверки на четкость иа передающей стороне. Логическая единица на выходе сумматора 14 по модулю два указывает на отсутствие ошибки в принятой последовательности или на на- М личие ошибок, кратных двум. Логический ноль на выходе сумматора 14 по модулю два указывает на наличие 1, 3,5,7... и так далее ошибок. На третий блок 17 совпадения поступают налы с сумматора 14 по модулю два и дешифратора 27 трех ошибок первого канала. Сигнал ка выходе третьего блока 17 совпадения появляется только в случае наличия логической единицы с третьего ключа 10 и сигнала с дешифратора 27 трех ошибок. Это свидетельствует о появлении четьфех некорректируемых ошибок в кодовом слове. Полученный сигнал через управляющий триггер 18 поступает в блок 24 выбора канала. Логика работы блока выбора канала 11редставлена в таблице. Выход кодового фильтра 19 первого канала подключен к счетчику 25 ошибок. К счетчику 26 подключен выход кодового фильтра второго канала декодирования 6. алполнение операций, соответствующих первым 18 пунктам таблицы, происходит с помощью схемы 33 совпадения, открытой до момента обнаружения трех ошибок в каждом из канёшов или четырех ошибок в первом канале. Дешифратор 29 и управляющий триггер 30 служат цля отпирйния схем .31 и 32 совпадения в случае обнаружения трех ошибок в первом и втором каналах 5 и 6 декодирования. Схема 33 при этом запирается сигналом с противоположного плеча управлякицего триггера 30. В этом случае доступ абонента к каналам осуществляется также при отсутствии сигнала Четыре ошибки, поступающего с управлшшдих триггеров 18 обоих каналов. Выполнение операций, соответствую щих пунктам 23, 24 и 25 таблицы, осу ществляется с помощью схемы 37 совпадения, открытой сигналом Четыре ошибки педвого канала и сигналом с управляющего триггера 30. Инвертор 39 и схема 34, 35 и 38 совпадения образуют схему приоритета первого канала для случая одновременного появления трех корректируемых ошибок в первом и втором канала Использование в устройстве двух паргишельных каналов декодирования и блока выбора канала позволяет применять данное устройство в канале со стиранием, что снижает требуемое отношение сигнал/шум на входе приемника в 1,5 раза при неизменной вероятности ошибки на один двоичный символ Формула изобретения 1. Устройство декодирования линей ного циклического кЪда, содержащее объединенные по первому входу первый блок логического сложения и первый инвертор, выход которого через второй блок логического сложения подключен ко входу второго инвертора, при этом вторые входы первого и вто рого блока логического сложения объединены, а также первый канал декодирования, содержЕоций буферный регис и кодовый фильтр, выход которого под ключен ко входам пороговых блоков, причем выход первого блока логическо го сложения подключен к первому вход первого канала декодирования, отличающееся тем, что, с целью повьшения помехоустойчивости и (стродействия, в него введены второ каигт декодирования и блок выбора ка нала, при этом к первому входу второ го канала декодирования подключен вы ход второго инвертора, а три выхода каждого канала декодирования пoдкJвoчены к соответствующим входам блока выбора канала, выходы которого подключены ко вторым входам каждого канала декодирования. 2.Устройство по п. 1, отличающееся тем, что в каждый канал декодирования введены первый сумматор по модулю два, первый ключ, два блока совпадения, последовательно соединенные элемент памяти и второй ключ, а также последовательно соединенные третий ключ, счетный триггер, второй сумматор по модулю два, третий блок совпадения и управляющий триггер, при этом второй выход элемента.памяти подключён ко второму входу второго сумматора по модулю два, а выход второго ключа подключен ко входам третьего ключа и буферного регистра, выход которого подключен ко входу первого ключа и первому входу первого сумматора по модулю два, ко второму входу которо.го, объединенному с первым входом первого блока совпадения, подключен выход кодового фильтра, а выход первого сумматора по модулю два подключен ко второму входу второго ключа, выходы пороговых блоков подключены к соответствующим входам буферного регистра, первого блока совпадения и кодового фильтра, а также через второй блок совпадения к третьему входу кодового фильтра, четвертый вход которого объединен со входом элемента памяти и является первым входом каждого канала декодирования, вторым входом которого является второй вход третьего блока совпадения, а первым, вторым и третьим выходами каждого канала декодирования являются соответственно выходы первого ключа, управляющего триггера и первого блока совпадения. 3.Устройство по п. 2, отличающееся тем, что пороговый блок выполнен в виде последовательно соединенных сумматора, усилителя с переменным порогом усиления и каскада сопряжения, выход которого является выходом порогового блока, входом крторого является вход сумматора. Источники информации, принятые во внимание при экспертизе 1. Kasamt Т. Decoding Procedure for МЫ р le-E rror-Correct i ng Cyclic Codes, TEEE Transactions IT-10, 2, 1964, p. 134-138 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО СИНХРОНИЗАЦИИ НА ОСНОВЕ КОМБИНИРОВАННОГО ПРИМЕНЕНИЯ ДВОЙСТВЕННОГО БАЗИСА ПОЛЯ GF(2) И ВЫДЕЛЕНИЯ "СКОЛЬЗЯЩЕГО ОКНА" С ОШИБКАМИ | 2014 |

|

RU2580806C2 |

| Устройство для приема избыточной информации | 1982 |

|

SU1032470A1 |

| Устройство для устранения неопределенности дискретнофазовой модуляции | 1983 |

|

SU1095428A1 |

| УСТРОЙСТВО ДИВЕРГЕНТНОГО ДЕКОДИРОВАНИЯ СЕГМЕНТОВ ЛИНЕЙНОЙ РЕКУРРЕНТНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ | 2023 |

|

RU2820053C1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ ПСЕВДОСЛУЧАЙНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ С ФУНКЦИЕЙ ИСПРАВЛЕНИЯ ОШИБОК | 2011 |

|

RU2486682C2 |

| ВОЛОКОННО-ОПТИЧЕСКАЯ СИСТЕМА С БЕЗОПАСНОЙ ПЕРЕДАЧЕЙ ИНФОРМАЦИИ | 1995 |

|

RU2100906C1 |

| Кодек каскадного блочного кода | 1985 |

|

SU1338075A1 |

| Пороговый декодер сверточного кода | 1982 |

|

SU1078654A1 |

| Система для передачи и приема дискретной информации | 1979 |

|

SU903850A1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ РЕКУРРЕНТНОЙ ПОСЛЕДОВАТЕЛЬНОСТЬЮ С ФУНКЦИЕЙ ВЫДЕЛЕНИЯ ЗАЧЕТНЫХ ИМПУЛЬСОВ В СКОЛЬЗЯЩЕМ ОКНЕ | 2013 |

|

RU2553089C2 |

Авторы

Даты

1981-02-28—Публикация

1979-02-26—Подача