Изобретение относится к электросвязи и может использоваться для повышения достоверности в системах связи при передаче данных, цифровых сигналов радиовещания и телевидения при кодировании и декодировании их сверточными кодами.

Известен кодек сверточного кода, содержащий на передающей стороне входные и выходные полусумматоры, синхрогенератор передачи и кодер, а на приемной стороне - формирователь сигнала синдрома, приемник синхросигнала, синхрогенератор приема, корректор ошибок,Ч входных и n-k выходных полусумматоров, где k -число информационных ветвей, h - общее число ветвей сверточного кода tljt

Недостаток указанного кодека низкая помехоустойчивость из-за эффекта размножения ошибок декодером.

Наиболее близким к предлагаемому является пороговый декодер сверточного кода, содержащий объединенные по входу кодер и корректор ошибок, а также анализатор синдрома, выходы которого через пороговый элемент и блок запрета коррекции подключены к входам корректора ошибок и анализатора синдрома СЗЗ,

Недостатком известного порогового декодера является наличие эффекта размножения ошибок, что снижает помехоустойчивость, так как если в случае появления одной ошибки в информационной последовательности производится коррекция в кодере (исправле ние ошибки) и коррекция в анализаторе синдрома АС (очищение регистра сдвига синдрома от размножения ошибки) , то при появлении трех ошибоьэ, и которых одна информационная, производится коррекция ошибочного символа, а коррекция регистра сдвига АС не производится, т.е очищения регистра сдвига АС не происходит, следовательно , декодер способен к pasMHO жению. ошибок. По этой же причине декодер способен к размножению ошибок при поступлении четырех ошибок.

При возникновении в канале связи длительных пакетов ошибок мультиплек сору (обнаружителю пакетов ошибок) потребуется дополнительно не менее т/2 фактов (пт-длина регистра сдвига РС и АС и определяется максимальной степенью образующих многочленов) для обнаружения ошибок, так как информация об ошибках с выхода PC АС на вход му: ьтиш1ексора(обнаружителя пакетов ошибок) поступает в последовательном коде и тем самым увеличивается вероятность пропуска ошибок и уменьшение помехоустойчивости декодера. Известный пороговый декодер реализуют для ниэкочастотных сверточных кодЪв со скоростью кода R 1/п, п7/ 2, 3 ....

Цель изобретения - повышение помехоустойчивости за счет устранения эффекта размножения ошибок.

Указанная цель достигается тем, что пороговый декодер сверточного кода, содержащий объединенные по входу кодер и корректор ошибок, а также анализатор синдрома, выходы которого через пороговый элемент и блок запрета §оррекции подключены к входам корректора ошибок и анализатора синдрома, введены.формирователь синдромной последовательности, мультиплексор, блок совпадения, пороговый счетчик, формирователь временного интервала,D -триггер, блок формирования тактовых импульсов, К-1 группа, каждая состоящая из последовательно соединенных порогового элемента и бхюка запрета коррекции, при этом выход кодера подключен через формирователь синдромной последовательности, к второму входу которого подключен проверочный выход дискретного канала, к соответствующему входу анализатора синдрома, соответствующие выходы которого подключены к входам К-1 пороговых элементов, а выходы К-1 блоков запрета (Коррекции подключены к соответст-. вующим входам корректора ошибок и анализатора синдрома, причем выходы К пороговых элементов подключены к первым входам мультиплексора, к вторым входам которого и к тактовым входам блока совпадения и формирователя временного интервала подключены выходы блока формирования тактовых импульсов, выход мультиплексора подключен к первому входу блока совпадения, выход которого через пороговый счетчик подключен к С-входу D- триггера, к )-входу которого, вторым входам порогового счетчика и формирователя временного интервала подключен выход формирователя временного интервала, а выход D -триггера подключен к третьему входу блока совпадения, к вторым входам К блоков .запрета коррекции и к D -входу D триггера.

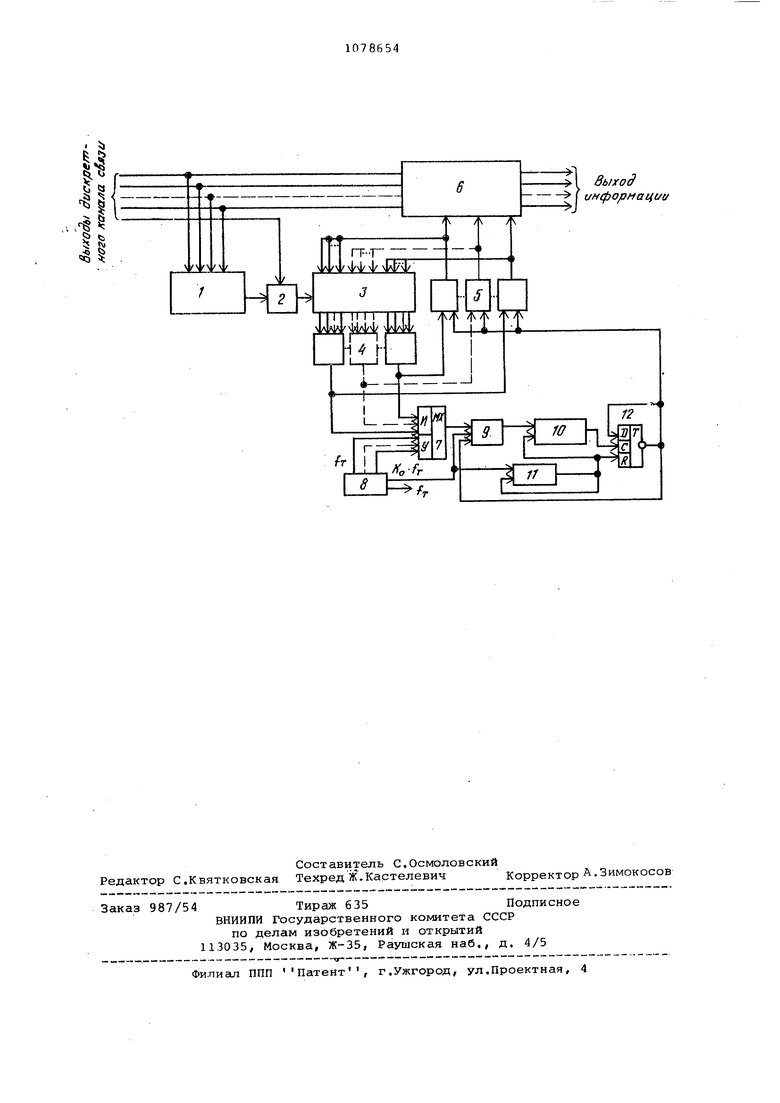

На чертеже приведена структурная схема предлагаемого порогового декодера.,

Пороговый декодер сверточного кода содержит кодер 1, формирователь 2 синдрома, анализатор 3 синдрома К пороговых элементов 4, К блоков 5 запрета коррекции, корректор 6 ошибок, мультиплексор 7, блок 8 формирования тактовых импульсов, блок 9 совпадения, пороговый счетчик 10, формирователь И временного интервала, -триггер 12,

Кодер 1 по принятым информационным символам формирует символы проверочной последовательности. В качестве кодера 1 используется регистр сдвига PC со встроенными сумматорами по модулю два. Длина PC определя ется максимальной степенью порождаю щих полиномов , j - 1, 2, 3., ,. Kg | сверточного кода со скоростью R , а число сумматоров по модулю два равно (JKo -1), при этом выходной сумматор многоходовой (.Пр входов), Формирователь 2 синдрома служит для формирования синдромной последо вательности из принятой проверочной последовательности и проверочной последовательности, сформированной на приемной стороне. В качестве фор мирователя 2 синдрома используется сумматор по модулю два. Анализатор 3 синдрома предназначен для обнаружения и исправления ошибок в информационных символах и .представляет собой PC с обратными связями и с встроенными сумматорами по модулю два. Принципиальная элект рическая схема анал 1затора 3 синдро ма полностью опред яется порождающими полиномами , j 1,2,3,,,,, Пороговые элементы 4 предназначе ны для принятия решения о достоверности принятых информационных симво лов. Связи пороговых элементов (ПЭ) с ячейками памяти PC анализатора 3 синдрома определяются соответствующими порождающими полиномами G , 1 1 2, ,,, Kg , При числе ортогональных проверок порог устанавливается ра.вным Т7/3, Следовательно, алгоритм работы ПЭ следующий: при поступлении на вход ПЭ трех или четырех ненулевых символов (при J 4 и таких комбинаций пять: 1-1110, 2-1101, 3-101 4-0111, 5-1111) с соответствующих ячеек памяти PC анализатора синдро.ма принимается решение об исправлении информационного символа, С выхо да ПЭ на корректор ошибок поступает логическая единица, а во всех остал ных случаях коррекция символа не производится. Блок 5 запрета коррекции предназ начен для запрета поступления корре ции с выхода соответствующего ПЭ на корректор ошибок при возникновении в канале связи ошибок, превосходящи корректирующую способность сверточного кода,. Корректор б ошибок представляет собой совокупность последовательных PC, число которых определяется скоростью кода, т,е, . Длина PC, т,е, количество разрядов или ячеек памяти, определяется максималь ной степенью порождающих полиномов Ci), j 1,2, ,,., Kg, PC заканчивается сумматором по модулю два, на один вход которого поступают символы соответствующей информационной последовательности, а на второй входсимволы коррекции. Мультиплексор 7 предназначен для преобразования ;, 2, ,,, К входных параллельных потоков в один последовательный поток. Скорость передачи выходного потока в К раз больше скорости передачи входного потока. Блок 8 формирования тактовых импульсов предназначен для формирования тактовых импульсов, необходимых для функционирования декодера и являющихся самостоятельным устройством декодера. Блок 9 совпадения предназначен для стробирования выходной информации мультиплексора при записи ее в пороговый счетчик 10 и блокировки входной информации порогового счетчика при превышении порога, Стробирование информации осуществляется тактовой частотой с выхода блока 8 формирования тактовых частот, а блокировка - выходным импульсом D -триггера 12 , . Пороговый счетчик 10 пpeднaзнa Jeн для блокировки выходов ПЭ 4 при возникновении в канале связи ошибок, превышающих корректирующую способность сверточного кода. Пороговый счетчик состоит из собственно счетчика и дешифратора. Порог выбирается равным П ; с -минимальное кодовое расстояние сверточного кода. При превышении порога с выхода дешифратора на вход D -триггера 12 поступает импульс, переводящийР -триггер в положение, когда с его инверсного выхода снимается логический ноль. Триггер остается в таком положении до поступления на R--вход импульса с выхода дешифратора формирователя 11 временного интервала, Коэффицие т счета выбирается равным К ,. Формирователь 11 временного интервала служит для установления временного интервала анализа информации, поступающей на вход порогового счетчика 10, и формирования импульсов, следующих с периодом, равным -интервалу анализа, В качестве формирователя временного интервала анализа кода используется счетчик с коэффициентом счета равным (т +1), т,е. (т +1), m -наивысшая степень порождающих полиномов и-)) , j 1 2, , , ,, KQ, Формирователь 11 временного интервала анализа состоит из собственно счетчика и дешифратора,D-триггер 12 предназначен для формирования импульса запрета коррекции принятой информации при возникновении в канале связи ошибок, превышающих исправляющую способность сверточного кода. Рассмотрим принцип работы порого вого декодера на примере сверточног кода со скоростью кода 4/5; 3 4; dr: + , т ,е ., |сра :ностью , е , крах HuuibHJ ..JLl. на исправляемых ошибок 2 длине кодового расстояния Пд r(m+l) X По ,{26 + 1) - 5 1 35, m - максимальна степень порождающих полиномов Gjfi) , j 1,2,3,4. Принятые символы К:4 информацион ных подпотоков одновременно поступают на входы соответствующих РС| корректора 6 ошибок и на соответствующие входы кодера 1. В кодере 1 из принятых информационных символов формируются символы проверочной пос ледовательности, которые поступают на один из входов формирователя 2 синдрома, на второй вход которого с выхода дискретного канала связи поступают символы принятой проверочной последовательности. Производится формирование символов синдромной последовательности, структура которой зависит от типа ошибок как в информационных, так и проверочных символах. Символы синдромной последователь ности поступают на вход анализатора 3 синдрома, производится заполне ние символами PC анализатора синдро ма в течение m 26 тактов. На т + 1 такте производится анализ пороговыми элементами структуры синдромной последовательности и принятие решения о достоверности (Первого блока из информационных символов. Решение о достоверности декодирования: если на вход ПЭ с ; анализатора 3 синдрома поступит ненулевых символов больше установленного порога, т,е, более Т.3, то принимается решение, что информационный символ принят ошибочным и с выхода ПЭ одновременно на корректор 6 ошибок и на соответствующие сумма торы по модулю два PC анализатора 3 синдрома поступает импульс коррекции (логическая единица), Предположим, что в принятой инфо мации два ошибочных символа (пусть будут в первом и третьем информационных подпотоках) , т,е. число не превышает корректирующей способности кода. В соответствии с алгоритмом поро гового декодирования с выхода перво го и третьего пороговых элементов 4 импульсы коррекции (логическая единица) одновременно поступают на оди из входов первого и третьего блоков 5 запрета коррекции и на входы муль типлексора 7, С выходов второго и четвертого пороговых элементов 4 на входы соответствующих блоков 5 запрета коррекции и на входьд мультиплексора 7 поступают логические нули. В мультиплексоре 7 производится объединение параллельных потоков в последовательный поток. Скорость выг: ходного последовательного потока в раз больше скорости входных потоков и тем самым достигается согласование работы порогового счетчика 10 и пороговых элементов 4, Через блок совпадения, который стробируется частотой равной , импульсы с выходов пороговых элементов 4 поступают на вход порогового счетчика 10, который также тактируется частотой Krf. В связи с тем. что на длине кодового ограничения число ошибок, превышающих корректирующую способность кода, может встречаться в любом месте, коэффициент счета выбирается равным К ,ц .пг1, т.е, максимальной степени образующего полинома. Порог дешифратора устанавливается равным трем, но установка в нулевое состояние производится формирователем вр еменного интервала анализа, С выхода дешифратора порогового счетчика 10 на тактируемый вход С D -триггера 12 поступает логический ноль и с выхода D-триггера 12 на вторые входы блоков 5 запрета коррекции логическая единица, импульсы коррекции поступят одновременно на корректор 6 ошибок и на соответствующие входы сумматоров по модулю два PC анализатора 3 синдрома. Производится одновременно коррекция ошибочных символов в первом и в третьем информационных подпотоках и коррекция символов синдромной посгг ледовательности, Предположим, что на этой же длине . кодового ограничения Ид ошибочным .принят еще один информационный символ (например, во втором информаидионном подпотоке) , В -зависимостей от структуры синдромной последовательности в PC анализаторе 3 синдрома ошибочно сработают один или более пороговых элементов 4, При этом бу-дет достигнут или превышен порог срабатывания дешифратора порогового счетчика 10, С выхода дешифратора на вход С Б -триггера 12 поступит логическая единица, которая перебрасывает триггер во второе состояние, С инверсного выхода D -триггера 12 поступает логический ноль одновременно на вход D -триггера 12 и бло- кирует его в этом состоянии, на вход блока 9 совпадения и блокирует вход порогового счетчика 10, на входы бло-с. ков 5 запрета коррекции и блокирует прохождение импульса коррекции с выходов пороговых элементов 4 на корректор 6 ошибок и на входы сумматоров 110 модулю два PC анализатора 3 синдрома. За время блокировки происходит также полная или частич-. ная смена (перезапись) синдромной последовательности в PC анализатора 3 синдрома, уменьшается тем самым вероятность размножения ошибок. Таким образом, не происходит ошибочно коррекции информационных символов и символов синдромной последовательно сти, исключая тем самым возможность распространения ошибок на выходе де кодера и обеспечивая реализацию кор ректирующей способности сверточного кода. В результате повышается помехоустойчивость порогового декодирования, По окончании времени анализа, которое задается формирователем 11 временного интервала анализа, входным импульсрм дешифратора пороговый счетчик 10 и D -триггер 12 устанавливаются в первоначальное состояние (установка в ноль). С выхода D -три гера 12 на вход блока 9 совпадения, на входы блокоэ 5 запрета коррекции и на вход D D- триггера поступает логическая единица и производится разблокировка данных устройств. -Предположим, что в принятой информации ошибочным являются три (па кет из трех ошибок) информационных символа. В соответствии со структурой синд ромной последовательности, записанной в PC анализатора 3 синдрома, по роговыми элементами 4 принимается решение о достоверности принятых информационных символов и символов синдромной последовательности т.е. к размножению ошибок. Однако размно жения ошибок не происходит, так как при поступлении на вход порогового счетчика 10 импульсов -коррекции пре вышен порог (число ненулевых символов более ). С выхода дешифратора порогового счетчика 10 на вход С D-триггера 12 п оступит высокий уровень (логический ноль) и блокирует прохождение импульсов коррекции с .выходов пороговых элементов 4 на ко IpeKTOp б ошибок и на входы соответствующих сумматоров по модулю два PC анализатора 3 синдрома. -Таким образом, исключается ошибочная коррекция информационных символов и символов синдромной последовательности и, следовательно, исключается эффект размножения ошибок. На выход декодера посгупаог гольы:) пакет ошибок из трех символов. Одновременно блокируется вход блока g совпадения. Длительность блокировки входов блоков 5 запрета коррекции и блока 9 совпадения определяется работой формирователя временного интервала анализа 11. По окончании времени анализа ( i формирователя временного интервала анализа равен hi +1 такт) пороговый счетчик 10 и D -триггер 12 устанавливаются в первоначальное (нулевое) состояние. За время блокировки, как указывалось выше, производится частичная или полная перезапись синдромной последовательности в PC анализатора 3 синдрома, что также приводит к уменьшению вероятности ошибочного декодирования. Аналогичным образом устраняется ошибочное декодирование и размножение ошибок при возникновении в канале связи болылих пакетов ошибок, значительно превосходящих корректирующую способность сверточного кода. Таким образом, блокировка импульсов коррекции с выходов пороговых элементов 4 при возникновении в канале связи ошибок, превосходящих корректирующую способность сверточного кода, т.е. Ъ J/2 (где b -величина пакета ошибок, Э/2 ::i i - кратность гарантированно исправляемых ошибок), исключает ошибочную коррекцию информационнных символов и сим-волов синдромной последовательности и тем самым исключается эффект размножения ошибок и реализация корректирующей способности сверточного кода. Кроме того, блокировка соответствующих входов сумматоров по модулю два PC анализатора 3 синдрома позволяет произвести частичную или полную смену символов синдромной последовательности PC анализатора 3 синдрома и уменьшить тем самым вероятность ошибочного декодирования и размножения ошибок, в результате чего повышается помехоустойчивость или корректирующая способность порогового декодирования. Исследования корректирующей способности сверточного кода налабораторном макете подтверлодают то, что размножение ошибок практически устранено. Энергетический выигрыш кодирования - декодирования равняется 3 дБ.

I выход

I информации

| название | год | авторы | номер документа |

|---|---|---|---|

| Декодер сверточного кода (его варианты) | 1985 |

|

SU1320875A1 |

| Декодер сверточного кода | 1985 |

|

SU1320904A1 |

| Пороговый декодер сверточного кода | 1984 |

|

SU1185629A1 |

| Кодек несистематического сверточного кода | 1990 |

|

SU1714812A1 |

| Устройство для устранения неопределенности дискретнофазовой модуляции | 1983 |

|

SU1095428A1 |

| ПОРОГОВЫЙ ДЕКОДЕР СВЕРТОЧНОГО КОДА | 1991 |

|

RU2023349C1 |

| Пороговый декодер сверточного кода | 1985 |

|

SU1252944A1 |

| Пороговый декодер сверточного кода | 1991 |

|

SU1781825A1 |

| Пороговый декодер сверточного кода | 1991 |

|

SU1837385A1 |

| Пороговый декодер сверхточного кода | 1976 |

|

SU586571A1 |

ПОРОГОВЫЙ ДЕКОДЕР СВЕРТОЧНОГО КОДА,содержащий объединенные по входу кодер и корректор ошибок, а также анализатор синдрома, выходы которого через пороговый элемент и блок запрета коррекции подключены к входам корректора шибок и анализатора синдрома,о тличающийся тем,что,с целью повышения помехоустойчивости,в него введены формирователь синдромной последовательности, муль-типлекс6р блок совпадения, пороговый счетчик, формирователь временного интервала, -триггер,блок формирования тактовых импульсов, К-1 группа, каждая состоящая из последовательно сГоединенных порогового элемента и блока запрета коррекции, при этом выход кодера подключен через формирователь синдромной .последовательности, к второму входу которого подключен проверочный выход дискретного канала,к соответствующему входу arriaлизатора синдрома,соотвётствующие выходы которого подключены к входам К-1 пороговых элементов, а выходы К -1 6Jloков запрета коррекции подключены к соответствующим входам корректора ошибок и анализатора синдрома, причем выходы К. пороговых элементов подключены к первым входам мультиплексора, к вторым входам которого и к тактовым входам блока совпадения и формирова- теля временного интервала подключе- «g ны выходы блока формирования такто(Л вых импульсов, выход мультиплексора подключен к первому входу блока совпадения, выход которогй через пороговый счетчик подключен к С -входу JJ- триггера, к R -входу которого, вто-S рым входам п6 огового счетчика и фор1«1ирователя временного интервсша подключен формирователя временного интервала, а выходЭ-триггера под ключей к третьему входу блока совпа00 ;дения, к вторым входам К--блоков запрета коррекции и к JD .-входу .Ф -тригW ел ;гера. 4

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Кодек сверхточного кода | 1976 |

|

SU605324A1 |

| кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Пороговый декодер сверхточного кода | 1976 |

|

SU586571A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1984-03-07—Публикация

1982-12-13—Подача