ства соединен с третьим входом первого элемента И и через элемент НЕ - с TipeTb:им .входом элемента И.

Необходимо отметить, что в зависимости от конкретного внда модуляции и используемого модулятора может потребоваться различное число синхронных сигналов, изменяющихся по определенным п разным законам. Поэтому, вообще говоря, к выходу счетчика может быть параллельно подключено различное число блоков памяти, выход каждого будет подключен к выходу устройства через свой цифро-аналоговый преобразователь. Устройство в этом случае будет многоканальным.

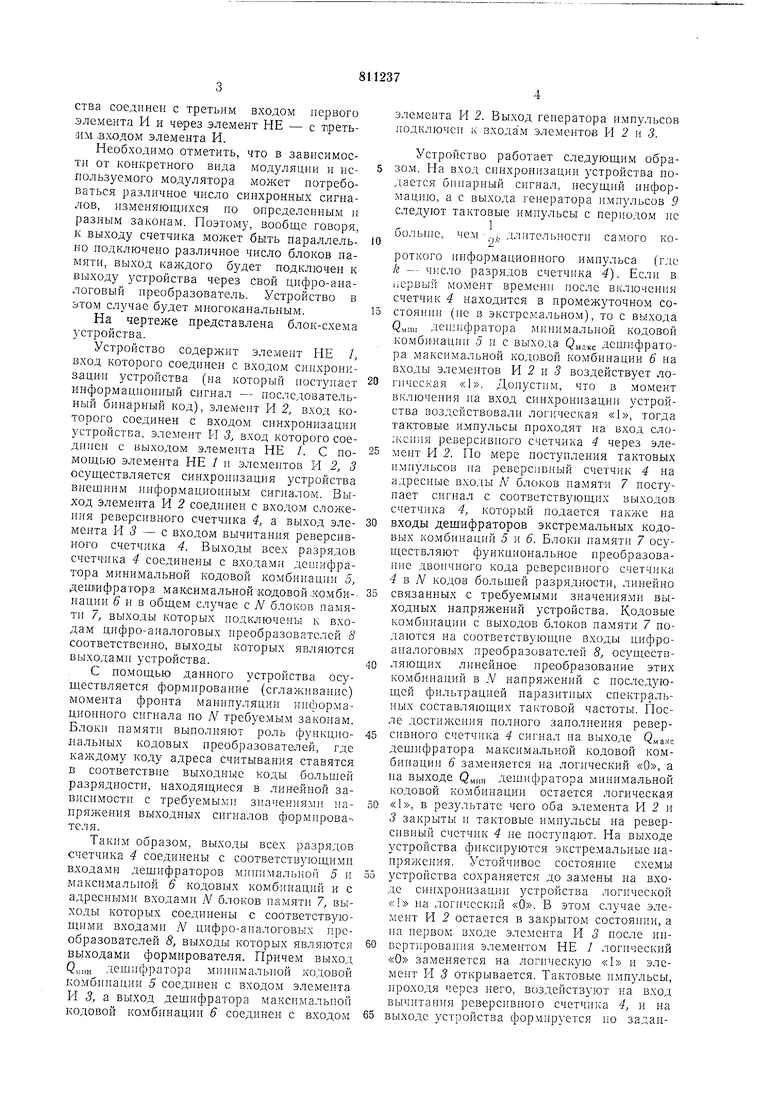

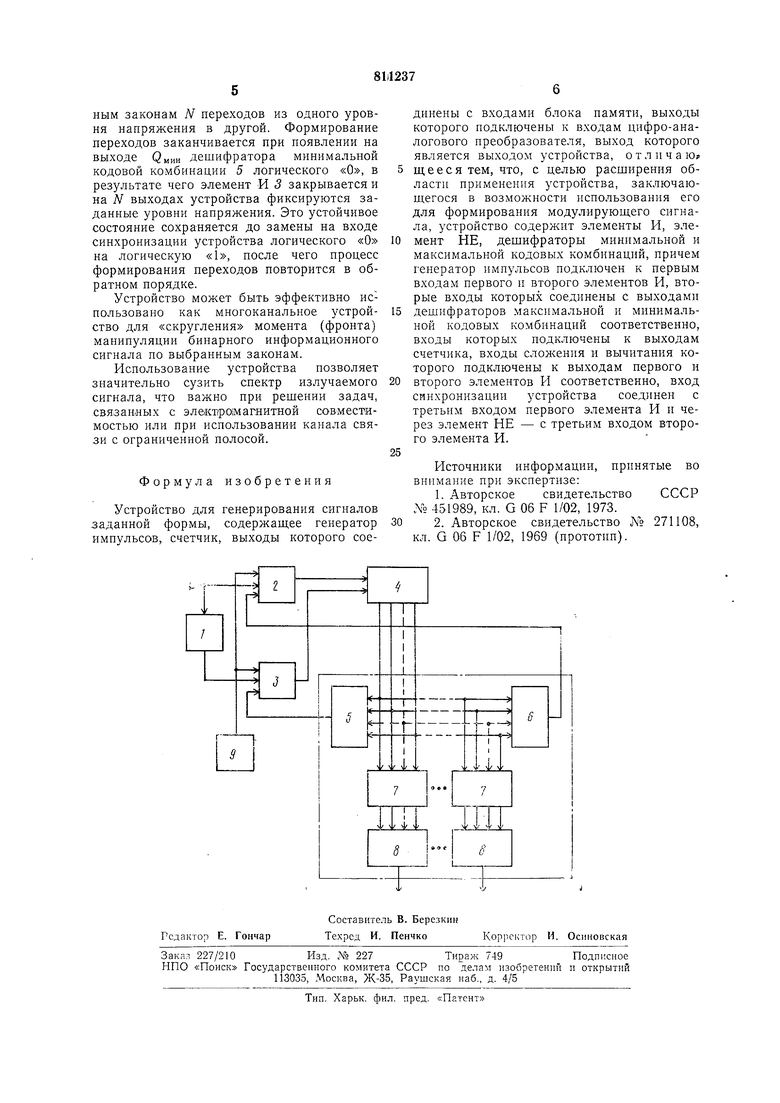

На чертеже представлена блок-схема устройства.

Устройство содержит элемент НЕ /, вход которого соединен с входом сиихронизацш-1 устройства (па который поступает информационный сигнал - последовательный бинарный код), элемент И 2, вход которого соединен с входом еинхронизации устройства, элемент И 3, вход которого соединен с выходом элемента НЕ /. С помощью элемента НЕ / и элементов И 2, 3 осуществляется синхронизация устройства внешним информационным сигналом. Выход элемента И 2 соединен с входом сложения реверсивного счетчика 4, а выход элемента И 5 - с входом вычитания реверсивного счетчика 4. Выходы всех разрядов счетчика 4 соединены с входами дешифратора минимальной кодовой комбинации 5, дешифратора максимальной кодовой .комби-нации 6 и в общем случае с N блоков памяти 7, выходы которых подключены к входам цифро-аналоговых преобразователей 8 соответственно, выходы которых являются выходами устройства.

С помощью даиного устройства осуществляется формирование (сглаживание) момента фронта манипуляции информационного сигнала по N требуемым законам. Блоки иамяти выполняют роль с)уикциолальных кодовых преобразователей, где каждому коду адреса считывания ставятся в соответствие выходные коды большей разрядности, находящиеся в линейной зависимости с требуемыми значениями иапряження выходных сигналов формирова-. теля.

Таким образом, выходы всех разрядов счетчика 4 соединены е соответствующими входами дешифраторов минимальной 5 и максимальиой 6 кодовых комбинаций и е адресными входами /V блоков памяти 7, выходы которых соедииены с соответствующими входами .V цифро-аналоговых преобразователей 8, выходы которых являются выходами формирователя. Причем выход Qiiiii, дешифратора минимальной кодовой комбинации 5 соединен е входом элемента PI 3, а выход дешифратора максимальной кодовой комбинации 6 соединен с входом

элемента И 2. Выход генератора импульсов иодключеи 1 входам элементов П 2 и 3.

Устройство работает следующим образом. На вход сннхроиизации уетройетва подается бинарный сигнал, несущпй информацию, а е выхода генератора импульсов 9 следуют тактовые имиульсы с периодом не

1

оолыне, чем ,,j длительности самого короткого информационного имиульса (где /г - число разрядов счетчика 4). Если в ьсрвый момент времени иосле включения счетчик 4 находится в промежуточном ео5 стоянии (не в экстремальном), то с выхода QMHII денл;фратора минимальной кодовой комбинации 5 и с выхода QuaKc дешифратора максимальной кодовой комбннации 6 па входы элементов Н 2 и 5 воздействует логическая «1. Доиустим, что в момент включеиия на вход сиихронизации устройства воздействовали логическая «1, тогда тактовые импульсы проходят на вход сло;ксиия реверсивиого счетчика 4 через эле5 мент И 2. По мере поступления тактовых импульсов на реверсивный счетчик 4 иа адресиые входы Л блоков иамяти 7 иостуиает сигнал с соответствующих выходов счетчика 4, который иодается также на 0 входы дешифраторов экстремальных кодовых комбинаций 5 и 6. Блоки намяти 7 осуществляют функциональное нреобразование двоичного кода реверсивного счетчика 4 ъ N кодов большей разрядности, линейно 5 связанных с требуемыми значениями выходных напряжений устройства. Кодовые комбинации с выходов блоков иамяти 7 подаются иа соответствующие входы цифроаиалоговых преобразователей 8, осуществ0 ляющих линейное преобразование этих комбннации в ;V напряжений с носл-едующей фильтрацией паразитных сиектральных составляющих тактовой частоты. После достижения полпого заполнения ревер5 сивпого счетчика 4 сигнал иа выходе Qwaxc дешифратора максимальной кодовой комбииацни 6 замеияется на логический «О, а на выходе Р„„н дешифратора минимальной кодовой комбннации остается логическая 50 «1, в результате чего оба элемента PI 2 и 5 закрыты и тактовые нмнульсы иа реверсивный счетчнк 4 не иостуиают. На выходе устройства фиксируются экстремальные наиряжения. Устойчивое состояние схемы 5 устройства сохраняется до замены на входе синхронизации устройства логической «1 на логический «О. В этом случае элемеит И 2 оетается в закрытом состоянии, а на нервом входе элемента И 3 ноеле ин60 всртирования элементом НЕ / логический «О заменяется на логическую «1 и элемент И 3 открывается. Тактовые импульсы, нроходя через него, воздействуют на вход вычитания реверсивиого счетчика 4, и на 65 выходе уетройетва формируется по задайным законам N переходов из одного уровня напряжения в другой. Формирование переходов заканчивается при появлении на выходе QMHH дешифратора минимальной кодовой комбинации 5 логического «О, в результате чего элемент И 3 закрывается и на N выходах устройства фиксируются заданные уровни напряжения. Это устойчивое состояние сохраняется до замены на входе синхронизации устройства логического «О на логическую «1, после чего процесс формирования переходов повторится в обратном порядке.

Устройство может быть эффективно использовано как многоканальное устройство для «скругления момента (фронта) манипуляции бинарного информационного сигнала по выбранным законам.

Использование устройства позволяет значительно сузить спектр излучаемого сигнала, что важно при решении задач, связанных с элект(р01магнитной совместимостью или при использовании канала связи с ограниченной полосой.

Формула изобретения

Устройство для генерирования сигналов заданной формы, содержаш,ее генератор импульсов, счетчик, выходы которого соединены с входами блока памяти, выходы которого подключены к входам цифро-аналогового преобразователя, выход которого является выходом устройства, о т л и ч а ю щеесятем, что, с целью расширения области применения устройства, заключающегося в возможности использования его для формирования модулирующего сигнала, устройство содержит элементы И, элемент НЕ, дешифраторы минимальной и максимальной кодовых комбинаций, причем генератор импульсов подключен к первым входам первого и второго элементов И, вторые входы которых соединены с выходами

дешифраторов максимальной и минимальной кодовых комбинаций соответственно, входы которых подключены к выходам счетчика, входы сложения и вычитания которого подключены к выходам первого и

второго элементов И соответственно, вход синхронизации устройства соединен с третьим входом первого элемента И и через элемент НЕ - с третьим входом второго элемента И.

Источники информации, принятые во внимание при экспертизе:

1.Авторское свидетельство СССР ЛЬ 451989, кл. G 06 Е 1/02, 1973.

2.Авторское свидетельство № 271108, кл. G 06 Е 1/02, 1969 (прототпп).

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой генератор модулирующего сигнала | 1978 |

|

SU746480A1 |

| Устройство для ограничения спектра частотно-манипулированного сигнала | 1980 |

|

SU907852A1 |

| Формирователь сигналов с угловой модуляцией | 1985 |

|

SU1241411A1 |

| Фазовый модулятор | 1978 |

|

SU771783A1 |

| Устройство для генерирования сигналов заданной формы | 1979 |

|

SU886223A2 |

| Частотный манипулятор | 1980 |

|

SU873450A1 |

| Частотный манипулятор | 1979 |

|

SU886300A1 |

| Устройство для логарифмирования чисел | 1984 |

|

SU1257846A1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО ОПРЕДЕЛЕНИЯ ВЫИГРЫШНОЙ КОМБИНАЦИИ ПРИ ИГРЕ В РУЛЕТКУ | 1994 |

|

RU2122878C1 |

| Генератор импульсов | 1981 |

|

SU957424A1 |

Авторы

Даты

1981-03-07—Публикация

1978-06-01—Подача