«1

Изобретение относится к вычислительной технике и может быть использовано в информационных системах

Цель изобретения - повышение точности и увеличение быстродействия логарифмирования,

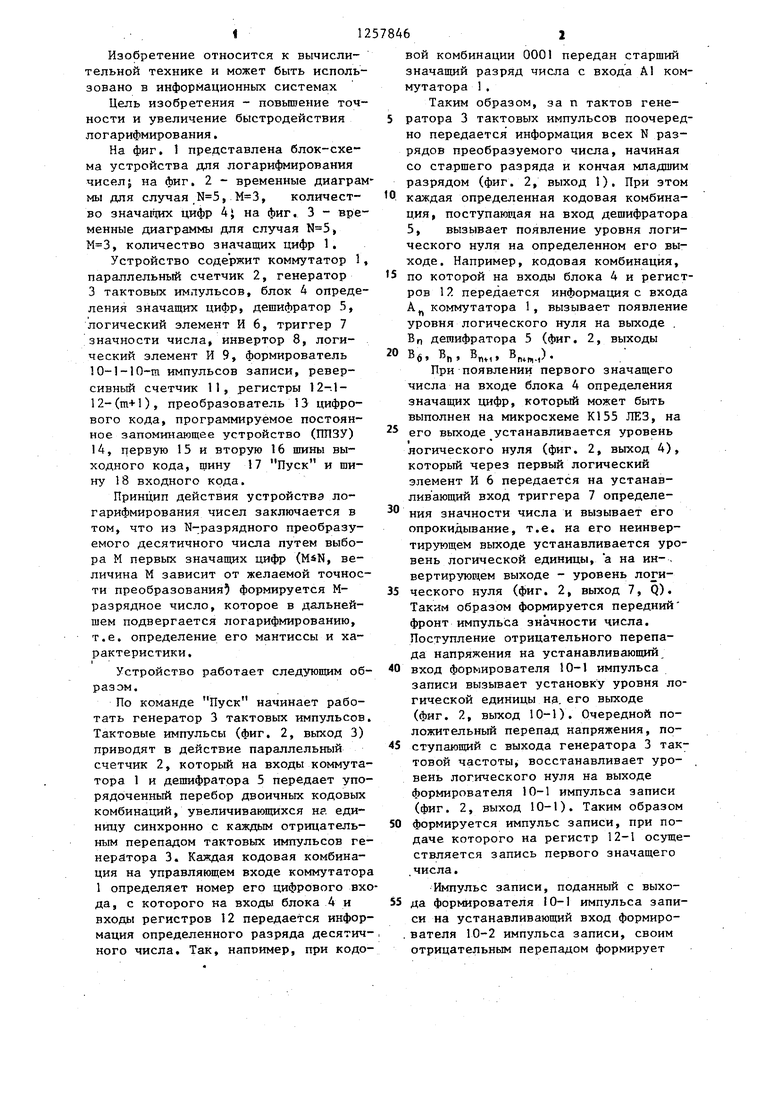

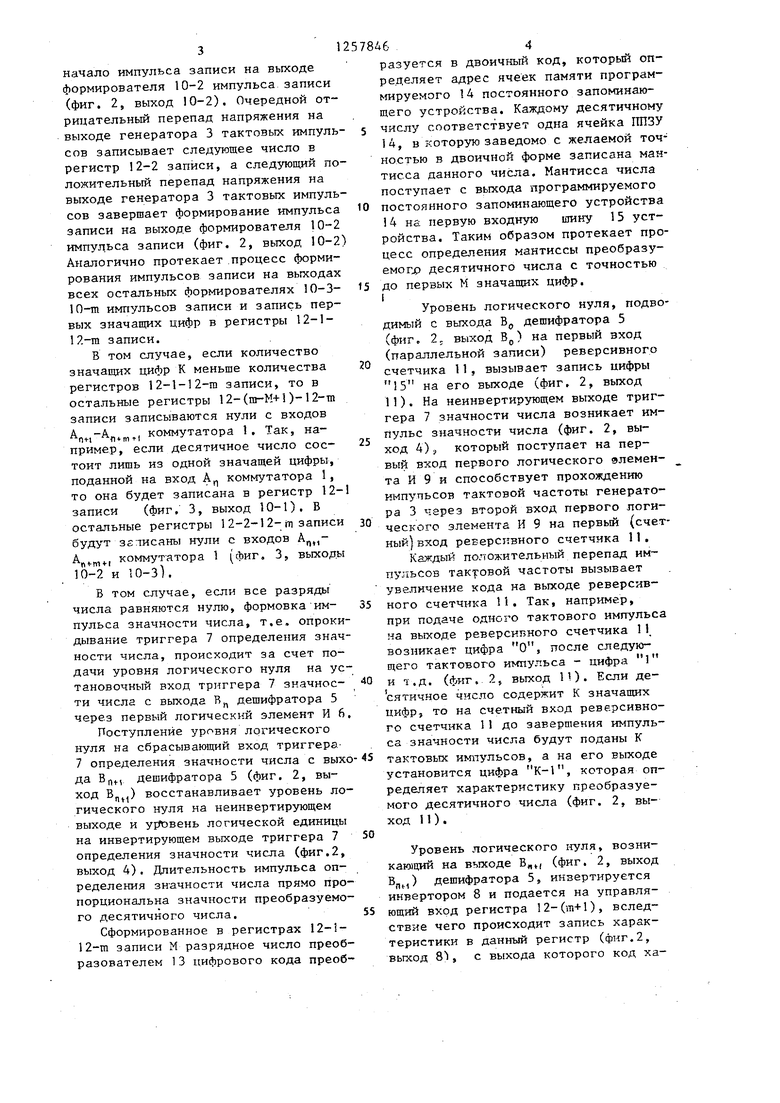

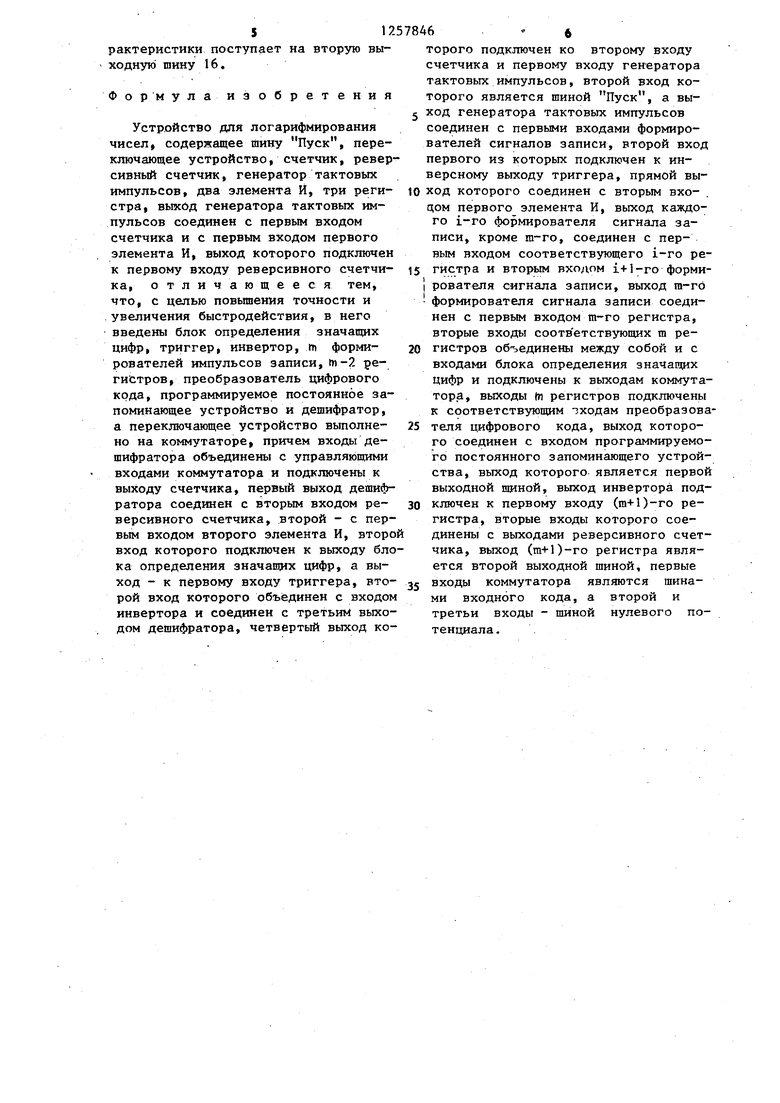

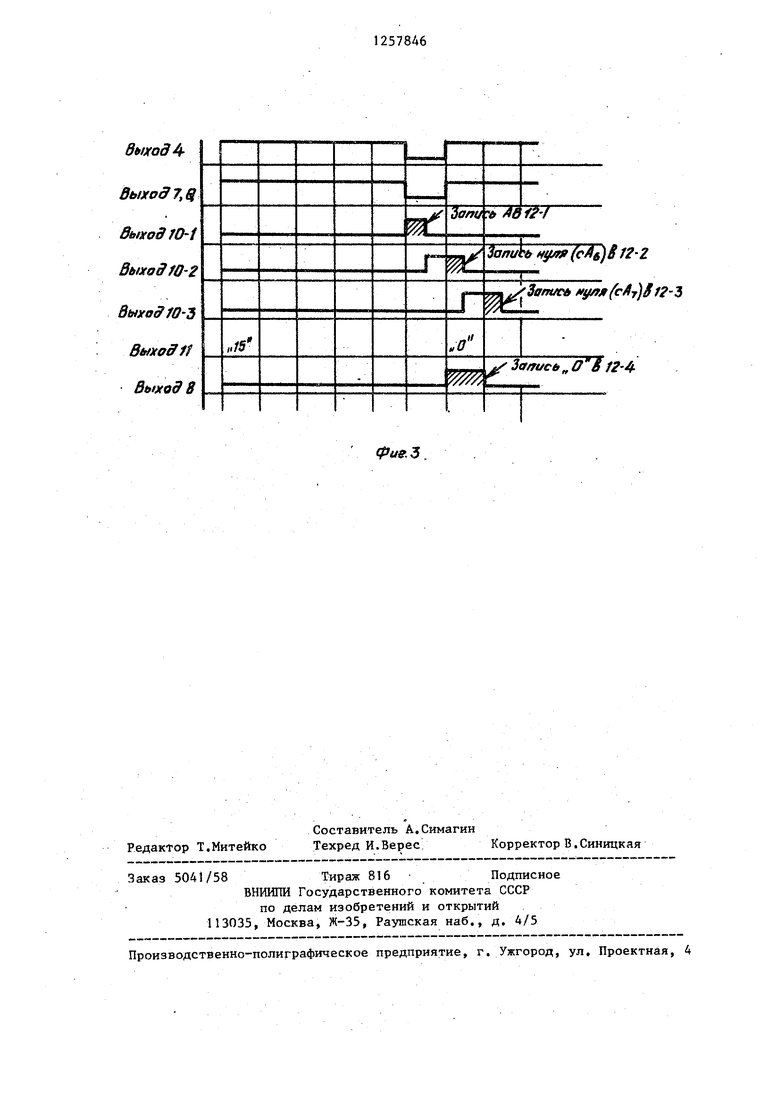

На фиг. 1 представлена блок-схема устройства для логарифмирования чиселt на фиг, 2 - временные диаграммы для случая , , количест- во значащих цифр 4j на фиг. 3 - временные диаграммы для случая , количество значащих цифр 1.

Устройство содержит коммутатор 1 параллельный счетчик 2, генератор 3 тактовых импульсов, блок 4 определения значащих цифр, дешифратор 5, логический элемент И 6, триггер 7 значности числа, инвертор 8, логический элемент И 9, формирователь IO-1-lO-m импульсов записи, реверсивный счетчик 11, регистры 12-.1- 12-(т+1), преобразователь 1Э цифрового кода, программируемое постоянное запоминающее устройство (ПИЗУ) 14, первую 15 и вторую 16 шины выходного кода, шину 17 Пуск и шину 18 входного кода.

Принцип действия устройства логарифмирования чисел заключается в

том, что из N-разрядного преобразуемого десятичного числа путем выбора М первых значащих цифр (, величина М зависит от желаемой точности преобразования формируется М- разрядное число, которое в дальнейшем подвергается логарифмированию, т.е. определение его мантиссы и характеристики.

Устройство работает следующим образом.

По команде Пуск начинает работать генератор 3 тактовых импульсов. Тактовые импульсы (фиг, 2, выход 3) приводят в действие параллельный счетчик 2, который на входы коммутатора 1 и дешифратора 5 передает упорядоченный перебор двоичных кодовых комбинаций, увеличивающихся н. единицу синхронно с каждым отрицательным перепадом тактовых импульсов генератора 3. Каждая кодовая комбинация на управляющем входе коммутатора 1 определяет номер его цифрового входа, с которого на входы блока А и входы регистров 12 передается информация определенного разряда десятичного числа. Так, например, при кодо

.

5 0

5

0

вой комбинации 0001 передан старший значащий разряд числа с входа А1 коммутатора 1 .

Таким образом, за п тактов генератора 3 тактовых импульсов поочередно передается информация всех N разрядов преобразуемого числа, начиная со старшего разряда и кончая младшим разрядом (фиг. 2, выход 1), При этом каждая определенная кодовая комбинация, поступаюгцая на вход дешифратора 5, вызывает появление уровня логического нуля на определенном его выходе. Например, кодовая комбинация, по которой на входы блока 4 и регистров 12 передается информация с входа А коммутатора 1, вызывает появление уровня логического нуля на выходе . Вр дешифратора 5 (фиг, 2, выходы

6 Bnti ,-)

При появлении первого значащего числа на входе блока 4 определения значащих цифр, который может быть выполнен на ьткросхеме К155 ЛЕЗ, на его выходе устанавливается уровень логического нуля (фиг, 2, выход 4), который через первый логический элемент И 6 передается на устанавливающий вход триггера 7 определения значности числа и вызывает его опрокидывание, т.е, на его неинвертирующем выходе устанавливается уровень логической единицы, а на ин- , вертирующем выходе - уровень логи5 ческого нуля (фиг, 2, выход 7, Q), Таким образом формируется передний фронт импульса значности числа. Поступление отрицательного перепада напряжения на устанавливающий

0 вход формирователя 10-1 импульса записи вызывает установку уровня логической единицы на. его выходе (фиг. 2, выход 10-1), Очередной положительный перепад напряжения, по5 ступаюшзий с выхода генератора 3 тактовой частоты, восстанавливает уровень логического нуля на выходе формирователя 10-1 импульса записи (фиг, 2, выход 10-1). Таким образом

0 формируется импульс записи, при подаче которого на регистр 12-1 осуществляется запись первого значащего .числа,

Импульс записи, поданный с выхо5 да формирователя 10-1 импульса записи на устанавливающий вход формнро- . вателя 10-2 импульса записи, своим отрицательньт перепадом формирует

3

начало импульса записи на выходе формирователя 10-2 импульса записи (фиг. 2, выход 10-2). Очередной отрицательный перепад напряжения на выходе генератора 3 тактовых импульсов записывает следующее число в регистр 12-2 записи, а следующий положительный перепад напряжения на выходе генератора 3 тактовых импульсов завершает формирование импульса записи на выходе формирователя 10-2 импудьса записи (фиг. 2, выход, 10-2 Аналогично протекает процесс формирования импульсов записи на выходах всех остальных формирователях 10-3- 10-т импульсов записи и запись первых значащих цифр в регистры 12-1- 1 .-т записи.

В том случае, если количество значащих цифр К меньще количества регистров 12-1-12-т записи, то в остальные регистры 12-(m-M-)-i )-12-тп записи записываются нули с входов коммутатора 1. Так, например, если десятичное число состоит лишь из одной значащей цифры, поданной на вход А коммутатора 1, то она будет записана в регистр 12записи (фиг. 3, выход 10-1). В остальные регистры 12-2-12-m записи будут 3 ли саны нули с входов А,Ч«-т -| коммутатора 1 (фиг, 3, выходы 10-2 и 10-3.

Б том случае, если все разряды числа равняются нулю, формовка импульса значности числа, т.е. опрокидывание триггера 7 определения значности числа, происходит за счет подачи уровня логического нуля на установочный вход триггера 7 значности числа с выхода В дешифратора 5 через первый логический элемент И 6.

Поступление уровня логического нуля на сбрасывающий вход триггера- 7 определения значности числа с выхода БП, дешифратора 5 (фиг. 2, выход В„) восстанавливает уровень логического нуля на неинвертирующем выходе и угйэвень логической единицы на инвертирующем выходе триггера 7 определения значности числа (фиг.2, выход 4). Длительность импульса определения зн-ачности числа прямо пропорциональна значности преобразуемого десятичного числа.

Сформированное в регистрах 12-т записи М разрядное число преобразователем 13 цифрового кода преоб578464

разуется в двоичный код, который определяет адрес ячеек памяти программируемого 14 постоянного запоминающего устройства. Каждому десятичному 5 числу соответствует одна ячейка ППЗУ 14, в которую заведомо с желаемой точностью в двоичной форме записана мантисса данного числа. Мантисса числа поступает с выхода программируемого 10 постоянного запоминающего устройства 14 на первую входную шину 15 устройства. Таким образом протекает процесс определения мантиссы преобразу- eMorjp десятичного числа с точностью 15 до первых М значащих цифр. I

Уровень логического нуля, подводимый с выхода В дешифратора 5 (фиг. 2; выход Вр) на первый вход (параллельной записи) реверсивного счетчика 11, вызывает запись цифры 15 на его выходе (фиг. 2, выход 11). На неинвертирующем выходе триггера 7 значности числа возникает импульс значности числа (фиг. 2, выход 4)J который поступает на первый вход первого логического элемента И 9 и способствует прохождению импульсов тактовой частоты генератора 3 через второй вход первого логи- ° ческого элемента И 9 на первый (счетный) вход реверсивного счетчика 11,

Каждьш положительный перепад импульсов тактовой частоты вызывает увеличение кода на выходе реверсив- 5 ного счетчика П. Так, например,

при подаче одного тактового импульса на выходе реверсивного счетчика 1 1. возникает цифра О, после следующего тактового импульса - цифра 1 0 и 1.д. (фиг. 25 выход 11). Если десятичное число содержит К значащих цифр, то на счетный вход реверсивного счетчика 11 до завершения импульса значности числа будут поданы К

25

тактовых импульсов, а на его выходе установится цифра К-1, которая определяет характеристику преобразуемого десятичного числа (фиг. 2, выход П ).

Уровень логического нуля, возни- какицкй на выходе В„к (фиг. 2, выход В.,,) дешифратора 5, инвертируется инвертором 8 и подается на управля- ющий вход регистра 12-(п1+1), вследствие чего происходит запись характеристики в данный регистр (фиг.2, выход 81, с выхода которого код характеристики поступает на вторую выходную шину 16.

Формулаиэобретения

Устройство для логарифмирования чисел, содержащее шину Пуск, переключающее устройство, счетчик, реверсивный счетчик, генератор тактовых импульсов, два элемента И, три регистра, выход генератора тактовых импульсов соединен с первым входом счетчика и с первым входом первого элемента И, выход которого подключен к первому входу реверсивного счетчика, отличающееся тем, что, с целью повышения точности и увеличения быстродействия, в него введены блок определения значащих цифр, триггер, инвертор, m формирователей импульсов записи, т-2 ре- гиЬтров, преобразователь цифрового кода, программируемое постоянное запоминающее устройство и дешифратор, а переключающее устройство выполнено на коммутаторе, причем входы дешифратора объединены с управляющими входами коммутатора и подключены к выходу счетчика, первый выход дешифратора соединен с вторым входом реверсивного счетчика, второй - с первым входом второго элемента И, второ вход которого подключен к выходу блока определения значащих цифр, а выход - к первому входу триггера, второй вход которого объединен с входом инвертора и соединен с третьим выходом дешифратора, четвертый выход которого подключен ко второму входу счетчика и первому входу генератора тактовых импульсов, второй вход которого является шиной Пуск, а вы- 5 ход генератора тактовых импульсов соединен с первыми входами формирователей сигналов записи, второй вход первого из которых подключен к инверсному выходу триггера, прямой вы- 10 ход которого соединен с вторым вхо- Чом первого элемента И, выход каждого i-ro формирователя сигнала записи, кроме т-го, соединен с первым входом соответствующего i-ro ре- tS гистра и вторым входом i+1-го форми- I рователя сигнала записи, выход га-го формирователя сигнала записи соединен с первым входом т-го регистра, вторые входы соотв етствующих m ре- 20 гистров об ьединены между собой и с входами блока определения значащих ЦИФР и подключены к выходам коммутатора, выходы (п регистров подключены к соответствующим входам преобразова 25 теля цифрового кода, выход которого соединен с входом программируемого постоянного запоминающего устройства, выход которого является первой выходной шиной, выход инвертора под- 30 ключей к первому входу (т+1)-го регистра, вторые входы которого соединены с выходами реверсивного счетчика, выход (т+1)-го регистра является второй выходной шиной, первые 35 входы коммутатора являются шинами входного кода, а второй и третьи входы - шиной нулевого потенциала.

/t-lЛ-N

ВыжоЗЪ Buxoffi

ВыжоЗ Be ВыхоЗвп. BS

OMtSftTti ffs

8tue3Bntm-tj

Of

вмиоЗ BbuoS 7, f

Выход 10-1 Выход 10-2 ВыжодЮ-Ъ

Bbfjrod 11 fftoeodS

Выходу Выход7,Щ

Выход rO-i BbixofffO-2

BiHxoSW-Ъ

Выходи

Выход 8

Редактор Т.Митейко

Составитель А.Симагин

Техред И.Верес Корректор В.Синицкая

Заказ 5041/58 Тираж 816 Подписиое ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

фие. 3.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для индикации | 1989 |

|

SU1667150A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Устройство для преобразования чисел из формы с фиксированной запятой в форму с плавающей запятой | 1982 |

|

SU1022148A1 |

| Устройство для деления чисел в форме с плавающей запятой | 1988 |

|

SU1566340A1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Преобразователь частоты в код | 1985 |

|

SU1356207A1 |

| Устройство для преобразования двоичного кода в десятичный и обратно для чисел с плавающей запятой | 1977 |

|

SU717755A1 |

| Устройство для ввода и вывода информации | 1985 |

|

SU1265755A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1981 |

|

SU1013942A1 |

| Устройство для сложения и вычитания чисел с плавающей запятой | 1980 |

|

SU959070A1 |

Изобретение относится к вычислительной технике и позволяет повысить точность и увеличить быстродействие логарифмирования за счет того, что значения логарифмов берутся из программируемого постоянного запоминающего устройства, а не являются результатом приблизительных расчетов, и за счет того, что количество необходимых операций в данном устройстве значительно меньше, чем в известных. По команде Пуск на входы блока определения значащих цифр (БОЗЦ) послтедователь- но поступают коды разрядов десятичного числа. В БОЗЦ определяется момент поступления первой значащей цифры (отличной от нуля), которая записывается в первый регистр. Информация о коде в остальных р азря- дах записывается в остальные т-1 регистров. Затем десятичный код числа преобразуется в двоичный в преобразователе цифрового кода и поступает на вход программируемого постоянного запоминающего устройства, на вьпсоде которого образуется мантисса преобразуемого числа. Характеристика преобразуемого числа формируется на выходе реверсивного счетчика в соответствии с сигналами на выходах БОЗЦ и триггера, которые пропорциональны количеству значащих цифр в преобразуемом числе. 3 ил. с б С го сд 00 4i О)

| Цифровое устройство для логарифми-РОВАНия дВОичНыХ чиСЕл | 1979 |

|

SU813414A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для логарифмирования двоичных чисел | 1978 |

|

SU767755A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-09-15—Публикация

1984-04-11—Подача